# iSBC 544 INTELLIGENT COMMUNICATIONS CONTROLLER

iSBC Communication Controller acting as a single board communications computer or an intelligent slave for communications expansion.

On Board Dedicated 8085A Microprocessor providing communications control and buffer management for four programmable Synchronous/Asynchronous Channels. Sockets for up to 8K bytes of read only memory.

16K-bytes of dual port dynamic read/write memory with on-board refresh.

Extended Multibus addressing permits iSBC 544 board partitioning into 16K byte segments in a 1-megabyte address space.

Ten programmable parallel I/O lines compatible with Bell 801 Automatic Calling Unit.

12 levels of programmable interrupt control.

Individual software programmable baud rate generation for each serial I/O channel.

Three independent programmable interval timer/counters.

Interface control for auto answer and auto originate modem.

The iSBC 544 Intelligent Communications Controller is a member of Intel's family of single-board computers, memory, I/O, and peripheral controller boards. The iSBC 544 board is a complete communications controller on a single 6.75 × 12.00 inch printed circuit card. The on-board 8085A CPU may perform local communications processing by directly interfacing with on-board read/write memory, nonvolatile read only memory, four synchronous/asynchronous serial I/O ports, RS366 compatible parallel I/O, programmable timers, and programmable interrupts.

# **FUNCTIONAL DESCRIPTION**

# Intelligent Communications Controller

Two Mode Operation - The iSBC 544 board is capable of operating in one of two modes: 1) as a single board communications computer with all computer and communications interface hardware on a single board; 2) as an "intelligent bus slave" that can perform communications related tasks as a peripheral processor to one or more bus masters. The iSBC 544 may be configured to operate as a stand-alone single board communications computer with all MPU, memory and I/O elements on a single board. In this mode of operation, the iSBC 544 may also interface with expansion memory and I/O boards (but no additional bus masters). The iSBC 544 performs as an intelligent slave to the bus master by performing all communications related tasks. Complete synchronous and asynchronous I/O and data management are controlled by the on-board 8085A CPU to coordinate up to four serial channels. Using the iSBC 544 as an intelligent slave, multichannel serial transfers can be managed entirely on-board, freeing the bus master to perform other system functions.

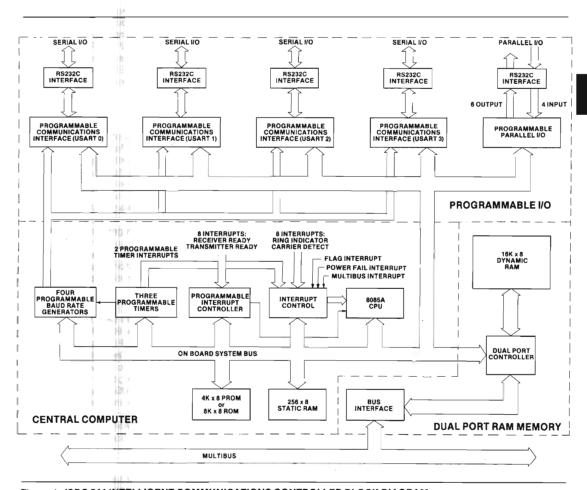

Architecture — The iSBC 544 board is functionally partitioned into three major sections: I/O, central computer, and shared dual port RAM memory (Figure 1). The I/O hardware is centered around the four Intel 8251A USART devices providing fully programmable serial interfacing. Included here as well is a 10-bit parallel interface compatible with the Bell 801 automatic calling unit, or equivalent. The I/O is under full control of the on-board CPU and is protected from access by system bus masters. The second major segment of the intelligent communications controller is a central computer, with an 8085A CPU providing powerful processing capability. The 8085A together with on-board EPROM / ROM, static RAM, programmable timers/counters, and program-

Figure 1. iSBC 544 INTELLIGENT COMMUNICATIONS CONTROLLER BLOCK DIAGRAM

Central Processing Unit

mable interrupt control provide the intelligence to manage sophisticated communications operations on-board the iSBC 544 board. The timer/counters and interrupt control are also common to the I/O area providing programmable baud rates to the USARTs and prioritizing interrupts generated from the USARTs. The central computer functions are protected for access only by the onboard 8085A. Likewise, the on-board 8085A may not gain access to the system bus when being used as an intelligent slave. When the iSBC 544 is used as a bus master, the on-board 8085A CPU controls complete system operation accessing on-board functions as well as memory and I/O expansion. The third major segment, dual port RAM memory, is the key link between the iSBC 544 intelligent slave and bus masters managing the system functions. The dual port concept allows a common block of dynamic memory to be accessed by the on-board 8085A CPU and off-board bus masters. The system program can, therefore, utilize the shared dual port RAM to pass command and status information between the bus masters and on-board CPU. In addition, the dual port concept permits blocks of data transmitted or received to accumulate in the on-board shared RAM, minimizing the need for a dedicated memory board.

on a single LSI chip, is the central processor for the iSBC 544. The 8085A CPU is directly software compatible with the Intel 8080A CPU. The 8085A contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs, providing both single and double precision operators. The minimum instruction execution time is 1.45 microseconds. The 8085A CPU has a 16-bit program counter. An external stack, located within any portion of iSBC 544 read/write memory, may be used as a last-in/first-out storage area for the contents of the program counter, flags, accumulator, and all of the six general purpose registers. A 16-bit stack pointer controls the addressing of this external stack. This stack provides subroutine nesting bounded only by memory size.

Intel's powerful 8-bit n-channel 8085A CPU, fabricated

# Serial I/O

# EPROM/ROM Capacity

Four programmable communications interfaces using Intel's 8251A Universal Synchronous/Asynchronous Receiver/Transmitter (USART) are contained on the board and controlled by the on-board CPU in combination with the on-board interval timer/counters to provide all common communication frequencies. Each USART can be programmed by the system software to individually select the desired asynchronous or synchronous serial data transmission technique (including IBM Bi. Sync.). The mode of operation (i.e., synchronous or asynchronous), data format, control character format, parity, and baud rate are all under program control. Each 8251A provides full duplex, double-buffered, transmit and receive capability. Parity, overrun, and framing error detection are all incorporated in each USART. Each channel is fully buffered to provide a direct interface to RS232C compatible terminals, peripherals, or synchronous/asynchronous modems. Each channel of RS232C command lines, serial data lines, and signal ground lines are brought out to 26-pin edge connectors that mate with RS232C flat or round cable. An optional iSBC 530 teletypewriter adapter provides an optically isolated interface for those systems requiring a 20mA current loop.

Sockets for up to 8K bytes of nonvolatile read only memory are provided on the iSBC 544 board. Read only memory may be added in 2K-byte increments up to a maximum of 4K bytes using Intel 2716 EPROMs or Intel 2316E masked ROMS; or in 4K-byte increments up to 8K bytes maximum using Intel 2732 EPROMs. All on-board EPROM/ROM operations are performed at maximum processor speed.

# Parallel I/O Port

# RAM Capacity

The iSBC 544 provides a 10-bit parallel I/O interface controlled by an Intel \$155 Programmable Interface (PPI) chip. The parallel I/O port is directly compatible with an Automatic Calling Unit (ACU) such as the Bell Model 801, or equivalent, and can also be used for auxiliary functions. All signals are RS232C compatible, and the interface cable signal assignments meet RS366 specifications. For systems not requiring an ACU interface, the parallel I/O port can be used for any general purpose interface requiring RS232C compatibility.

The iSBC 544 contains 16K bytes of dynamic read/write memory using Intel 2117 RAMs. Power for the on-board RAM may be provided on an auxiliary power bus, and memory protect logic is included for RAM battery back-up requirements. The iSBC 544 contains a dual port controller, which provides dual port capability for the on-board RAM memory. RAM accesses may occur from either the on-board 8085A CPU or from another bus master, when used as an intelligent slave. Since on-board RAM accesses do not require the MULTIBUS, the bus is available for concurrent bus master use. Dynamic RAM refresh is accomplished automatically by the iSBC 544 for accesses originating from either the CPU or from the MULTIBUS.

Addressing — On board RAM, as seen by the on-board 8085A CPU, resides at address 8000-BFFF. On board RAM, as seen by an off-board CPU, may be placed on any 4K-byte address boundary. The iSBC 544 provides extended addressing jumpers to allow the on-board RAM to reside within a one megabyte address space when accessed via the MULTIBUS. In addition, jumper options are provided which allow the user to protect 8K-or 12K-bytes of on-board RAM for use by the on-board 8085 CPU only. This reserved RAM space is not accessible via the MULTIBUS and does not occupy any system address space.

Static RAM — The iSBC 544 board also has 256 bytes of static RAM located on the Intel 8155 PPI. This memory is only accessible to the on-board 8085A CPU and is located address 7F00<sub>H</sub>-7FFF<sub>H</sub>.

# **Programmable Timers**

The iSBC 544 board provides seven fully programmable and independent interval timer/counters utilizing two Intel 8253 Programmable Interval Timers (PIT), and the Intel 8155. The two Intel 8253 PITs provide six Independent BCD or binary 16-bit interval timer/counters and the 8155 provides one 14-bit binary timer/counter. Four of the PIT timers (BDGO-3) are dedicated to the USARTs providing fully independent programmable baud rates.

Three General Use Timers — The fifth timer (BDG4) may be used as an auxiliary baud rate to any of the four USARTs or may alternatively be cascaded with timer six to provide extended interrupt intervals. The sixth PIT timer/counter (TINT1) can be used to generate interrupt intervals to the on-board 8085A. In addition to the timer/counters on the 8253 PITs, the iSBC 544 has a 14-bit timer available on the 8155 PPI providing a third general use timer/counter (TINT0). This timer output is jumper selectable to the interrupt structure of the on-board 8085A CPU to provide additional timer/counter capability.

Timer Functions — In utilizing the iSBC 544 board, the systems designer simply configures, via software, each timer independently to meet systems requirements. Whenever a given baud rate or interrupt interval is needed, software commands to the programmable timers select the desired function. The on-board PIT together with the 8155 provide a total of seven timer/counters and six operating modes. Mode 3 of the 8253 is the primary operating mode of the four dedicated USART baud rate generators. The timer/counters and useful modes of operation for the general use timer/counters are shown in Table 1.

# Interrupt Capability

The iSBC 544 board provides interrupt service for up to 21 interrupt sources. Any of the 21 sources may interrupt the intelligent controller, and all are brought through the interrupt logic to 12 interrupt levels. Four interrupt levels are handled directly by the interrupt processing capability of the 8085A CPU and eight levels are serviced from an Intel 8259 Programmable Interrupt Controller (PIC) routing an interrupt request output to the INTR input of the 8085A (see Table 2).

Interrupt Sources — The 21 interrupt sources originate from both on-board communications functions and the Multibus. Two interrupts are routed from each of the four USARTs (8 Interrupts total) to indicate that the transmitter and receiver are ready to move a data byte to or from the on-board CPU. The PIC is dedicated to accepting these 8 interrupts to optimize USART service request. One of eight interrupt request lines are jumper selectable for direct interface from a bus master via the system bus. Two auxiliary timers (TINT0 from 8155 and TINT1 from 8253) are jumper selectable to provide general purpose counter/timer interrupts. A jumper selectable Flag Interrupt is generated to allow any bus master to interrupt the iSBC 544 by writing into the base address of the shared dual port memory accessable to the system. The Flag Interrupt is then cleared by the iSBC 544 when the on-board processor reads the base address. This interrupt provides an interrupt link between

| Function                                    | Operation                                                                                                                                                                                             | Counter                        |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Interrupt on<br>Terminal Count<br>(Mode 0)  | When terminal count is reached, an inter- rupt request is gener- ated. This function is useful for generation of real-time clocks.                                                                    | 8253<br>TINT1                  |

| Rate Generator<br>(Mode 2)                  | Divide by N counter. The output will go low for one input clock cycle and high for N-1 input clock periods.                                                                                           | <b>8253</b><br>BDG4 *          |

| Square-Wave<br>Rate Generator<br>(Mode 3)   | Output will remain high until one-half the TC has been completed, and go low for the other half of the count. This is the primary operating mode used for generating Baud rate clocked to the USARTs. | 8253<br>BDGO-4<br>TINT1        |

| Software<br>Triggered<br>Strobe<br>(Mode 4) | When the TC is loaded,<br>the counter will begin.<br>On TC the output will<br>goe low for one input<br>clock period.                                                                                  | <b>8253</b><br>BDG4 *<br>TINT1 |

| Single Pulse                                | Single pulse when TC reached.                                                                                                                                                                         | <b>8155</b><br>TINTO           |

| Repetitive<br>Single Pulse                  | Repetitive single pulse<br>each time TC is<br>reached until a new<br>command is loaded.                                                                                                               | <b>8155</b><br>TINTO           |

# **Table 1. Programmable Timer Functions**

BDG4 is jumper selectable as an auxiliary baud rate generator to the USARTs or as a cascaded output to TINT1. BDG4 may be used in modes 2 and 4 only when configured as a cascaded output.

| Interrupt<br>Source                                                           |         | Vector<br>Location | interrupt<br>Level |

|-------------------------------------------------------------------------------|---------|--------------------|--------------------|

| Power Fall                                                                    | TRAP    | <sup>24</sup> H    | 1                  |

| 8253 TINT1<br>8255 TINT0                                                      | RST 7.5 | 3CH                | 2                  |

| Ring Indicator (1)<br>Carrier Detect                                          | RST 6.5 | <sup>34</sup> H    | 3                  |

| Flag Interrupt<br>INT0/-INT7/ (1 of 8)                                        | RST 5.5 | <sup>34</sup> H    | 4                  |

| RXRDY0<br>TXRDY0<br>RXRDY1<br>TXRDY1<br>RXRDY 2<br>TXRDY2<br>RXRDY3<br>TXRDY3 | INTR    | Program-<br>mable  | 5-12               |

#### **Table 2. Interrupt Vector Memory Locations**

Four ring indicator interrupts and four carrier detect interrupts are summed to the RST 6.5 input. The 8155 may be interrogated to inspect any one of the eight signals. a bus master and intelligent slave (See System Programming). Eight inputs from the serial ports are monitored to detect a ring indicator and carrier detect from each of the four channels. These eight interrupt sources are summed to a single interrupt level of the 8085A CPU. If one of these eight interrupts occur, the 8155 PPI can then be interrogated to determine which port caused the interrupt. Finally, a jumper selectable Power Fail Interrupt is available from the Multibus to detect a power down condition.

8085 Interrupt — Thirteen of the twenty-one interrupt sources are available directly to four interrupt inputs of the on-board 8085A CPU. Requests routed to the 8085A interrupt inputs, TRAP, RST 7.5, RST 6.5 and RST 5.5 have a unique vector memory address. An 8085A jump instruction at each of these addresses then provides software linkage to interrupt service routines located independently anywhere in the Memory. All interrupt inputs with the exception of the TRAP may be masked via software.

8259 Interrupts 4 Eight interrupt sources signaling transmitter and receiver ready from the four USARTs are channeled directly to the Intel 8259 PIC. The PIC then provides vectoring for the next eight interrupt levels. Operating mode and priority assignments may be reconfigured dynamically via software at any time during system operation. The PIC accepts transmitter and receiver interrupts from the four USARTs. It then determines which of the incoming requests is of highest priority, determines whether this request is of higher priority than the level currently being serviced, and, if appropriate, issues an interrupt to the CPU. The output of the PIC is applied directly to the INTR input of the 8085A. Any combination of interrupt levels may be masked, via software, by storing a single byte in the interrupt mask register of the PIC. When the 8085A responds to a PIC interrupt, the PIC will generate a CALL instruction for each interrupt level. These addresses are equally spaced at intervals of 4 or 8 (software selectable) bytes. Interrupt response to the PiC is software programmable to a 32- or 64-byte block of memory. Interrupt sequences may be expanded from this block with a single 8085A jump instruction at each of these addresses.

Interrupt Output — In addition, the iSBC 544 board may be jumper selected to generate an interrupt from the onboard serial output data (SOD) of the 8085A. The SOD signal may be jumpered to any one of the 8 MULTIBUS interrupt lines (INTO/-INT7/) to provide an interrupt signal directly to a bus master.

## Power-Fail Control

Control logic is also included to accept a power-fail interrupt in conjunction with the AC-low signal from the iSBC 635 Power Supply or equivalent.

#### **Expansion Capabilities**

When the iSBC 544 board is used as a single board communications controller, memory and I/O capacity may be expanded and additional functions added using Intel MULTIBUS<sup>TM</sup> compatible expansion boards. In this

mode, no other bus masters may be configured in the system. Memory may be expanded to a 65K byte capacity by adding user specified combinations of RAM boards, EPROM boards, or combination boards. Input/output capacity may be increased by adding digital I/O and analog I/O expansion boards. Furthermore, multiple iSBC 544 boards may be included in an expanded system using one iSBC 544 board as a single board communications computer and additional controllers as intelligent slaves.

# **System Programming**

In the system programming environment, the iSBC 544 board appears as an additional RAM memory module when used as an intelligent slave. The master CPU communicates with the iSBC 544 board as if it were just an extension of system memory. Because the iSBC 544 board is treated as memory by the system, the user is able to program into it a command structure which will allow the iSBC 544 board to control its own I/O and memory operation. To enhance the programming of the iSBC 544 board, the user has been given some specific tools. The tools are: 1) the flag interrupt, 2) an on-board RAM memory area that is accessible to both an offboard CPU and the on-board 8085A through which a communications path can exist, and 3) access to the bus interrupt line.

Flag Interrupt — The Flag Interrupt is generated anytime a write command is performed by an off-board CPU to the base address of the iSBC 544 board's RAM. This interrupt provides a means for the master CPU to notify the iSBC 544 board that it wishes to establish a communications sequence. In systems with more than one intelligent slave, the flag interrupt provides a unique interrupt to each slave outside the normal eight MULTIBUS interrupt lines (INTO/-INT7/).

On-Board RAM — The on-board 16K byte RAM area that is accessible to both an off-board CPU and the on-board 8085A can be located on any 4K boundary in the system. The selected base address of the iSBC 544 RAM will cause a flag interrupt when written into by an off-board CPU.

Bus Access — The third tool to improve system operation as an intelligent slave is access to the Multibus interrupt lines. The iSBC 544 board can both respond to interrupt signals from an off-board CPU, and generate an interrupt to the off-board CPU via the MULTIBUS.

#### System Development Capability

The development cycle of iSBC 544 board based products may be significantly reduced using the Intellec series microcomputer development systems. The Intellec resident macroassembler, text editor, and system monitor greatly simplify the design, development and debug of iSBC 544 system software. An optional ISIS-II diskette operating system provides a linker, object code locater, and library manager. A unique in-circuit emulator (ICE-85) option provides the capability of developing and debugging software directly on the iSBC 544 board.

# **SPECIFICATIONS**

# Serial Communications Characteristics

Synchronous - 5-8 bit characters; automatic sync

insertion; parity.

Asynchronous — 5-8 bit characters; break character

generation; 1,  $1\frac{1}{2}$ , or 2 stop bits; false start bit detection; break

character detection.

#### **Baud Rates**

| Frequency (KHz) <sup>1</sup> | Baud Rate (Hz) <sup>2</sup> |       |              |  |

|------------------------------|-----------------------------|-------|--------------|--|

| (Software Selectable)        |                             |       | Asynchronous |  |

|                              |                             | + 16  | + 64         |  |

| 307.2                        |                             | 19200 | 4800         |  |

| 153.6                        |                             | 9600  | 2400         |  |

| 76.8                         |                             | 4800  | 1200         |  |

| 55.8                         | 55800                       | 3500  | 870          |  |

| 38.4                         | 38400                       | 2400  | 600          |  |

| 19.2                         | 19200                       | 1200  | 300          |  |

| 9.6-                         | 9600                        | 600   | 150          |  |

| 4.8                          | 4800                        | 300   | 75           |  |

| 6.98                         | 6980                        |       | 110          |  |

#### Notes:

Frequency selected by I/O writes of appropriate 16-bit frequency factor to Baud Rate Register.

2) Baud rates shown here are only a sample subset of possible software programmable rates available. Any frequency from 18.75 Hz to 614.4 KHz may be generated utilizing on-board crystal oscillator and 16-bit Programmable Interval Timer (used here as a frequency divider).

#### 8085A CPU

Word Size - 8, 16 or 24 bits/instruction; 8 bits of data

Cycle Time — 1.45/usec ± .1% for fastest executable instruction; i.e. four clock cycles.

Clock Rate - 2.76 MHz ± .1%

#### **System Access Time**

Dual port memory - 740 nsec

Note: Assumes no refresh contention

#### **Memory Capacity**

On-Board ROM/PROM — 4K, or 8K bytes of user installed ROM or PROM.

On-Board Static RAM - 256 bytes on 8155.

On-Board Dynamic RAM (on-board access) — 16K bytes. Integrity maintained during power failure with user-furnished batteries (optional).

On-Board Dyanmic RAM (MULTIBUS access) — 4K, 8K, or 16K-bytes available to bus by switch selection.

# Memory Addressing

On-Board ROM/PROM — 0-0FFF (using 2716 EPROMS or 2316E ROMs); 0-1FFF (using 2732 EPROMs)

On-Board Static Ram - 256 bytes: 7F00-7FFF

On-Board Dynamic RAM (on-board access) — 16K bytes: 8000-BFFF.

On-Board Dynamic RAM (MULTIBUS access) — any 4K increment 00000-FF000 which is switch and jumper selectable. 4K- 8K- or 16K-bytes can be made available to the bus by switch selection.

# I/O Capacity

**Serial** — 4 programmable channels using four 8251A USARTs.

Parallel — 10 programmable lines available for Bell 801 ACU, or equivalent use. Two auxiliary jumper selectable signals.

# I/O Addressing

# On-Board Programmable I/O

| Port     | Data                                | Control |  |

|----------|-------------------------------------|---------|--|

| USART 0  | DO                                  | D1      |  |

| USART 1  | D2                                  | D3      |  |

| USART 2  | D4                                  | . D5    |  |

| USART 3  | D6                                  | D7 .    |  |

| 8155 PPI | E9 (Port A) EA (Port B) EB (Port C) | E8      |  |

# **Interrupts**

Addresses for 8259 Registers (Hex notation, I/O address space)

E6 Interrupt request register

E6 In-service register

E7 Mask register

E6 Command register

E7 Block address register

E6 Status (polling register)

Note: Several registers have the same physical address: Sequence of access and one data bit of the control word determines which register will respond.

**Interrupt levels** routed to the 8085 CPU automatically vector the processor to unique memory locations:

24 TRAP

3C RST 7.5

34 RST 6.5

2C RST 5.5

## **Timers**

Addresses for 8253 Registers (Hex notation, I/O address space)

#### Programmable Interrupt Timer One

| D8 | Timer 0         | BDG0 |

|----|-----------------|------|

| D9 | Timer 1         | BDG1 |

| DA | Timer 2         | BDG2 |

| DB | Control registe | er   |

# Programmable Interrupt Timer Two

| DC | Timer 0         | BDG3  |

|----|-----------------|-------|

| DD | Timer 1         | BDG4  |

| DE | Timer 2         | TINT1 |

| DF | Control registe | er    |

#### Address for 8155 Programmable Timer

E8 Control

EC Timer (MSB) TINT0

ED Timer (LSB) TINTO

Input frequencies - Jumper selectable reference 1.2288 MHz ± .1% (.814 usec period nominal) or 1.843 MHz ± .1% crystal (0.542 usec period, nominal)

#### Output Frequencies (at 1.2288 MHz)

| Function                        | Single timer/counter |           | Dual timer/counter<br>(two timers cascaded |           |

|---------------------------------|----------------------|-----------|--------------------------------------------|-----------|

|                                 | Min                  | Max       | Min                                        | Max       |

| Real-time<br>interrupt interval | 1.63 usec            | 53.3 usec | 3.26 usec                                  | 58.25 min |

| Rate Generator (frequency)      | 18.75 Hz             | 614.4 KHz | 0.00029 Hz                                 | 307.2 KHz |

#### Interfaces

Serial I/O - EIA Standard RS232C signals provided and supported:

Carrier Detect Clear to Send

Receive Data Ring Indicator

Data Set Ready Data Terminal Ready Secondary Receive Data \* Secondary Transmit Data \*

Request to Send Receive Clock

Transmit Clock Transmit Data

DTE Transmit Clock

Parallel I/O - Four inputs and eight outputs (includes two jumper selectable auxiliary outputs). All signals compatible with EIA Standard RS232C. Directly compatible with Bell Model 801 Automatic Calling Unit, or

**MULTIBUS** — Compatible with iSBC MULTIBUS.

# On-Board Addressing

All communications to the parallel and serial I/O ports. to the timers, and to the interrupt controller, are via read and write commands from the on-board 8085A CPU.

# **Auxiliary Power**

An auxiliary power bus is provided to allow separate power to RAM for systems requiring battery backup of read/write memory. Selection of this auxiliary RAM power bus is made via jumpers on the board.

# Connectors

| Interface    | Pins<br>(qty) | Centers<br>(in.) | Mating Connectors            |

|--------------|---------------|------------------|------------------------------|

| Bus          | 86            | 0.156            | Viking 3KH43/9AMK12          |

| Parallel I/O | 50            | 0.1              | 3M 3415-000 or<br>TI H312125 |

| Serial I/O   | 26            | 0.1              | 3M 3462-000 or<br>TI H312113 |

# **Memory Protect**

An active-low TTL compatible memory protect signal is brought out on the auxiliary connector which, when asserted, disables read/write access to RAM memory on the board. This input is provided for the protection of RAM contents during the system power-down sequences.

#### **Bus Drivers**

| Function | Characteristic | Sink Current (mA) |

|----------|----------------|-------------------|

| Data     | Tri-state      | 50                |

| Address  | Tri-state      | 15                |

| Commands | Tri-state      | 32                |

Note: Used as a master in the single board communications computer mode

# Physical Characteristics

Width: 30.48 cm (12.00 inches) 17.15 cm (6.75 inches) Depth: Thickness: 1.27 cm (0.50 inch) Weight: 3.97 gm (14 ounces)

#### **Electrical Characteristics**

#### DC Power Requirements

| Current Requirements               |                                    |                                       |                           |                                       |

|------------------------------------|------------------------------------|---------------------------------------|---------------------------|---------------------------------------|

| Configuration                      | V <sub>CC</sub> = +5V<br>±5% (max) | V <sub>DD</sub> = ± 12V<br>± 5% (max) |                           | V <sub>AA</sub> = - 12V<br>± 5% (max) |

| With 4K<br>EPROM<br>(using 2716)   | I <sub>CC</sub> = 3.4 max          | † <sub>DD</sub> = 350mA<br>max        | I <sub>BB</sub> = 5mA max | I <sub>AA</sub> = 200mA<br>max        |

| Without<br>EPROM                   | 3.3A max                           | 350 mA max                            | 5 mA max                  | 200 mA max                            |

| RAM only (1)                       | 390 mA max                         | 176 mA max                            | 5 mA max                  | -                                     |

| RAM <sup>(2)</sup><br>refresh only | 390 mA max                         | 20 mA max                             | 5 mA max                  |                                       |

Notes: 1. For operational RAM only, for AUX power supply rating,

2. For RAM refresh only. Used for battery backup requirements. No RAM accessed.

3. VBB is normally derived on-board from VAA, eliminating the need for a VBB supply. If it is desired to supply VBB from the bus, the current requirement is as shown.

# **Environmental Characteristics**

Operating Temperature: 0°C to 55°C (32°F to 131°F) Relative Humidity: To 90% without condensation

#### Reference Manual

9800616B - iSBC 544 Intelligent Communication Controller Board Hardware Reference Manual (NOT SUP-PLIED)

Reference manuals are shipped with each product only if designated SUPPLIED (see above). Manuals may be ordered from any Intel sales representative, distributor office or from Intel Literature Department, 3065 Bowers Avenue, Santa Clara, California 95051.

#### ORDERING INFORMATION

Part Number

Description

**iSBC 544**

Intelligent Communications

Controller

<sup>\*</sup> Optional if parallel I/O port is not used as Automatic Calling Unit.