ARTICLE REPRINT

What a rich of the grade of the property of th

# What can you do with a microprocessor?

Here is how you can take \$50 worth of microprocessor parts and control a real-world electro-mechanical system.

Robert H. Cushman, Special Features Editor

By now you are probably sick and tired of hearing all these endless, vague claims about how the microprocessor will replace all TTL and CMOS SSI and MSI circuits and make you, the digital system designer, obsolete in the process. You've had your fill of our dissertations on the architectures of these  $\mu$ P's and how they condense roomfuls of 1960-vintage computers and rackfuls of 1970-vintage mini-computers into a handful of DIP's.

You say, "Just give me one quick, simple and to-the-point example of how a microprocessor can replace TTL in the small systems I am designing—systems where the end products sell for no more than a thousand dollars or so. Tell me how I can get in the  $\mu P$  act."

We have a double-barreled answer for you: Intel's little MCS-4  $\mu$ P, and Matt Biewer of Pro-Log Corp., Monterey, Calif. Together, they are the basis for the common-sense application example that follows—where a  $\mu$ P replaces the discrete circuitry that normally operates a papertape reader.

Our choice of the MCS-4 was because it's one of the very few microprocessors whose parts are actually on distributors' shelves. (We know because we've called them.) Further, the MCS-4 is

priced so low that it can do the example for \$50, which is roughly equivalent to the cost of commercial TTL cards for tape readers. The MCS-4, of course, can do much more than the example. In the real application it comes from, this is just a minor subroutine.

We've chosen Matt Biewer because he seems to us a sort of circuit designer's  $\mu P$  "folk hero." He's already gone the route you will be going as you add microprocessors to your bag of tricks. He has self-taught himself programming and developed a no-nonsense hexadecimal-code approach that has allowed him to detour around the need to use assembler and compiler programs.

However, many  $\mu P$  systems' planners are rushing on to 8-bit machines and many  $\mu P$  software experts sharply disagree with Biewer's humble "up-from-hardware" approach. An Intel spokesman who knows Biewer personally, while admitting that Biewer gets results, argues that to follow his footsteps is to ignore a decade of software development.

Our conclusion after hearing both sides of the story is that, for the small microprocessors like the MCS-4 which are suitable for \$50 controllers, the Biewer manual approach makes sense for circuit designers first getting into  $\mu$ P's. We agree

Fig. 1—Matt Biewer, creator of the tape-reader design example, is an ex logic-circuit designer who has switched over to  $\mu P's$ . He got started with microprocessors while with a former employer, MSI-Data, by designing the MCS-4 into a portable terminal instead of the custom LSI originally considered. Hundreds of units of that product are now rolling off the production line each month. Biewer is now vice-president with Pro-Log Corp., Monterey, Calif., a small company that sells support products for  $\mu P's$ .

whole-heartedly with Biewer that it may be too much to ask a circuit designer to learn both  $\mu P$  hardware and the concepts of higher level language programming at the same time. Besides, you just can't afford that much ROM memory in a \$50 system that the programming can't be done manually, as Biewer does. But we think that it might be very wise for the designer to be learning about higher level language programming at night school while he works on the Biewer machine-level approach by day.

At this time we won't get into the argument whether Biewer is right or wrong to circumvent the niceties of the world of software. The point to be made here is that the program you see in the example was created and entered into the pROM programmer by hand, without the aid of an assembly program, by an ex-digital circuit designer like yourself.

# Practically no interface hardware

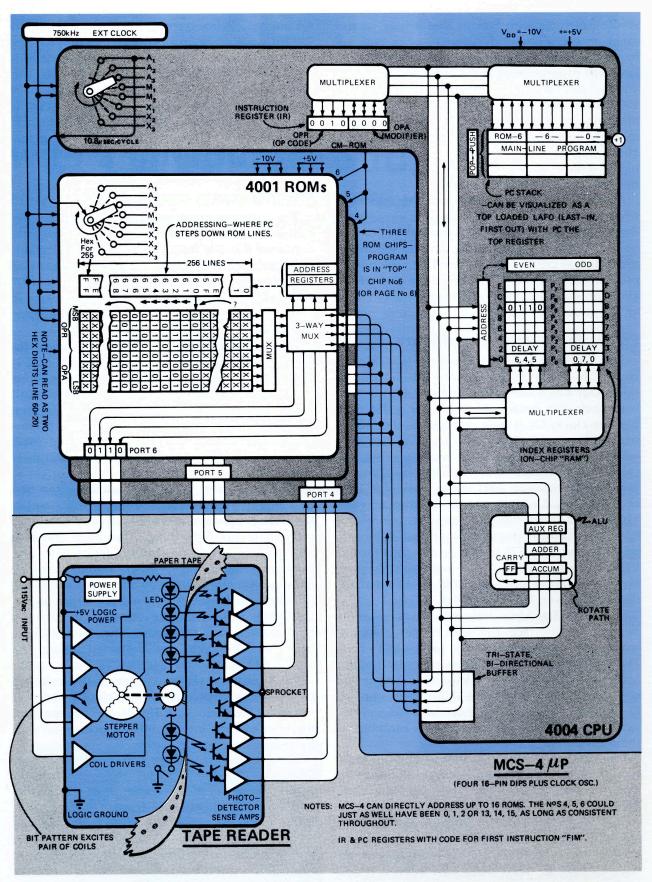

The hardware side of Biewer's tape reader control is shown in Fig. 2. The MCS-4 part is essentially just a 4004 CPU and three 4001 ROM's with their I/O ports, all driven by a 750 kHz 2-phase clock. Or at least this is what the MCS-4 part of the system would look like if the product were in high-volume production. Biewer's application is in initial moderate-volume stage, and he replaces the custom 4001 metal-masked ROM's shown in Fig. 2 with the easier-to-program Intel 1702A ROM's. He interfaces these to the MCS-4 with the 4008/4009 chips that Intel makes for this purpose and adds TTL latches and buffers for the I/O ports. But in Fig. 2, to keep our diagram simple, we show the same 4001 ROM's that we described in our last article (Ref. 5).

Note from **Fig. 2** how little external hardware is needed to interface the tape-reader stepping motor and hole sensors to the MCS-4 I/O ports. The buffer amplifiers that boost the output of the MCS-4 port 6 to the level adequate for the motor coils can be very simple. We show them as just IC Darlingtons with built-in protective diodes. They would have to be there anyway—you can't blame them on the MCS-4.

We, likewise, show the photo-transistor hole sensors as high-gain Darlington types to minimize parts count. So you can see that the only additional hardware elements to interface this typical electro-mechanical function to the existing MCS-4 system are the three I/O ports 4, 5 and 6. With the standard MCS-4 parts, this means you have to have at least three 4001 ROM's. If you look ahead to the small number of lines in the program, **Fig. 3b**, you might say your I/O requirements will force you to put in more ROM than the application needs. (Each ROM in the MCS-4

system has 256 lines, and there are only 37 lines in the software program.) However, there are many additional functions that you can implement with the spare software space in a system like this. The chances are you will find that even if your main program doesn't need the ROM space—which it most likely will—there are valuable uses for the additional ROM lines in embellishments of this tape-reading function. Don't worry, you'll think of them.

# What it takes to move tape

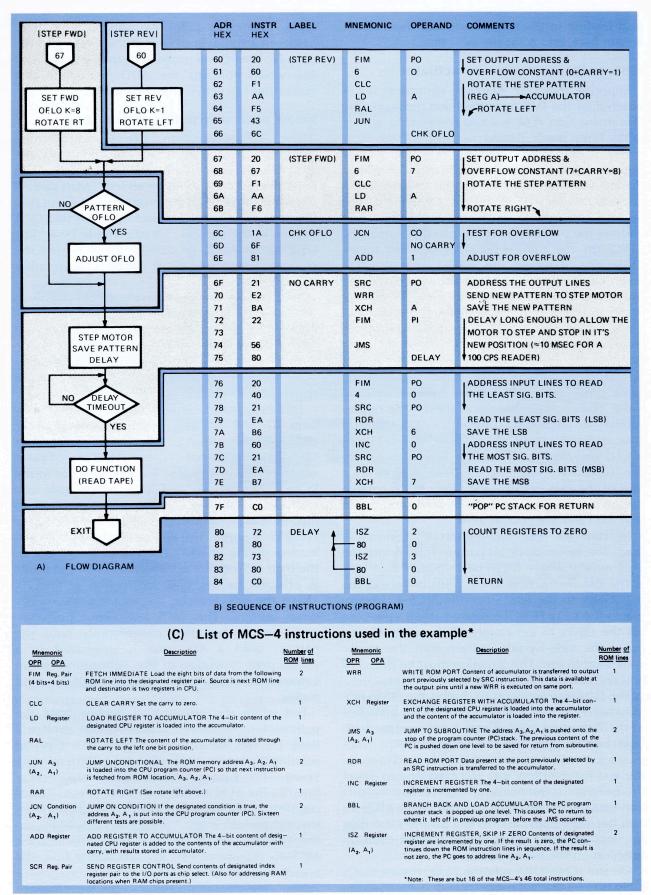

The software program, Fig. 3, has to be "the design" because you've already seen how little hardware there is from Fig. 2. The flow diagram, Fig. 3a, is the programmer's conceptual starting point in the process of "verbalizing a program," to use Matt's words. It is the skeleton which is clothed with the flesh of the instruction sequence of Fig. 3b.

This flow diagram shows two entry points for the subroutine, ROM address 67 for STEP FORWARD AND READ TAPE and ROM address 60 for STEP REVERSE AND READ TAPE. It shows one exit point, address 7F (hexadecimal) at the bottom where the BBL instruction at the end of this subroutine returns the computer to the main program. (See brief list of instructions and their explanations in box in **Fig. 3**.)

The entry points, 60 and 67, would be reached by a JMS or "jump to subroutine" at any point in the main program where it was desired to read in more data from the tape. That main-line JMS instruction would put either a 60 or 67 in the program counter (PC), which would push the previous main-line program address down in the PC stack (to be available for later return at the final BBL). This would cause the CPU to fetch the first instruction of this subroutine. (The MCS-4's basic machine cycle was explained in our last article, **Ref. 5**.)

The approximately seven parts to this software program are depicted by the blocks and diamonds of the flow chart, **Fig. 3a**. We've separated the lines of code into groups to correspond with these blocks.

The purpose of the first seven code lines is to take the two side-by-side ONEs in the 4-bit pattern that will drive the four stepper-motor coils and shift the two side-by-side ONEs right or left to rotate the motor and move the tape for the new reading position. This pattern has been stored in CPU index register A (hexadecimal 10 in decimal). It was put there after the last rotation (using the instruction at 71 as we'll see). Now it has to be brought out into the accumulator, rotated left or right according to the desired motion of the motor, and presented to the output

**Fig. 2—The hardware side of the tape reader control:** MCS-4 parts are shown at the top in much the same "classical" arrangement as they were in the preceding article (**Ref. 5**). The tape reader peripheral is shown at the bottom. As explained in the text, Biewer actually uses a 1702A electrically-

programmable, UV light-erasable pROM instead of the regular 4001 ROM that is part of the MCS-4 family. He interfaces the 1702A with the 4008 and 4009 MOS/LSI parts that Intel makes for the purpose. But he will go to this configuration, once his product reaches volume production.

Fig. 3—Software for the tape-reader control: this is what was developed to go into the MCS-4 ROM so that the  $\mu P$  would perform the control actions. He first sketched out his program graphically in the flow diagram (a) and with this to guide him,

he selected the sequence of MCS-4 instructions that implemented the flow diagram (b). A capsule explanation of the MCS-4 instructions used is given in the box (c).

port leading to the motor coils and then, again, be put back into A for the next time.

#### How software moves an actuator

Suppose the STEP REVERSE command leg is entered by the JMS from the main program. The FIM instruction at 60 is a two liner taking up two ROM lines (each having its own full machine cycle). It says register pair No. 0 (which is index register 0 and 1, if you look back to Fig. 2) will be loaded with the constant in the second lineaddress 61. The "6" in the left 4-bit side of this second line will be used shortly in step 6F to address the output port leading to the motor. The ZERO on the right 4-bit side, is a bit tricky. Ordinarily, it would not matter what this was when an I/O port was being addressed, for you only have to address down to the chip level to reach an I/O port in the MCS-4 architecture. But Biewer does not let this space go to waste. He throws the ZERO in on the right-hand side because he needs it as a constant for a later operation. "I kind of fetched two things at the same time," he explained. He believes you are more likely to stumble upon these little opportunities to pack your code efficiently if you do your coding all by hand.

CLC or "clear carry" at line 62 is a necessary precaution. The machine will be looking to see if one of the two side-by-side ONEs being rotated has spilled over into the carry FF, so it is important that the carry start out at zero.

In step 63, the "LD-register-A" instruction loads the motor-drive bit pattern from A into the accumulator where it can be shifted.

The RAL instruction, at 64, shifts or rotates the two ONEs to the left. Since the MCS-4 circuitry places the carry FF in the rotate path, it's possible for the ONEs to get caught in the carry FF and upset the side-by-side pattern that the motor coils want to see. This situation must be detected and corrected.

The JUN instruction at 65, jumps the PC to line 6C where the REVERSE and FORWARD branches of the flow chart meet. There is no need for both branches to duplicate the common steps from now on. The JCN instruction at 6C is used to make the test for overflow into the carry and to direct the program sequence to the correction instruction (at 6E) if necessary. JCN is one of the MCS-4's two decision steps, and so is a proper candidate for implementing the diamond-shaped decision function on the flow diagram.

On the JCN's OPA side the "CO" means that a jump is to be made if the carry FF = 0. Thus, as the arrow out of the left tip of the JCN diamond in the flow diagram indicates, the PC will be jumped around the next overflow correction step to 6F if

there is no carry spillover problem. But if there has been a spillover of one of the ONEs into the carry FF, the PC will proceed normally to the next line which contains the ADD instruction that makes the corrective adjustment.

## **Know your instruction definitions**

The ADD instruction, line 6E, directs the contents of register 1 to be added to the accumulator. There is a subtlety here. "You might think that a ONE should be added," Matt said. "I did when I first wrote the program. But if you stop to think about it, you'll realize there will be a ONE already in the carry FF, so you should be adding ONE minus ONE, or ZERO." (That is why the correction in rotate right at line 68 is seven rather than eight.)

Say that your bit pattern in the accumulator was 1100 which, upon shifting left, gave 1000 plus ONE in the carry. If you now add ZERO, you'll get 1001 with the ONE coming from the carry. By the way, the pattern 1001 still has the two ONEs side-by-side as far as the circle of motor coils are concerned.

This new pattern is sent out to the motor by lines 6F and 70. The SRC command at 6F addresses the output port 6. As written in proper MCS-4 coding format, it calls for the pair of index registers, No. 0 and No. 1, to be sent out to the ROM's. But, as we explained awhile ago, you really only want the "6" in register No. 0 to go out, as that is sufficient to select the ROM chip containing port 6. You will recall that the "6" was loaded during line 61. The actual movement of the pattern from the accumulator to output port 6 is effected by the WRR instruction at line 70. There the ONEs excite the motor coils via the drive buffers. The MCS-4's output ports incorporate latches that conveniently hold the pattern until a new one is generated in a subsequent execution of this subroutine, so an external actuator like the motor will be held locked.

But while the output-port latches hold the pattern for the motor, the computer itself will have no way of knowing where it left off in rotating the motor, so the new bit pattern must be saved. This is done with the XCH instruction at line 70. The XCH merely switches the contents of register A and the accumulator. You don't want the old pattern from A in the accumulator, but this XCH happens to be the only command in the MCS-4's repertoire that will move data from the accumulator to CPU index registers.

Your final operation, so far as the movement of the motor is concerned, is to introduce a delay that will allow the motor to settle to its new position before you read the data off the tape.

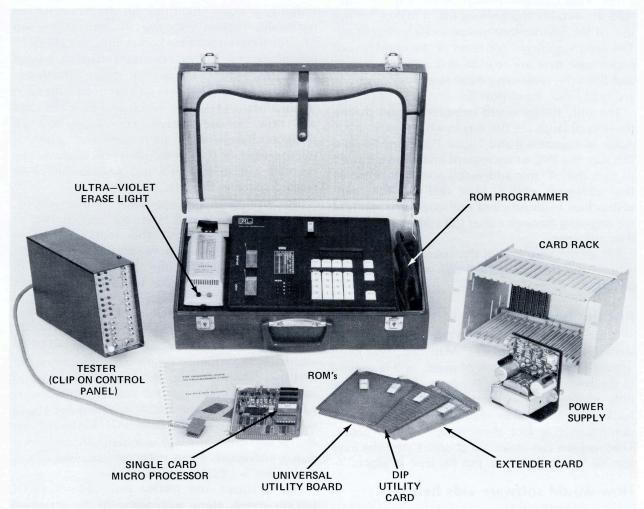

**Fig. 4—These are some of the designer aids** that Biewer has developed for approaching the MCS-4 in his up-fromhardware manner. The 1702A programmer in the middle is the

key tool. It has automatic stepping for the ROM addresses and a hexadecimal keyboard for entering the machine-language instructions.

Matt sets up a register pair (No. P<sub>1</sub>) with certain constants, and then jumps the program with a JMS to some ISZ counting instructions.

As the diamond-shaped block in the flow diagram indicates, the ISZ instruction is a decision step—the MCS-4's other one besides the JCN. This "increment-by-one-and-skip-if-zero" instruction is found in one form or other in all computers. Here it directs the CPU to keep looping back and adding ONE to the designated register (2 for the first ISZ) until the content of that register becomes ZERO, then to skip over the loop-back (line 81), and go on to the next step.

Matt must have planned to use this ISZ delay count routine more than once because he shows it as a separate subroutine at a different location (starting at line 80 in our **Fig. 3b**). This represents a

subroutine within a subroutine, or two levels of "nesting." As the nesting stack associated with the MCS-4's PC is three levels deep, this presents no problem. The BBL instruction at the end of this short subroutine automatically "pops" the stack and returns the PC to the desired point in the main subroutine—line 76.

The first ISZ can produce up to 345 μsec of delay if register 2's starting count is 0000. The second ISZ can add to this exponentially as it makes the PC keep going back all the way through the first count on each of its loops. Therefore, the total delay, if the second ISZ's register (No. 3) also starts at 0000, can be 5.8 msec. In his actual tape reader application, Matt uses a somewhat more complex arrangement variation of this to produce 10 msec delay.

# Reading in the data

The final operation—that of reading the tape data in—is fairly straightforward. It makes further use of the instructions we've already described. The least significant four bits of the eight bits of paper tape data are read in first on input port 4, and then the remaining most significant four bits are read in on input port 5.

The only things worth commenting on during these final steps are the way in which a new use is made of registers 0 and 1 (pair P<sub>0</sub>) at line 76, and the way the INC or increment instruction is used to turn the "4" that addressed port 4 into the "5" that addresses port 5. Matt said the increment instruction is an efficient one-code-line method for stepping through either I/O addresses or RAM data addresses.

BBL at the very end of the subroutine (line 7F) returns the PC to where it was in the main line program.

# Just the beginning

"Our software for the tape reader doesn't stop with this basic subroutine," Matt said. "We keep adding things as we think of them, as it is so easy to do this with software. For example, we've got a little routine that steps the motor forward and backwards and makes readings from the tape to determine if, in fact, there is tape in the reader. That way we can make our product alert the user that he has forgotten to put his tape in place."

## How would software aids help?

It is very difficult for an outsider to evaluate the various software aids. Part of the confusion comes from the way software people seem to imply that these aids help to create or "write" the program. As far as we know, no machine aid can help you select the basic sequence of instructions (like that shown on the right-hand side of Fig. 3b), any more than any machine could help the author write this article. But programmers point out that some languages are easier to "think" in. Just like some multi-linguists say they like to think in Italian rather than German, so some programmers feel they can create programs faster when they are thinking in some high-level language like FORTRAN. Once one has gone to some language that is different from what the end user understands (be it a human or a machine), then it is quite sensible to have a computer program that will automatically translate from the easy-to-use

language to the final application language.

But Biewer, being a digital circuit designer by training, "likes" to think in terms close to hardware. The MCS-4's own 46 instructions are fine for him because he knows this "vocabulary" intimately due to his constant hardware-level familiarity with this machine. Matt effortlessly visualizes which registers will be used with each instruction, and where, when and how the data will flow between them. He claims the μP designer has to have such familiarity with his microprocessor if he is to use it efficiently (as we pointed out in Biewer's use of the otherwise wasted space in line 61).

The writing of the sequence of instructions, which no machine can help you with, is 99% of the work. How about the remaining 1%translating the instructions in their mnemonic form into the ONEs and ZEROs that the µP understands? "What's the big deal here?" says Biewer. "I merely run down the instructions and write in the hexadecimal equivalents for their 4-bit code groups (see the third column from the left in **Fig. 3b**). I have already numbered the ROM addresses in sequence on my work sheet (see the first two columns in Fig. 3b). Now all I have to do is go to the ROM (pROM actually since he is talking in terms of the 1702A) programmer I have designed. It has a hexadecimal keyboard for instruction entry and will automatically sequence down addresses. I can enter all 256 lines of the typical MCS-4 ROM in 15 minutes."

Fig. 4 shows the pROM programmer he is talking about, along with some of the other µP design and prototyping aids that Biewer has evolved to make his approach easier.

#### References

- 1. "The Designers Guide to Programmed Logic (For the PLS 400 Systems)," by Matt Biewer, Pro-Log Corp., 852 Airport Rd., Monterey, CA 93940. The textbook that Biewer uses to teach his up-from-hardware approach to programming the MCS-4. It is a very useful supplement to the Intel MCS-4 manual as it provides a second viewpoint that helps the designer see how it can be programmed to perform certain widely-used common functions.

- 2. "Microprocessors are changing your future," EDN, Nov. 5, 1973, pg. 26.

- 3. "Understanding the microprocessor is no trivial task," EDN, Nov. 20, 1973, pg. 42.

- 4. "Understand the 8-bit \u03bcP: you'll see a lot of it," EDN, Jan. 20, 1974, pg. 48.

- 5. "Don't overlook the 4-bit µP: they're here and they're cheap," EDN, Feb. 20, 1974, pg. 44.

EDN MARCH 20, 1974

48