## **DEVELOPMENT SYSTEMS**

### MICROCOMPUTER DEVELOPMENT SYSTEMS

This section contains information necessary to select the appropriate Intel design aids required to facilitate microprocessor hardware and software development. Design aids cover the broad range from the Intellec<sup>®</sup> MDS system with its in-circuit emulator options for both the Intel 8080 (ICE-80) and the Series 3000 Bipolar Microcomputer (ICE-30), to the extensive User's Program Library and a selection of 3 and 4 day Microcomputer Workshops. The purpose of development aids is to shorten the design cycle and thus save time and money in the development and production of microcomputer-based products.

|                       | Туре                           | Description                               | Page No. |

|-----------------------|--------------------------------|-------------------------------------------|----------|

|                       |                                | Intellec <sup>®</sup> MDS-800             | 10-3     |

| ទ                     |                                | Diskette Operating System                 | 10-8     |

| DEVELOPMENT SYSTEMS   |                                | Universal Prom Programmer                 | 10-13    |

|                       | Intellec <sup>®</sup> MDS-800  | High Speed Paper Tape Reader              | 10-14    |

|                       |                                | In Circuit Emulator – ICE-80              | 10-15    |

|                       |                                | In Circuit Emulator – ICE-30              | 10-18    |

| JE V                  |                                | ROM Simulators                            | 10-21    |

| M                     | Intellec <sup>®</sup> 8/MOD/8  | Intellec 8/MOD 8                          | 10-23    |

| 5                     |                                | High Speed Paper Tape Reader              | 10-24    |

| ž                     | Barebones                      | Barebones 80                              | 10-25    |

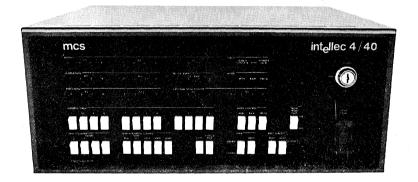

| B                     | Intellec <sup>®</sup> 4/MOD/40 | Intellec 4/MOD 40                         | 10-27    |

|                       |                                | High Speed Paper Tape Reader              | 10-28    |

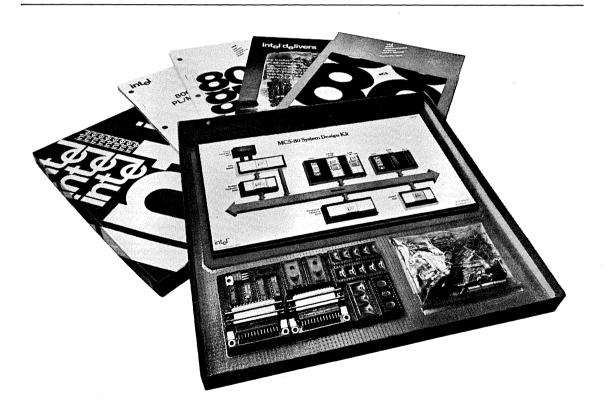

| DESIGN<br>KIT         | SDK-80                         | 8080 System Design Kit                    | 10-29    |

|                       | imm 4-42                       | Central Processor Module                  | 10-31    |

|                       | imm 4-43                       | Central Processor Module                  | 10-31    |

|                       | imm 4-60                       | Input/Output                              | 10-31    |

| ŝ                     | imm 4-22                       | Data Storage Module                       | 10-31    |

| <u> </u>              | imm 4-24                       | Data Storage Module                       | 10-31    |

| 3                     | imm 8-82                       | Central Processor Module                  | 10-32    |

| e<br>N                | imm 8-60                       | Input/Output Module (8008)                | 10-32    |

| æ                     | imm 8-61                       | Input/Output Module (8080)                | 10-32    |

| Ë                     | imm 8-62                       | Output Module (8008)                      | 10-32    |

| P                     | imm 8-63                       | Output Module (8080)                      | 10-32    |

| N                     | imm 8-82                       | Central Processor Module (8008)           | 10-32    |

| õ                     | imm 8-83                       | Central Processor Module (8080)           | 10-32    |

| MICROCOMPUTER MODULES | imm 6-26                       | PROM Memory Module                        | 10-33    |

| 10                    | imm 6-28                       | RAM Memory Module                         | 10-33    |

|                       | imm 6-70                       | Universal Prototype Module                | 10-33    |

| ÷                     | imm 6-72                       | Module Extender                           | 10-33    |

|                       | imm 6-76                       | PROM Programmer Module                    | 10-33    |

|                       | Conversion Kits                | Conversion Kits                           | 10-33    |

| OEM                   | SBC 80/10                      | OEM Computer System                       | 10-34    |

|                       | MAC 40                         | Microcomputer Software Products           | 10-36    |

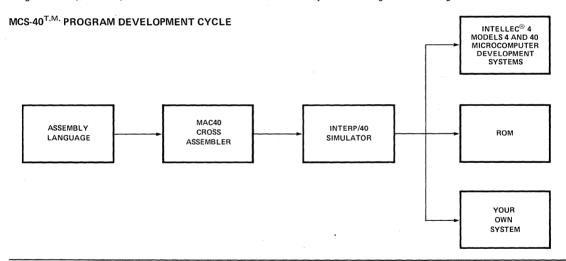

|                       |                                | MCS-40™ Cross Assembler                   | 10-37    |

|                       | INTERP 40                      | 4004/4040 Simulator                       | 10-39    |

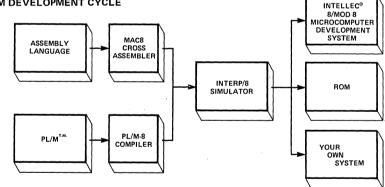

| ш                     | MAC 8                          | MCS-8™ Cross Assembler                    | 10-38    |

| SOFTWARE              | INTERP/8                       | 8008 Simulator                            | 10-40    |

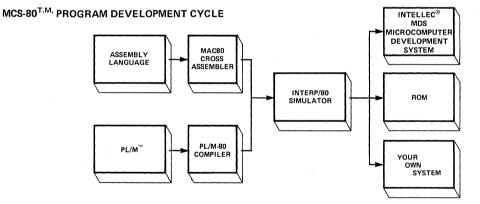

| M                     | MAC 80                         | MCS-80™ Cross Assembler                   | 10-41    |

| E                     | INTERP/80                      | 8080 Simulator                            | 10-42    |

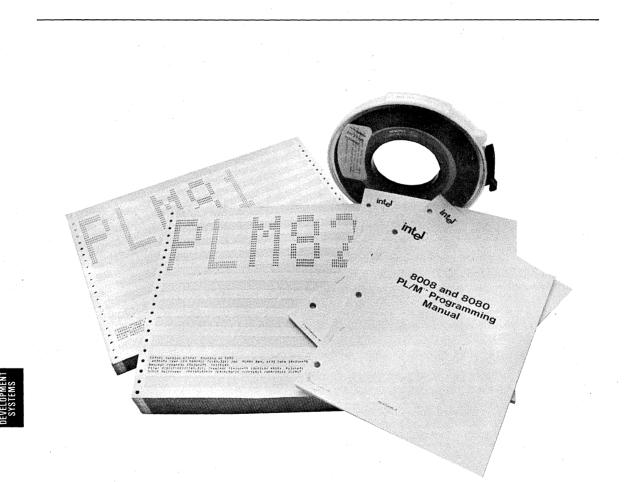

| SO                    | PL/M™                          | PL/M™ Cross Compilers for MCS-8/MCS-80    | 10-43    |

|                       | CROMIS                         | Series 3000 Cross Microprogramming System | 10-45    |

|                       |                                | User's Program Library                    | 10-46    |

|                       | User's Library                 | 4-Bit Library Index                       | 10-47    |

|                       |                                | 8-Bit Library Index                       | 10-49    |

|                       |                                | User's Library Submittal Form             | 10-57    |

|                       | Training                       | Microcomputer Training Program            | 10-59    |

# intel

### MDS-800 INTELLEC® MDS MICROCOMPUTER DEVELOPMENT SYSTEM

Modular microcomputer development system for development and implementation of MCS<sup>T.M.</sup>-80 and Series 3000 Microcomputer Systems

Intel 8080 microprocessor, with 2  $\mu$ s cycle time and 78 instructions, controls all Intellec MDS functions.

16K bytes RAM memory expandable to 64K bytes.

2K bytes ROM memory expandable to 14K bytes.

Hardware interfaces and software drivers provided for TTY, CRT, line printer, high speed paper tape reader, high speed paper tape punch, and Universal PROM Programmer.

Universal bus structure with multiprocessor and DMA capabilities.

Eight level nested, maskable, priority interrupt system.

Optional PROM programmer peripheral capable of programming all Intel PROMs.

ICE (In-Circuit Emulator) options extend Intellec MDS diagnostic capabilities into user configured system allowing real time emulation of user processors.

Optional I/O modules expandable in groups of four 8-bit input and output ports to a maximum of 88 ports (all TTL compatible).

ROM resident system monitor includes all necessary functions for program loading, debugging, and execution.

RAM resident macro assembler used to assemble all 8080 machine instructions with full macro and conditional assembly capabilities.

RAM resident text editor with powerful string search, substitution, insertion, and deletion commands.

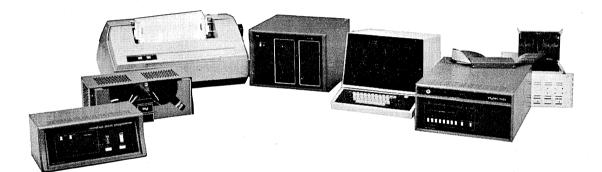

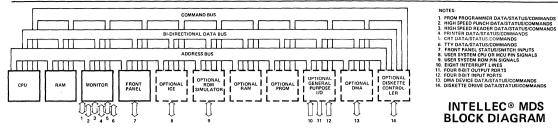

The Intellec<sup>®</sup> MDS is a modular microcomputer development system containing all necessary hardware and software to develop and implement Intel MCS<sup>T.M.</sup>20 and Series 3000 microcomputer systems. The addition of MDS options and peripherals provides the user with a complete in-circuit microcomputer development system, supporting product design from program development through prototype debug, to production and field test.

### INTELLEC<sup>®</sup> MDS HARDWARE

The standard Intellec<sup>®</sup> MDS consists of four microcomputer modules (CPU, 16K RAM Memory, Front Panel Control, and Monitor), an interconnecting printed circuit motherboard, power supplies, fans, a chassis, and a front panel. Modular expansion capability is provided by 14 additional sockets on the motherboard.

The CPU module uses Intel's powerful NMOS 8-bit 8080 microprocessor. The 8080's 2  $\mu$ s cycle time, 78 instructions, unlimited subroutine nesting, vectored interrupt, and DMA capabilities are fully utilized by the Intellec MDS. Bus control logic resolves bus contention conflicts between the CPU module and other modules capable of acquiring control of the bus. The CPU module interfaces with a sixteen line address bus and a bidirectional eight line data bus. 8080 status signals are decoded and utilized for memory and I/O operations. An eight-level, nested interrupt priority system, complete with an interrupt priority push-down stack, resolves contention for 8080 interrupt servicing.

The RAM memory module contains 16K bytes of Intel 2107 dynamic RAM which operates at full processor speed. All necessary address decoding and refresh logic is contained on the module.

The front panel control module provides system initialization, priority arbitration, and real time clock functions. System initialization routines reside in a 256 byte, PROM resident, bootstrap loader. An eight-level priority arbitration network resolves bus contention requests among potential bus masters. A 1 ms interrupt request generator, which can be disabled under program control, provides real time clock functions. A 10 ms automatic time-out feature is also provided to force an interrupt request if nonexistent memory or I/O is addressed.

The Monitor module contains the Intellec MDS system monitor and all Intellec MDS peripheral interface hardware. The system monitor resides in a 2K byte Intel 8316 ROM. The module contains all necessary control and data transfer circuitry to interface with the following Intellec MDS peripherals:

- Teletype

- CRT

- High Speed Paper Tape Reader

- High Speed Paper Tape Punch

- PROM Programmer

- Line Printer

The Intellec MDS universal bus structure enables several CPU and DMA devices to share the bus by operating at different priority levels. Resolution of bus exchanges is synchronized by a bus clock signal which is derived independently from processor clocks. Read/write transfers may take place at rates up to 5 MHz. The bus structure contains provisions for up to 16-bit address and data transfers and is not limited to any one Intel microcomputer family.

The Intellec MDS front panel is intended to augment the primary user interaction medium, the system console. The simplicity of the front panel coupled with the power of the system monitor provides an efficient user/Intellec interface. The front panel contains eight interrupt request switches with corresponding indicators, CPU RUN and HALT status indicators, a bootstrap loader switch, RESET switch, and a POWER ON switch and indicator.

The basic Intellec MDS capabilities may be significantly enhanced by the addition of the following optional features.

ICE (In-Circuit Emulator) extends Intellec MDS diagnositic capabilities into user configured systems. The Intellec MDS resident ICE processor operates in conjunction with the MDS host CPU and interfaces to the user system via an external cable. The ICE processor replaces the user system processor providing real time emulation capability. MDS resident memory and I/O may be substituted for equivalent user system elements, allowing the hardware designer to sequentially develop his system by integrating MDS and user system hardware. MDS display and debug hardware eliminate the need for specially constructed user system equivalents. Augmenting these capabilities are such powerful ICE debug functions as setting breakpoints, tracing program flow, single stepping, examining and altering CPU registers and memory locations.

The Universal PROM Programmer is an Intellec MDS peripheral capable of programming and verifying the following Intel PROMs: 1702A, 2704, 2708, 3601, 3604, 3624, 8702A, 8704, and 8708. Programming and verification operations are initiated from the Intellec MDS system console and are controlled by programs resident in the Intellec MDS and Universal PROM Programmer.

The addition of a single or dual drive Diskette Operating System significantly reduces program development time. An intelligent controller, constructed around Intel's powerful Series 3000 computing elements, provides diskette interface and control. Intel's software operating system (IDOS) in conjunction with the diskette operating system hardware provides a highly efficient and easy to use method of assembling, editing, and executing programs.

Customized user I/O requirements may be satisfied by adding I/O modules. Each 1/O module contains four 8-bit input ports (latched or unlatched), four 8-bit latched output ports (with adjustable strobe pulses), and eight system interrupt lines. All inputs and outputs are TTL compatible. Optional I/O may be expanded to a maximum of 44 input and 44 output ports.

Memory may be expanded by adding RAM or PROM modules in user defined combinations. Up to 64K bytes of RAM may be added in 16K byte increments. PROM (Intel 8702A) may be added in 256 byte increments by adding PROM modules with socket capacity for 6K bytes and populating each module with the desired number of PROMs. Maximum PROM capacity is 12K bytes. RAM/PROM memory overlap is resolved by giving PROM priority.

DMA (direct memory access) modules work in conjunction with the Intellec MDS universal bus to maximize the efficiency of data transfers between MDS memory and selected I/O devices. Each module contains all the necessary control and data transfer logic to implement a complete DMA channel.

A ROM simulator composed of high speed bipolar RAM emulates Series 3000 bipolar microprogram ROM memory. Each ROM simulator module may be used in  $512 \times 16$  or  $1024 \times 8$  configurations.

### INTELLEC<sup>®</sup> MDS SOFTWARE

Resident software provided with the Intellec<sup>®</sup> MDS includes the system monitor, 8080 macro assembler and text editor. Used together, these three programs simplify program preparation and speed the debugging task.

The system monitor provides complete control over operation of the Intellec MDS. All necessary functions for program loading and execution are provided. Additional commands provide extensive debug facilities and PROM programming functions. System peripherals may be dynamically assigned either via monitor commands or through calls to the system monitor's I/O subroutines.

Programs may be loaded from the reader device in either BNPF or hexadecimal format. Utility commands which aid in the execution and checkout of programs include:

- · initialize memory to a constant

- move a block of memory to another location

- display memory

- modify RAM memory

- examine and modify CPU registers

- set breakpoints

- initiate execution at any given address

- perform hexadecimal arithmetic

- examine and modify the interrupt mask

The Intellec MDS System Monitor contains a powerful and easily expandable input/output system, which is built around four logical device types; console device, reader device, punch device and list device. Associated with each logical device may be any one of four physical devices. The user controls physical device assignment to each logical device through a System command.

Drivers are provided in the system monitor for the Universal PROM Programmer, ASR 33 teletype, high speed paper tape reader, high speed paper tape punch, line printer, and CRT. The user may write his own drivers for other peripheral devices and easily link them to the system monitor.

All system peripherals may be accessed simply by calling I/O subroutines in the system monitor. In addition, the user may dynamically reconfigure his system by monitor commands or by calling system subroutines which can assign a different physical device to each logical device. The user may also determine the current system peripheral configuration, check I/O status and determine the size of available memory.

The monitor is written in 8080 Assembly Language and resides in 2K bytes of ROM memory.

The Intellec MDS Resident Assembler translates symbolic 8080 assembly language instructions into the appropriate machine operation codes. In addition to eliminating the errors of hand translation, the ability to refer to program addresses with symbolic names makes it easy to modify programs by adding or deleting instructions. Full macro capability eliminates the need to rewrite similar sections of code repeatedly and simplifies program documentation. Conditional assembly permits the assembler to include or delete sections of code which may vary from system to system, such as the code required to handle optional external devices.

The assembler performs its function in three passes. The first pass builds the symbol table. The second pass produces a source listing and provides error diagnostics. The third pass produces the object code. If the punch and list devices are separate (e.g. a high speed punch or printer is available) passes 2 and 3 may be combined into one pass.

Object code produced by the assembler is in hexadecimal format. It may be loaded directly into the Intellec MDS for execution and debugging or may be converted by the system monitor to BNPF format for ROM programming.

The assembler is written in PL/M<sup>T.M.</sup>80, Intel's high level systems programming language. It occupies 12K bytes of RAM memory including space for over 800 symbols. The symbol table size may be expanded to a maximum of 6500 symbols by adding RAM memory. All I/O in the assembler is done through the system monitor, enabling the assembler to take advantage of the monitor's I/O system. The assembler is shipped in hexadecimal object format on paper tape or diskette and is standard with each Intellec MDS.

The Intellec MDS editor is a comprehensive tool for the entry and correction of assembly language programs for the Intel 8080 microcomputer. Its command set allows manipulation of either entire lines of text or individual characters within a line.

Programs may be entered directly from the console keyboard or from the system reader device. Text is stored internally in the editor's workspace, and may be edited with the following commands:

- string insertion or deletion

- string search

- string substitution

To facilitate the use of these editing commands, utility commands are used to change positions in the workspace. These include:

- move pointer by line or by character

- move pointer to start of workspace

- move pointer to end of workspace

The contents of the workspace may be listed to the system console or written to the system list or punch device for future use.

The text editor is written in PL/M<sup>T.M.</sup>80. It occupies 8K bytes of RAM memory, including over 4500 bytes of work-space. The workspace may be expanded to a maximum of 58K bytes by adding RAM memory. All I/O in the editor is done through the system monitor, enabling the editor to take advantage of the monitor's I/O system. The editor is shipped in hexadecimal object format on paper tape or diskette and is standard with each Intellec MDS.

### DEVELOPMENT SYSTEMS

### **MDS-800**

### HARDWARE SPECIFICATIONS

### WORD SIZE

Host Processor (Intel 8080)

Data: 8 bits

Instruction, 8, 16, or 24 bits

### MEMORY SIZE

- RAM: 16K bytes expandable to 64K bytes using optional modules.

- ROM: 2K bytes expandable to 14K bytes in 256 byte increments using optional PROM modules.

- PROM: 256 bytes expandable to 12K bytes using optional modules.

- RAM, ROM and PROM may be combined in user Total: defined configurations up to a maximum of 64K bytes.

#### MACHINE CYCLE TIME

Host Processor (Intel 8080): 2.0 µS

### **BUS TRANSFER RATE**

Maximum bus transfer rate of 5 MHz.

#### SYSTEM CLOCKS

Host Processor (Intel 8080) Clock: Crystal controlled at 2 MHz ±0.1%.

Bus Clock: Crystal controlled at 9.8304 MHz ±0.1%.

#### **I/O INTERFACES**

### CRT:

| Baud Rates:  | 110/300/600/1200/2400/4800/9600 |

|--------------|---------------------------------|

|              | (selectable).                   |

| Code Format: | 7–12 level code (programmable). |

| Parity:      | Odd/even (programmable).        |

| Interface:   | TTL/RS232C (selectable).        |

| TY:          |                                 |

#### Т

| Baud Rate:   | 110                  |

|--------------|----------------------|

| Code Format: |                      |

| Input:       | 10 level or greater. |

| Output:      | 11 level.            |

| Parity:      | Odd.                 |

| Interface:   | 20 mA current loop.  |

High Speed Paper Tape Reader: Т

| I ransfer Rate: | 200 cps.      |

|-----------------|---------------|

| Control:        | 2-bit output. |

|                 | 1-bit input.  |

| Data:           | 8-bit byte    |

| Interface:      | TTL           |

Punch:

Transfer Rate: 75 cps Control: 2-bit output 1-bit input 8-bit byte Data: TTL Interface:

Printer:

| put |

|-----|

|     |

|     |

|     |

| p   |

**PROM Programmer:**

| Control:   | 3 strobes for multiplexed output data. |

|------------|----------------------------------------|

| Data:      | 8-bit bidirectional                    |

| Interface: | TTL                                    |

#### **GENERAL PURPOSE I/O (OPTIONAL)**

| Input Ports:         | 8-bit TTL compatible (latched or unlatched); |

|----------------------|----------------------------------------------|

|                      | expandable in 4 port increments to 44 input  |

|                      | ports.                                       |

| <b>Output Ports:</b> | 8-bit TTL compatible (latched); expandable   |

|                      | in 4 port increments to 44.                  |

| 1                    | O TTL semenatible internet lines             |

Interrupts: 8 TTL compatible interrupt lines.

### INTERRUPT

8-level, maskable, nested priority interrupt network initiated from front panel or user selected devices.

### DIRECT MEMORY ACCESS

Standard capability on Intellec bus; implemented for user selected DMA devices through optional DMA module maximum transfer rate of 2 MHz.

### MEMORY ACCESS TIME

RAM: 450 ns PROM: 1.3 µs using Intel 8708A PROM.

### PHYSICAL CHARACTERISTICS

Dimensions: 8.5" X 19" X 17" 21.6 cm X 48.3 cm X 43.2 cm Weight: 65 lb (29.5 kg)

### **ELECTRICAL CHARACTERISTICS**

| DC POWER<br>SUPPLY<br>(Volts) | POWER SUPPLY<br>CURRENT<br>(Amps) | BASIC SYSTEM<br>REQUIRE<br>(Amp | MENTS   |

|-------------------------------|-----------------------------------|---------------------------------|---------|

|                               |                                   | Maximum                         | Typical |

| + 5±5%                        | 35.0                              | 9.0                             | 6.6     |

| +12 ±5%                       | 3.0                               | 0.7                             | 0.4     |

| -10 ±5%                       | 3.0                               | 0.2                             | 0.2     |

| -12 ±5%                       | 0.5                               |                                 |         |

### AC POWER REQUIREMENTS

50-60 Hz; 115/230 VAC; 150 Watts

#### ENVIRONMENTAL CHARACTERISTICS Operating Temperature: 0 to 55°C

10-6

### SOFTWARE SPECIFICATIONS

### CAPABILITIES

System Monitor:

Devices supported include:

ASR 33 teletype

Intel high speed paper tape reader

Paper tape punch

CRT

Printer

Universal PROM programmer

4 logical devices recognized

16 physical devices maximum allowed

### Macro Assembler:

800 symbols in standard system; automatically expandable with additional RAM memory to 6500 symbols maximum.

Assembles all seventy-eight 8080 machine instructions plus 10 pseudo-operators.

Text Editor:

12K bytes of workspace in standard system; automatically expandable with additional RAM memory to 58K bytes.

### **OPERATIONAL ENVIRONMENTAL**

System Monitor:

Required hardware: Intellec MDS 331 bytes RAM memory 2K bytes ROM memory System console

Macro Assembler:

Required hardware: Intellec MDS 12K bytes RAM memory System console Reader device Punch device List device

Required software: System monitor

Text Editor:

Required hardware: Intellec MDS 8K bytes RAM memory System console Reader device Punch device Required software:

System monitor

Tape Format: Hexadecimal object format.

### MDS OPTIONS

MDS-016 16K Dynamic RAM MDS-406 6K PROM (sockets and logic) MDS-501 DMA Channel Controller MDS-504 General Purpose I/O Module MDS-600 Prototype Module MDS-610 Extender Module MDS-620 Rack Mounting Kit

### MDS EMULATORS/SIMULATOR

MDS-ICE-303001 In-Circuit EmulatorMDS-ICE-808080 In-Circuit EmulatorMDS-SIM-100Bipolar ROM Simulator

#### **MDS PERIPHERALS**

MDS-UPPUniversal PROM ProgrammerMDS-PTRHigh Speed Paper Tape ReaderMDS-DOSDiskette Operating System

### MDS INTERFACE CABLES/CONNECTORS

MDS-900 CRT Interface Cable MDS-910 Line Printer Interface Cable High Speed Reader Interface Cable MDS-915 MDS-920 High Speed Punch Interface Cable MDS-930 Peripheral Extension Cable DMA Cable MDS-940 MDS-950 General Purpose I/O Cable MDS-960 25-pin Connector Pair MDS-970 37-pin Connector Pair MDS-980 60-pin Motherboard Auxiliary Connector MDS-985 86-pin Motherboard Main Connector MDS-990 100-pin Connector Hood

### EQUIPMENT SUPPLIED

Central Processor Module **RAM Memory Module** Monitor Module (System I/O) Front Panel Control Module Chassis with Motherboard **Power Supplies Finished Cabinet** Front Panel **ROM Resident System Monitor RAM Resident Macro Assembler RAM Resident Text Editor** Hardware Reference Manual **Reference Schematics Operator's Manual** 8080 Assembly Language Programming Manual System Monitor Source Listing 8080 Assembly Language Reference Card TTY Cable European AC Adapter AC Cord

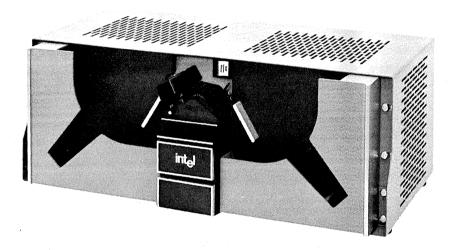

### MDS-DOS DISKETTE OPERATING SYSTEM AND MDS-DRV ADDITIONAL DRIVE UNIT

Floppy diskette operating system providing high speed Input/Output and data storage for the Intellec<sup>®</sup> MDS.

Supports all existing standard Intellec<sup>®</sup> peripherals.

Data on flexible diskette addressed using IBM softsectored format which allows 1/4 million byte data capacity per diskette.

Up to 200 files per diskette.

int

Dynamic allocation and deallocation of diskette sectors for variable length files.

Device independence realized by assignment of unique file names to each peripheral device.

Supports optional Intellec MDS ICE-80 (In-circuit Emulator) for Intel<sup>®</sup> 8080 Microprocessor.

Diskette system macro assembler used to assemble all 8080 machine instructions with full macro and conditional assembly capabilities.

Diskette system text editor with string search, substitution, insertion, and deletion commands.

Listing produced by macro assembler can be directed to diskette allowing interrogation from high speed console device.

Diskette operating system software products loaded into Intellec MDS RAM in seconds.

Access to all Intellec MDS Monitor facilities.

Programs created, edited, assembled, executed and debugged without paper tape handling.

Diskette operating system functions callable from user programs.

The Intellec MDS Diskette Operating System is a general purpose, high speed data handler and file manipulation system for use with the Intellec MDS and its peripherals. The use of a single or dual drive Diskette Operating System significantly reduces program development time. The software system known as ISIS (Intel Systems Implementation Supervisor), provides the ability to edit, assemble, execute and debug programs, and performs all file management tasks for the user.

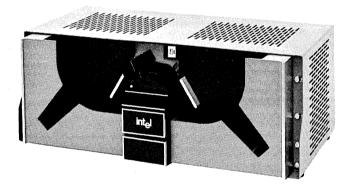

MDS-DOS Diskette Drive and Optional MDS-DRV

### HARDWARE

The INTELLEC<sup>®</sup> MDS diskette system provides direct access bulk storage, intelligent controller, and up to two diskette drives. Each drive provides 1/4 million bytes of storage with a data transfer rate of 250,000 bits/second. The controller is implemented with Intel's powerful Series 3000 Bipolar Microcomputer Set. The controller provides an interface to the INTELLEC MDS bus, as well as supporting the two diskette drives. The MDS diskette system records all data in the IBM-compatible soft sector format.

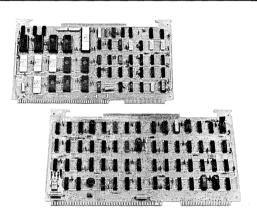

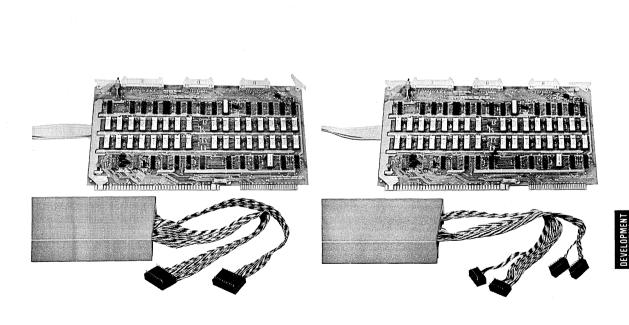

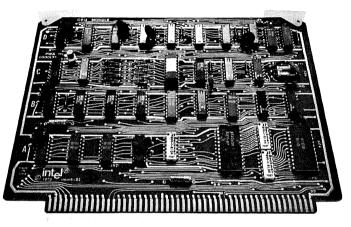

The MDS diskette controller consists of two boards, the Channel Board and the Interface Board. These two printed circuit boards reside in the INTELLEC MDS chassis and constitute the diskette controller. Each of the systems components is shown in the photograph, and are described in more detail in the following paragraphs.

**DOS Channel and Interface Controller Boards**

### CHANNEL BOARD

The *Channel Board* is the primary control module within the diskette system. The Channel Board receives, decodes, and responds to channel commands from the 8080 Central Processor Unit (CPU) in the INTELLEC MDS system. The Channel Board can access a block of INTELLEC MDS system memory to determine the particular diskette operations to be performed and fetch the parameters required for the successful completion of the specified operation.

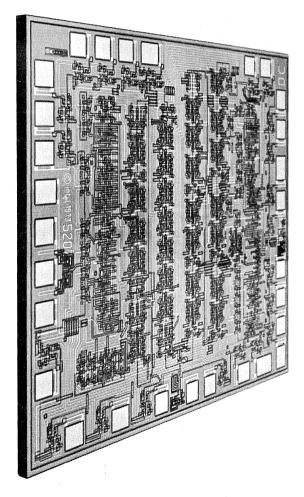

The control functions of the Channel Board have been achieved with an 8-bit microprogrammed processor, designed with Intel's Series 3000 Bipolar Microcomputer Set. This 8-bit processor includes four 3002 Central Processing Elements (2-bit slice per CPE), a 3001 Microprogram Control Unit, and 512  $\times$  32 bits of 3604 programmable-read-only-memory (PROM) which stores the microprogram. It is the execution of the microprogram by the microcomputer set which actually effects the control capability of the Channel Board.

### INTERFACE BOARD

The Interface Board provides the diskette controller with a means of communication with the diskette drives, as well as with the INTELLEC MDS system bus. Under control of the microprogram being executed on the Channel Board, the Interface Board generates those signals which cause the read/write head on the selected drive to be loaded (i.e., to come in contact with the diskette platter), cause the head to move to the proper track and verify successful operation. The Interface Board accepts the data being read off the diskette, interprets synchronizing bit patterns, checks the validity of the data using a cyclic redundancy check (CRC) polynomial, and then transfers the data to the Channel Board.

During write operations, the Interface Board outputs the data and clock bits to the selected drive at the proper times, and generates the CRC characters which are then appended to the data.

When the diskette controller requires access to INTELLEC MDS system memory, the Interface Board requests and maintains DMA master control of the system bus, and generates the appropriate memory command. The Interface Board also acknowledges I/O commands as required by the INTELLEC MDS bus.

The Diskette System is capable of performing seven different operations: recalibrate, seek, format track, write data, write deleted data, read data, and verify CRC.

### DISKETTE DRIVE MODULES

Each diskette drive consists of read/write and control electronics, drive mechanisms, read/write head, track positioning mechanism, and the removable floppy diskette platter. These components interact to perform the following functions:

- Interpret and generate control signals.

- Move read/write head to selected track.

- Read and write data.

Additional Drive Unit MDS-DRV

### SOFTWARE - INTEL SYSTEM IMPLEMENTATION SUPERVISOR (ISIS)

The ISIS programs and subroutines reside on the system diskette and provide a broad range of user-oriented design aid software. Total file management and input editing features greatly reduce software development time. The ISIS 8080 Macro Assembler can be loaded in seconds, from the diskette, and all passes executed without the need for user interaction. Object code and list files may be directed to any output device, or stored as diskette files. A special ISIS utility is provided which converts files from hexadecimal to absolute binary for high-speed retrieval and execution. Powerful system console commands are provided in an easy to use English context. Debugging is initiated by a special prefix to any system command or program call which causes Monitor mode to be entered directly from the program call along with its calling parameters.

A file is a user-defined collection of information of variable length. ISIS also treats each of the standard INTELLEC<sup>®</sup> MDS supported peripherals as files through preassignment of unique file names to each device. In this manner data can be copied from one device to another (i.e., tape reader to tape punch) using the same command required to copy one diskette data file to another. ISIS provides automatic implementation of random access disk files. Each file is identified by a user-chosen name unique on its diskette. Up to 200 files may be stored on each 1/4 million byte diskette.

### SYSTEM COMMANDS

The user is provided with a wide range of system commands that offer powerful file and program manipulation features:

- The DIR command lists the names, sizes and attributes of files resident on the specified disk directory.

- The RENAME command allows users to change the identifying names of files.

- The COPY command allows users to create new copies of existing files or to transfer files from one device to another.

- The ATTRIB command allows the user to set or reset write-protection and other characteristics of a disk file.

- The DELETE command removes a file from a diskette, thereby freeing space for allocation for other files.

- The HEXBIN command coverts an Intel standard hexadecimal format file into absolute binary format for a reduction in load time and space.

- The FORMAT command formats a diskette on a second disk drive so that it may be used by ISIS.

- The DEBUG command loads the name program and parameters, and gives control to the INTELLEC MDS monitor for execution and/or debugging in the event of an error.

- Programs may be loaded and executed by typing the program name as a command. Users may therefore name their own programs with descriptive verbs and extend their command repertoire.

### ISIS 8080 MACRO ASSEMBLER

The ISIS 8080 Macro Assembler translates symbolic 8080 assembly language instructions into the appropriate machine operation codes. In addition to eliminating the errors of hand translation, the ability to refer to program addresses with symbolic names makes it easy to modify programs by adding or deleting instructions. Full macro capability eliminates the need to rewrite similar sections of code repeatedly and simplifies program documentation. Conditional assembly permits the assembler to include or delete sections of code which may vary from system to system, such as the code required to handle optional external devices.

The ISIS Assembler accepts diskette file input and produces an object file with corresponding symbol table and assembly listing file with any errors. The list file may then be interrogated from the system console or copied to the appropriate list device. The object file may be kept on diskette in its hexadecimal format for loading under ISIS supported software packages such as the optional 8080 In-Circuit Emulator (ICE-80). For loading directly under control of ISIS, the object file may be converted from hexadecimal to absolute binary format using the HEXBIN command.

The ISIS 8080 Macro Assembler is written in PL/M<sup>TM</sup>-80, Intel's high level systems programming language. It occupies 12K bytes of RAM memory allowing space for over 1000 symbols when used with ISIS in a 32K INTELLEC MDS system. The symbol table size may be expanded by adding additional RAM memory.

### **ISIS TEXT EDITOR**

The ISIS Text Editor is a comprehensive tool for the entry and correction of assembly language programs for the Intel 8080 microcomputer. Its command set allows manipulation of either entire lines of text or individual characters within a line.

Programs may be entered from the console keyboard or may be loaded directly. Text is stored internally in the editor's workspace, and may be edited with the following commands:

- string insertion or deletion

- string search

- string substitution

To facilitate the use of these editing commands, utility commands are used to change positions in the workspace, These include:

- move pointer by line or by character

- move pointer to start of workspace

- move pointer to end of workspace

The contents of the workspace are stored on the diskette and can be immediately accessed by ISIS commands or other programs such as the ISIS 8080 Macro Assembler.

The ISIS Text Editor is written in PL/M<sup>TM</sup>-80. It occupies 8K bytes of RAM memory allowing approximately 12K bytes of workspace in a 32K INTELLEC MDS system.

### SOFTWARE SPECIFICATIONS

### ISIS CAPABILITIES

ISIS commands (User entries at console input device)

### File commands:

| List diskette directory.      |

|-------------------------------|

| Make a copy of a file.        |

| Remove a file from diskette.  |

| Change the name of a diskette |

| file.                         |

| Change the attributes of a    |

| diskette file.                |

|                               |

### Diskette initialization:

FORMAT Initialize a new diskette.

### Program debug and conversion:

| DEBUG  | Execute a program in debug |

|--------|----------------------------|

|        | mode.                      |

| HEXBIN | Convert program from hexa- |

|        | decimal format to absolute |

|        | binary.                    |

### Program execution:

| An executable program in a disk-                              |  |  |

|---------------------------------------------------------------|--|--|

| file can be executed by<br>ring the file name as a com-<br>d. |  |  |

|                                                               |  |  |

### ISIS System Calls (System services called by user programs)

### Input/output operations:

| OPEN   | Initialize file for input/output operations            |

|--------|--------------------------------------------------------|

| READ   | Transfer data from file to mem-<br>ory                 |

| WRITE  | Transfer data from memory to file                      |

| SEEK   | Position diskette file pointer at any byte in the file |

| RESCAN | Position pointer to beginning of<br>current line       |

| CLOSE  | Terminate input/output<br>operations on file           |

### Diskette directory maintenance

| DELETE | Delete a file from the diskette |

|--------|---------------------------------|

|        | directory                       |

| RENAME | Change diskette file name       |

| ATTRIB | Change diskette file attributes |

### Console Reassignment and error message output

| CONSOLE | Change console device                                    |

|---------|----------------------------------------------------------|

| WHOCON  | Determine currently assigned sys-                        |

| ERROR   | tem console<br>Output error message on system<br>console |

| DOS                                                                                                       | DEVELOPMENT SYSTEMS                                                         |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Program loading an                                                                                        | d execution                                                                 |

| LOAD                                                                                                      | Load a file of executable code<br>and transfer control to loaded<br>program |

| EXIT                                                                                                      | Terminate program and return to ISIS control                                |

| -                                                                                                         | oler:<br>in 32K system; automatically ex-<br>dditional RAM memory.          |

| Assembles all se<br>tions plus 10 pse                                                                     | venty-eight 8080 machine instruc-<br>eudo-operators.                        |

| •                                                                                                         | workspace in 32K system; auto-<br>lable with additional RAM memory.         |

| ISIS OPERATIONAL EN                                                                                       | VIRONMENTAL                                                                 |

| Required hardware<br>Intellec MDS<br>32K bytes RAM<br>System console                                      |                                                                             |

| Required software:<br>System monitor                                                                      |                                                                             |

| Macro Assembler:<br>Required hardware<br>Intellec MDS<br>MDS-DOS Diske<br>32K bytes RAM<br>System console | ette Operating System                                                       |

| Text Editor:<br>Required hardware<br>Intellec MDS<br>MDS-DOS Diske<br>32K bytes RAM<br>System console     | ette Operating System                                                       |

| Required software:<br>ISIS<br>System monitor                                                              |                                                                             |

| Required software:<br>ISIS<br>System monitor                                                              |                                                                             |

| ICE-80 (Optional)                                                                                         |                                                                             |

| Required hardware<br>Intellec MDS<br>MDS-80 ICE<br>32K bytes RAM<br>MDS-DOS Diske                         |                                                                             |

|                                                                                                           |                                                                             |

Required software: ISIS

System monitor

### **MDS-DOS**

### HARDWARE SPECIFICATIONS

### MEDIA

Flexible Diskette One Recording Surface IBM Soft Sector Format 77 Tracks/Diskette 26 Sectors/Track 128 Bytes/Sector

### PHYSICAL CHARACTERISTICS

(Chassis and Drives)

Mounting:

Table-Top or Standard 19" Retma Cabinet

Height:

12.08" (30.68 cm)

Width:

16.88" (42.88 cm)

Depth:

19.0" (48.26 cm)

Weight:

1 Drive 51 lb (23 kg)

2 Drives 64 lb (29 kg)

### **ELECTRICAL CHARACTERISTICS**

### Chassis

**DC** Power Supplies

Voltage Current

- 5V 3A ±5%

- -5V 600 mA ±5%

- 24V 4A ±5%

- AC Power Requirements

3-wire input with center conductor (earth ground) tied to chassis

Single-phase, 115/230 VAC; 50-60 Hz; 160 watts

### INTELLEC<sup>®</sup> MDS-DOS Controller

DC Power Requirements Channel Board: 5V @ 3.75A (typ), 5A (max) Interface Board: 5V @ 1.5A (typ), 2.5A (max)

### DISKETTE DRIVE PERFORMANCE SPECIFICATION

| Capacity (Unformatted):<br>Per Disk      |

|------------------------------------------|

| Capacity (Formatted):           Per Disk |

| Data Transfer Rate                       |

| Average Random Positioning Time          |

### **ENVIRONMENTAL CHARACTERISTICS**

### MEDIA

Temperature:

Operating

15.6°C to 51.7°C

Non-Operating:

5°C to 55%

Humidity:

0perating:

Operating:

8 to 80% (Wet bulb 29.4°C)

Non-Operating:

8 to 90%

#### **DRIVES AND CHASSIS**

Temperature:

Operating:

10°C to 38°C

Non-Operating:

-35°C to 65°C

Humidity:

Operating:

Operating:

20% to 80% (Wet bulb 26.7°C)

Non-Operating:

5% to 95%

### MDS-DOS CONTROLLER BOARDS

Temperature: Operating: 0 to 70°C Non-Operating: -55°C to 85°C Humidity: Operating: Up to 90% relative humidity without condensation. Non-Operating: All conditions without condensation of water or frost.

### EQUIPMENT SUPPLIED

Cabinet, Power Supplies, Line Cord, Single Drive FDC Channel Board FDC Interface Board Dual Auxiliary Board Connector Floppy Disk Controller Cable Floppy Disk Peripheral Cable Hardware Reference Manual Reference Schematics ISIS System Diskette ISIS Operators Manual ISIS/MDS Monitor Bootstrap PROM

### OPTIONAL EQUIPMENT

Rack Mount Kit MDS-DRV Additional Drive Unit Blank Diskettes ISIS System Diskettes

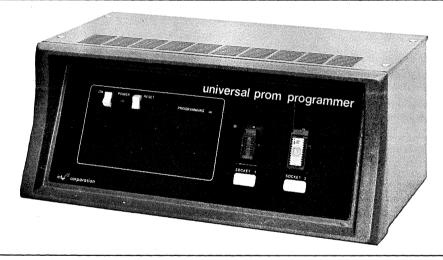

### MDS-UPP UNIVERSAL PROM PROGRAMMER

Intellec<sup>®</sup> MDS peripheral capable of programming the following Intel PROMs: 1702A, 2704, 2708, 3601, 3604, 3624, 8702A, 8704, 8708.

Personality cards used for specific Intel PROM programming requirements.

Zero insertion force sockets for both 16-pin and 24-pin PROMs.

Flexible power source for system logic and programming pulse generation.

PROM programming verification facility.

Stand alone or rack mountable.

The Universal PROM Programmer is an Intellec MDS peripheral capable of programming and verifying the following Intel PROMs: 1702A, 2704, 2708, 3601, 3604, 3624, 8702A, 8704, and 8708. Programming and verification operations are initiated from the Intellec MDS system console and are controlled by programs resident in the Intellec MDS and Universal PROM Programmer.

### **SPECIFICATIONS**

### INTERFACE

Data: Two 8-bit unidirectional buses Commands: 3 Write Commands 2 Read Commands Initiate Command

### AVERAGE PROGRAMMING TIME

| 1702A/8702A: | 40 seconds  |

|--------------|-------------|

| 2708/8708:   | 5 minutes   |

| 3601:        | 2 seconds   |

| 3604:        | 10 seconds  |

| 3624:        | 10 seconds  |

| 2704/8704:   | 2.5 minutes |

#### PHYSICAL CHARACTERISTICS

Dimensions: 6" X 7" X 17" 14.7 cm X 17.2 cm X 41.7 cm Weight: 18 lb (8.2 kg)

### ENVIRONMENTAL CHARACTERISTICS

Operating Temperature: 0° to 70°C.

### OPTIONS

Personality Cards: MDS-UPP-361:3601 Personality Card MDS-UPP-864:8604/3604/3624 Personality Card MDS-UPP-872:8702A/1702A Personality Card MDS-UPP-878:8708/8704/2708/2704 Personality Card

PROM Programming Sockets: MDS-UPP-501: 16-pin/24-pin pair MDS-UPP-502: 24-pin/24-pin pair

### EQUIPMENT SUPPLIED

الأجيار الجاري الأفر الأقربية والمرا

Cabinet Power Supplies 4040 Intelligent Controller Module Specified Zero Insertion Force Socket Pair Intellec MDS Interface Cable Hardware Reference Manual Reference Schematics

# intel

### **MDS-PTR HIGH SPEED PAPER TAPE READER**

Intellec<sup>®</sup> MDS high speed paper tape reader peripheral

20 times faster than standard ASR-33 Teletype reader

Loads 16K Intellec MDS program memory in less than three minutes.

Data transfer at asynchronous rates in excess of 200 characters per second

Rack mountable or stand-alone

The MDS-PTR high speed paper tape reader is an Intellec MDS peripheral that reads paper tape over twenty times faster than the standard ASR-33 Teletype reader. This translates into a significantly faster development cycle due to a marked reduction in the time required for repetitive program loading, assembly, and editing operations.

### SPECIFICATIONS

### TAPE MOVEMENT

Tape Reader Speed:

0 to 200 characters per second asynchronous

Tape Stopping:

Stops "On Character"

### TAPE CHARACTERISTICS

Tape must be prepared to ANSI  $\times$  3.18 or EMCA 10 Standards for base materials and perforations.

Reads tape of any material with thickness between 0.0027'' and 0.0045'' with transmissivity less than or equal to 57% (oiled buff paper tape).

Tape loading: in line

Tape width: 1 inch

### PHYSICAL CHARACTERISTICS

Height: 7.75 in. (19.69 cm) Width: 19.25 in. (48.90 cm) Depth: 11.62 in. (29.52 cm) Weight: 13 lb (5.9 kg)

### **ELECTRICAL CHARACTERISTICS**

AC Power Requirements: 3-wire input with center conductor (earth ground) tied to chassis. 100, 115, or 127 VAC, single phase at 3.0 amps or 220 or 240 VAC and 1.5 amps; 47 to 63 Hz.

#### ENVIRONMENTAL CHARACTERISTICS

Temperature:

Operating: 0 to 55°C (free air) Non-operating: -55°C to +85°C

Humidity:

- Operating: Up to 90% relative humidity without condensation.

- Storage: All conditions without condensation of water or frost.

### EQUIPMENT SUPPLIED

Paper Tape Reader Reader Cable Fanfold Tape Guide Fanfold Paper Tape Hardware Manual Installation and Operations Guide Fanfold Guide Installation Instructions

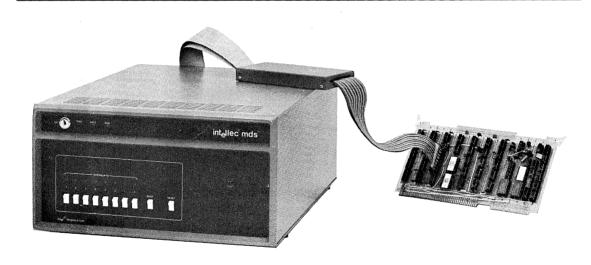

### MDS-ICE-80 8080 IN-CIRCUIT EMULATOR

Extends powerful Intellec<sup>®</sup> MDS diagnostic capabilities into user configured system allowing real time (2 MHz) emulation of the user system 8080.

User configured system can share Intellec MDS RAM, ROM, and PROM memory.

I/O translation allows user configured systems to share Intellec MDS input/output facilities.

Capability to display previously executed instructions with corresponding address, data, and 8080 status information.

Capability to examine and alter CPU registers and main memory.

Direct Intellec MDS connection to user configured system via an external cable and 40-pin plug.

ICE-80 is an Intellec MDS resident module that interfaces to any user configured 8080 system and allows the designer to emulate the user 8080 in real time, single step the user system's 8080, substitute Intellec MDS memory and I/O for user system equivalents, and extend powerful debug functions into the user system.

### SPECIFICATIONS

### WORD SIZE

Instruction: 8, 16 or 24 bits Data: 8 bits

#### CENTRAL PROCESSOR

8080 CPU, 2  $\mu$ S cycle time, 8-bit accumulator, six 8-bit registers, subroutine nesting to any level, multiple level. interrupt capability.

### INSTRUCTION SET

78 instructions including conditional branching, binary arithmetic, logical operations, register-to-register transfers. and I/O.

### CONNECTORS

Edge Connector: CDC VPB01E43A00A1

### PHYSICAL CHARACTERISTICS

Width: 12.00 in. Height: 6.75 in. Depth: 0.50 in.

### ELECTRICAL CHARACTERISTICS

DC Power:

- $V_{CC} = +5 \pm 5\%$

- I<sub>CC</sub> = 9.81A max.; 6.90A typ.

- $V_{DD} = +12 \pm 5\%$

- I<sub>DD</sub> = 79 ma max.; 45 ma typ.  $I_{BB} = 1 \text{ ma max.}; 1 \mu \text{ a typ.}$

- $V_{BB} = -9V \pm 5\%$

### SPECIFICATIONS

### MEMORY ADDRESSING

Intellec MDS RAM, ROM and PROM may be combined with user system ROM, PROM, and RAM combinations in 4K segments up to a maximum of 65, 536 bytes.

### **I/O ADDRESSING**

Intellec MDS I/O ports may be combined with user system I/O ports in 16 port groups, up to a maximum of 256 8-bit input and 256 8-bit output ports.

### USER SYSTEM INTERFACE

Cable carrying all 8080 address, data, and control signals terminated in a 40-pin plug.

### SYSTEM CLOCK

Crystal controlled 2 MHz  $\pm 0.01\%$ . Removable by jumper selection when replaced by user clock.

### ENVIRONMENTAL CHARACTERISTICS

Operating Temperature: 0 to 70°C

### EQUIPMENT SUPPLIED

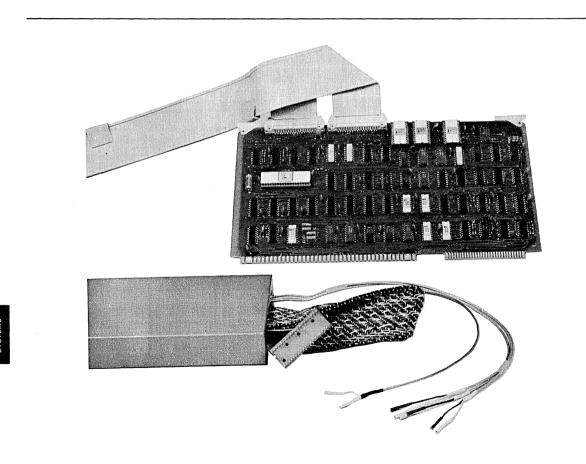

Printed Circuit Modules (2) Interface Cables and Buffer Board Reference Manual Schematic Diagram

ICE-80 allows the user to assign Intellec<sup>®</sup> MDS resident memory and I/O to the user system. Once assigned, the MDS memory or I/O becomes a part of the user system. The user system may operate with all MDS resident memory and I/O, all user provided memory and I/O, or a combination of both.

ICE-80 debug features include the setting of breakpoints in two hardware comparitors which can trap on any memory read, memory write, I/O read or I/O write operation. Breakpoint extensions, which can be logically ANDED with basic breakpoint parameters, include stack operation, M1 fetch state, or a user defined logic signal. When a breakpoint is encountered in the emulation mode, ICE-80 automatically reverts to the interrogation mode. At this time the memory address, data bus contents, and 8080 status byte from the last 44 machine cycles can be displayed along with the actual number of clock cycles which elapsed since program initiation. In the single-step mode, the user may select single-step or multiple single-step operation is executed, and upon completion, all relevant system status may be displayed. In multiple single-step mode, status information is stored at the end of each machine cycle and the next instruction is executed. When multiple single-step operation is terminated upon a software breakpoint or user command, historical information may be retrieved for display or off line analysis.

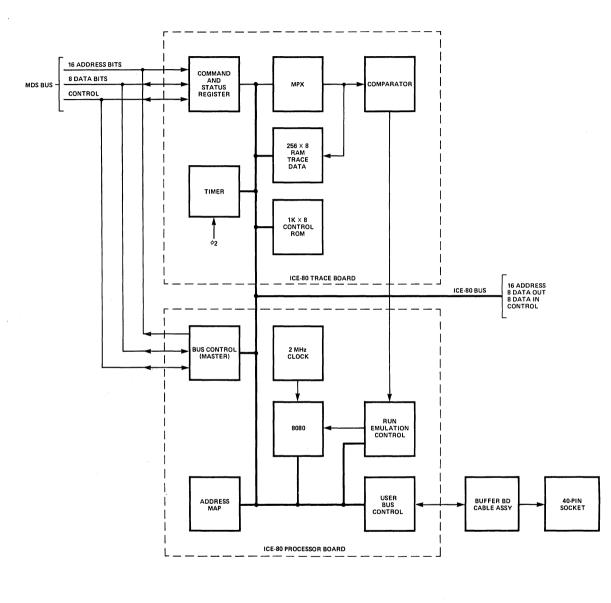

The heart of ICE-80 is a microcomputer system utilizing Intel's 8080 microprocessor as its nucleus. This system communicates with the Intellec MDS host processor via I/O commands. Host processor commands and ICE-80 status are interchanged through registers on the ICE module. ICE-80 and the MDS also communicate through a control block resident in Intellec MDS main memory which contains detailed configuration and status information.

The ICE-80 microcomputer system consists of an Intel 8080 CPU, control memory and data storage memory. The system may be driven with either an internal 2 MHz clock or a user supplied clock. The basic ICE-80 system is augmented by several peripheral devices. An 8-bit command register receives Intellec MDS commands and an 8-bit status register provides ICE-80 systems status information to the Intellec MDS. Bus control logic allows the ICE-80 processor to assume control of the Intellec MDS bus as a bus master, when required. A comparitor contains two 24-bit hardware breakpoint registers which provide address and control information associated with breakpoint functions. Finally, buffer/driver circuitry, located in circuit board in the ICE-80 cable, insures that data transmission between the ICE-80 and user system meets the capacitive loading and input current requirements for the 8080.

**ICE-80**

**ICE-80 BLOCK DIAGRAM**

EVELOPMEN SYSTEMS

## intel

### MDS-ICE-30 3000 SERIES IN-CIRCUIT EMULATOR

Extends the Intellec<sup>®</sup> MDS diagnostic capabilities into user configured systems allowing in-circuit emulation of the user system's 3001 MCU

Direct Intellec MDS connection to the user configured system is achieved via an external cable with 3001 compatible 40-pin connector

Provides for the display of all 3001 address, status, and control lines for the current micro-instruction executed

Allows for single step microprogram execution

Presets the 9-bit 3001 Microprogram Address Register and set two independent breakpoints on micro-instruction addresses generated by 3001

Allows two independent breakpoints to be set on the logical combination of any three TTL compatible signals in the user system via three logic probes

ICE-30 is an Intellec<sup>®</sup> MDS resident module that provides the user with direct in-circuit emulation of the 3001 Microprogram Control Unit (MCU) and complete control over the execution of user developed microprograms. Through in-circuit emulation, the designer is able to set micro-program address breakpoints, single step micro-program execution and monitor all of the address, status, and control lines of the 3001.

ICE-30 Module Board with External Cable and 40 Pin Connector

| A.C. | CHAR | ACTERISTICS | $T_A = 0^{\circ}C$ to 55°C, $V_{CC} = 5.0V \pm 5\%$ |

|------|------|-------------|-----------------------------------------------------|

|      |      |             |                                                     |

| SYMBOL                                                                   | PARAMETER                                                                                                                                                                                      | MIN                  | түр <sup>(1)</sup> | МАХ | UNIT                 |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|-----|----------------------|

| t <sub>CY</sub> <sup>(2)</sup>                                           | Cycle Time                                                                                                                                                                                     | 185                  | 120                |     | ns                   |

| twp                                                                      | Clock Pulse Width                                                                                                                                                                              | 35                   | 20                 |     | ns                   |

| tcs                                                                      | Clock Pulse Separation                                                                                                                                                                         | 150                  |                    |     |                      |

| <sup>t</sup> sғ<br><sup>t</sup> sқ<br><sup>t</sup> sх<br><sup>t</sup> sı | Control and Data Input Set-Up Times:<br>LD, AC <sub>0</sub> –AC <sub>6</sub><br>FC <sub>0</sub> , FC <sub>1</sub><br>SX <sub>0</sub> –SX <sub>3</sub> , PX <sub>4</sub> –PX <sub>7</sub><br>FI | 13<br>13<br>13<br>13 |                    |     | ns<br>ns<br>ns<br>ns |

| <sup>t</sup> нғ<br><sup>t</sup> нк<br><sup>t</sup> нх<br><sup>t</sup> нı | Control and Data Input Hold Times:<br>LD, AC <sub>0</sub> –AC <sub>6</sub><br>FC <sub>0</sub> , FC <sub>1</sub><br>SX <sub>0</sub> –SX <sub>3</sub> , PX <sub>4</sub> –PX <sub>7</sub><br>FI   | 15<br>15<br>15<br>15 |                    |     | ns<br>ns<br>ns<br>ns |

| <sup>t</sup> co                                                          | Propagation Delay from Clock Input (CLK) to Outputs (MA <sub>0</sub> -MA <sub>8</sub> , FO)                                                                                                    |                      | 90                 | 137 | ns                   |

| <sup>t</sup> KO                                                          | Propagation Delay from Control Inputs $FC_2$ and $FC_3$ to Flag Out (FO)                                                                                                                       |                      | 78                 | 130 | ns                   |

| <sup>t</sup> FO                                                          | Propagation Delay from Control Inputs AC <sub>0</sub> -AC <sub>6</sub> to Latch<br>Outputs (PR <sub>0</sub> -PR <sub>2</sub> )                                                                 |                      | 98                 | 150 | ns                   |

| t <sub>EO</sub>                                                          | Propagation Delay from Enable Inputs EN and ERA to Outputs ( $MA_0-MA_8$ , FO, $PR_0-PR_2$ )                                                                                                   |                      |                    | 50  | ns                   |

| t <sub>FI</sub>                                                          | Propagation Delay from Control Inputs AC <sub>0</sub> -AC <sub>6</sub> to Interrupt<br>Strobe Enable Output (ISE)                                                                              |                      | 86                 | 140 | ns                   |

| <sup>t</sup> мн                                                          | Propagation Delay from Clock Input (CLK) to Breakpoint<br>Match MATCH                                                                                                                          |                      |                    | 158 | ns                   |

NOTES:

(1) Typical values are for  $T_A = 25^{\circ}C$  and nominal supply voltage.

(2)  $t_{CY} = t_{CO} + t_{SF} + t_{WP}$

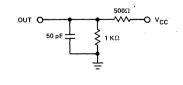

### **TEST CONDITIONS:**

### TEST LOAD CIRCUIT

Input rise and fall times of 10 ns between 0.8 volt and 2.4 volts.

Output load of 10 mA and 50 pF.

Speed measurements are taken at the 1.5 volt level.

| SYMBOL           | PARAMETER          | MIN | ТҮР | MAX | UNIT |

|------------------|--------------------|-----|-----|-----|------|

| C <sub>IN</sub>  | Input Capacitance: |     |     | 50  | pF   |

| С <sub>ОUT</sub> | Output Capacitance |     |     | 50  | pF   |

### D.C. AND OPERATING CHARACTERISTICS T<sub>A</sub> = 0° to 55°C, V<sub>CC</sub> = 5.0V $\pm 5\%$

**ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias         | 5°C  |

|--------------------------------|------|

| Storage Temperature            | ′5°C |

| All Output and Supply Voltages | +7V  |

| All Input Voltages             | 5.5V |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

### D.C. AND OPERATING CHARACTERISTICS

| SYMBOL               | PARAMETER                                                                                                                                    | MIN | түр <sup>(1)</sup> | МАХ               | UNIT           | CONDITIONS                                       |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-------------------|----------------|--------------------------------------------------|

| v <sub>c</sub>       | Input Clamp Voltage<br>(All Input Pins)                                                                                                      |     | -0.8               | -1.5              | V              | I <sub>C</sub> = -12mA                           |

| ۱ <sub>F</sub>       | Input Load Current:<br>CLK Input<br>Logic Probe inputs<br>All other inputs                                                                   |     |                    | 2.0<br>3.0<br>0.4 | mA<br>mA<br>mA | V <sub>F</sub> = 0.45V                           |

| V <sub>IL</sub>      | Input Low Voltage                                                                                                                            |     |                    | 0.8               | V              | V <sub>CC</sub> = 5.0V                           |

| V <sub>IH</sub>      | Input High Voltage                                                                                                                           | 2.0 |                    |                   | v              | V <sub>CC</sub> = 5.0V                           |

| <sup>I</sup> cc      | Power Supply Current                                                                                                                         |     |                    | 0.0               | mA             |                                                  |

| V <sub>OL</sub>      | Output Low Voltage<br>PR <sub>0</sub> -PR <sub>2</sub><br>All other outputs                                                                  |     | 0.35<br>0.35       | 0.45<br>0.45      | V<br>V         | I <sub>OL</sub> = 16mA<br>I <sub>OL</sub> = 40mA |

| V <sub>он</sub>      | Output High Voltage<br>MA <sub>0</sub> –MA <sub>8</sub> , ISE, FO                                                                            | 2.4 | 3.0                |                   | v              | I <sub>OH</sub> = -2mA                           |

| los                  | Output Short Circuit Current<br>MA <sub>0</sub> –MA <sub>8</sub> , ISE, FO                                                                   | -40 |                    | -120              | mA             | $V_{cc} = 5.0V^{(2)}$                            |

| I <sub>O (OFF)</sub> | Off-State Output Current<br>MA <sub>0</sub> –MA <sub>8</sub> , FO<br>MA <sub>0</sub> –MA <sub>8</sub> , FO, PR <sub>0</sub> –PR <sub>2</sub> |     |                    | 100<br>100        | μΑ<br>μΑ       | V <sub>0</sub> = 0.45V<br>V <sub>0</sub> = 5.25V |

NOTES:

(1) Typical values are for  $T_A = 25^{\circ}C$  and nominal supply voltage. (2) Not more than one output should be shorted at one time.

## intel

### SIM-101/SIM-102/SIM-104 ROM SIMULATORS

Extends the powerful Intellec<sup>®</sup> MDS diagnostic capabilities into user-configured systems, allowing simulation of the user system's bipolar ROM/ PROM memory

Direct Intellec MDS connection to the userconfigured system via external cables and Intel's ROM/PROM compatible dual-in-line connectors

Simulates Intel's standard bipolar ROMs and PROMs

Modular design allows the user to configure simulation modules to particular memory space requirements Directly load the ROM Simulator modules from the output of the Intel  $\ensuremath{^{^{(0)}}}$  Cross Microassembler, CROMIS

Access the configured memory space from the console keyboard using simulated ROM addresses

Examine an entire word regardless of length; i.e., 8 bits, 10 bits, 32 bits etc.

Modify an entire word in a single operation regardless of length

Read access time is 130 ns, maximum

Each ROM-SIM module consists of a high-speed, 130-nanosecond 8K bit RAM board, buffer assembly, external cables, and an interactive software program. The ROM-SIM software is a PL/M<sup>T.M.</sup>-80 program that operates in the Intellec MDS to provide the user interface for the ROM-SIM hardware. The software loads BNPF or hexadecimal files such as those generated by the Cross Microassembler System, CROMIS. The ROM-SIM software has the capability to compare and verify microcode, load, display and modify simulated control store contents, and output new BNPF or hexadecimal files from the simulated ROM memory for ROM/PROM programming.

### SPECIFICATIONS

### DC CHARACTERISTICS

$T_A = 0^{\circ}C \text{ to } 55^{\circ}C, V_{CC} = 5.0V \pm 5\%$

|                  | · · · · · · · · · · · · · · · · · · ·                                               | LIMITS |                       |          |                                                    |  |  |

|------------------|-------------------------------------------------------------------------------------|--------|-----------------------|----------|----------------------------------------------------|--|--|

| SYMBOL           | PARAMETER                                                                           | MIN    | MAX                   | UNIT     | TEST CONDITION                                     |  |  |

| I <sub>I</sub>   | Input Load Current<br>Low Order Addr A0-A8<br>High Order Addr A9-AB<br>Chip Selects |        | -1.6<br>-2.1<br>-0.75 | mA       | V <sub>CC</sub> = 5.25V<br>V <sub>IN</sub> = 0.45V |  |  |

| V <sub>OL</sub>  | Output Low Voltage                                                                  |        | 0.45                  | v        | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 16 mA   |  |  |

| Icc              | User Power Supply Sensing                                                           |        | 6                     | mA       | User V <sub>CC</sub> = 5.25V                       |  |  |

| VIL              | Input Low Voltage                                                                   |        | 0.8                   | v        | V <sub>CC</sub> = 5.0V                             |  |  |

| VIH              | Input High Voltage                                                                  | 2.0    |                       | v        | V <sub>CC</sub> = 5.0V                             |  |  |

| V <sub>OH</sub>  | Output High Voltage                                                                 |        | 2.4                   | v        | V <sub>CC</sub> = 4.75V                            |  |  |

| I <sub>SC</sub>  | Output Short Circuit Current at Single Output                                       | -40    | -100                  | mA       | V <sub>O</sub> = 0V, V <sub>CC</sub> = 5V          |  |  |

| I <sub>CEX</sub> | Output Leakage Current                                                              |        | ±50<br>250            | μΑ<br>μΑ | For High Impedance State<br>For Open Collector     |  |  |

### ABSOLUTE MAXIMUM RATINGS

| Temperature Under Bias | 0°C to 55°C     |

|------------------------|-----------------|

| Storage Temperature    | . –20°C to 75°C |

| All Outputs or Supply  | 0.5V to 7.0V    |

| All Inputs             | 1.0V to 5.5V    |

### CAPACITANCE LOAD

| C <sub>IN</sub> | Low Order Address, Chip Selects<br>High Order Address (Coaxial) | 45 pF max.<br>50 pF max. |

|-----------------|-----------------------------------------------------------------|--------------------------|

| COUT            | Data Outputs                                                    | 50 pF max.               |

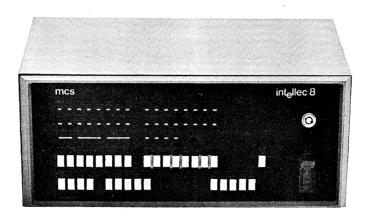

### INTELLEC® 8 / MOD 8 MICROCOMPUTER DEVELOPMENT SYSTEM

Complete Hardware/Software Development System for the design and implementation of 8008 CPU based microcomputer systems

Front panel designer's console provides complete system control and monitoring functions

8K bytes of random access memory (RAM) expandable to 16K bytes

2K bytes of erasable and field programmable read only memory (PROM) expandable to 16K bytes

Self contained PROM programming facility with zero insertion force PROM socket

Four 8-bit input and four 8-bit output ports

Integral asynchronous serial data communications capability at 110, 1200, or 2400 baud

Discrete teletype interface (20mA) current loop)

Standard system software includes a PROM resident system monitor, RAM resident Macro-Assembler and RAM resident text editor

Expansion capability provided for up to 16 standard or custom designed microcomputer modules

The Intellec<sup>®</sup> 8/MOD 8 (imm 8-80A) is a complete, self-contained microcomputer development system designed specifically to support the development and implementation of 8008 CPU based microcomputer systems. Its modular design facilitates the development of both large and small MCS-8 system.

The basic Intellec 8/MOD 8 consists of seven standard microcomputer modules (CPU, RAM, PROM, I/O, PROM Programmer, Front Panel Control) and power supplies enclosed in a finished table top cabinet. The heart of the system is the imm 8-82 central processor module built around Intel's 8008 p-channel 8-bit CPU on a single chip.

The Intellec Development System directly supports up to 16K of memory, eight input ports, twenty-four output ports, and provides expansion capability for custom designed microcomputer modules within the system chassis.

The front panel designer's console provides an easy means of monitoring and controlling system operation, manually moving data to and from memory and input/output devices, setting hardware breakpoints, and executing or debugging programs.

The Intellec 8/MOD 8 has 10K bytes of memory in its basic configuration which can be expanded to 16K bytes within the system chassis. Of the basic 10K bytes of memory, 8K bytes are random access read/write memory located on two imm 6-28 RAM memory modules. This memory can be used for both data and program storage. The remaining 2K bytes of memory are located on the imm 6-26 PROM memory module and contain the Intellec 8/MOD 8 system monitor in eight Intel<sup>®</sup> 1702A erasable and field programmable read only memory chips. Eight additional sockets (2K bytes) are available on the imm 6-26 programmable read only memory chips.

The PROM and RAM memory modules may be used in any combination to make up the 16K of directly addressable memory housed in the system chassis. Facilities are built into these modules so that combinations of RAM, ROM or PROM may be mixed in 256 byte increments.

The self-contained PROM programming module allows Intel 1602A or 1702A PROMs to be programmed and verified directly from RAM or PROM memory.

### INTELLEC<sup>®</sup>8 HIGH SPEED PAPER TAPE READER

Directly compatible with all Intellec<sup>®</sup> 8 Microcomputer Development Systems

20 times faster than standard ASR-33 teletype reader

Data transfer at asynchronous rates in excess of 200 characters per second

3 teletype reader Rack mo

Loads any 8K Intellec  $^{\circledast}$  8 program memory in less than 90 seconds

Rack mountable or stand-alone

The imm8-90 high speed paper tape reader provides all Intellec 8 Microcomputer Development Systems with a high speed paper tape input that is over twenty times faster than the standard ASR-33 teletype reader. This translates into a significantly faster development cycle due to a marked reduction in the time required for repetitive program loading, assembly, and editing operations.

The Intellec 8 monitor software provides two key capabilities which significantly enhance the systems performance of the imm8-90. A general purpose paper tape reader driver is included in the Intellec 8 Monitor. It enables all systems software to utilize the high speed reader features and is caliable by user written application programs. The monitor also provides dynamic I/O reconfiguration permitting instantaneous reassignment of physical devices to logical devices.

### **SPECIFICATIONS**

### TAPE MOVEMENT:

Tape Reading Speed 0 to 200 characters per second asynchronous Tape Stopping Stops "On Character"

TAPE CHARACTERISTICS:

Tapes must be prepared to ANSI  $\times$  3.18 or EMCA 10 Standards for base materials and perforations.

Reads tape of any material with thickness between 0.0027" and 0.0045" with transmissivity less than or equal to 5% (oiled buff paper tape).

Tape loading: in line

Tape width: 1 inch

3 wire input with center conductor (earth ground) tied to chassis. 100, 115, or 127 VAC, single phase at 3.0 amps or 220 or 240 VAC and 1.5 amps; 47 to 63 Hz.

ELECTRICAL CHARACTERISTICS:

### EQUIPMENT SUPPLIED

Paper Tape Reader Reader Cable Reader Flat Cable Fanfold Tape Guide Fanfold Paper Tape Hardware Manual Installation and Operations Guide Fanfold Guide Installation Instructions

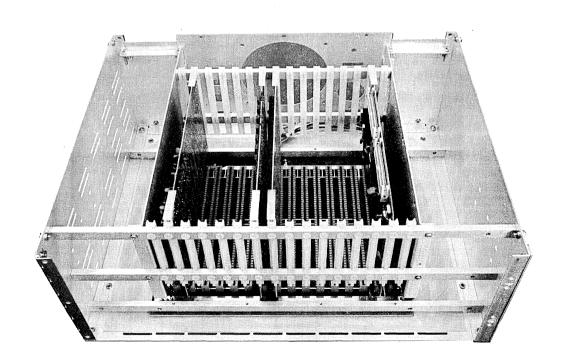

### BAREBONES 80 MICROCOMPUTER SUBSYSTEM

Complete 8080 CPU based microcomputer subsystem composed of Intel microcomputer modules housed in a card cage and interconnected by a printed circuit motherboard containing module sockets

78 instructions including data transfer; decimal, binary, and double precision arithmetic; logical, branch, stack, and I/O  $\!$

Vectored interrupt capability

DMA capability

4K 8-bit bytes of RAM expandable to 16K bytes in standard system and 64K bytes in user modified system

Sockets for 4K 8-bit bytes of PROM expandable to 16K bytes in standard system and 64K bytes in user modified system

Four 8-bit input ports expandable to 16 input ports; four 8-bit output ports expandable to 28 output ports. Expansion to 256 input and 256 output ports in user modified system. All ports are TTL compatible

Integral asynchronous serial data communications capability at 110, 1200, or 2400 baud

Discrete teletype interface (20 mA current loop)

Expansion capability provided for additional 12 Intel or custom microcomputer modules

Rack mountable.

The Barebones 80 (imm8-85) is a complete microcomputer system intended for OEM applications. The subsystem is composed of Intel microcomputer modules which are housed in a card cage and interconnected by a printed circuit motherboard. The chassis has space allocated for OEM power supplies, fan, and front panel.

Four modules are supplied with the basic system and expansion capability exists for 12 additional Intel-supplied or custom modules. Control signals, data and address lines are present at the 12 expansion connectors.

### **BAREBONES 80**

### **SPECIFICATIONS**

### WORD SIZE

Data: 8 bits Instruction: 8, 16, or 24 bits

### MEMORY SIZE

6K bytes expandable to 16K bytes with standard modules, 64K bytes using custom memory modules.