# **ISBC 80/20-4 (or pSBC 80/20-4\*) SINGLE BOARD COMPUTER**

- 8080A CPU used as central processor

- 4K bytes of static read/write memory

- Sockets for up to 8K bytes of erasable reprogrammable or masked read only memory

- 48 programmable parallel I/O lines with sockets for interchangeable line drivers and terminators

- Programmable synchronous/asynchronous RS232C compatible serial interface with fully software selectable baud rate generation

- Full MULTIBUS control logic allowing up to 16 masters to share system bus

- Two programmable 16-bit BCD and binary timers

- Eight-level programmable interrupt control

- Compatible with optional memory and I/O expansion boards

- Auxiliary power bus, memory protect, and power-fail interrupt control logic provided for battery backup RAM requirements

The iSBC 80/20-4 Single Board Computer is a member of Intel's complete line of OEM computer systems which take full advantage of Intel's LSI technology to provide economical, self-contained computer-based solutions for OEM applications. Each ISBC 80/20-4 is a complete computer system on a single 6.75 x 12.00-inch printed circuit card. The CPU, system clock, read/write memory, nonvolatile read only memory, I/O ports and drivers, serial communications interface, priority interrupt logic, two programmable timers, MULTIBUS control logic, and bus expansion drivers all reside on each board.

## **FUNCTIONAL DESCRIPTION**

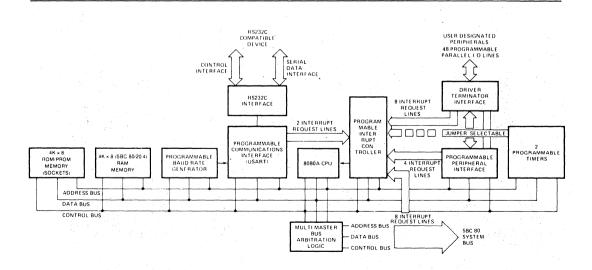

Intel's powerful 8-bit n-channel MOS 8080A CPU, fabricated on a single LSI chip, is the central processor for the iSBC 80/20-4. The 8080A contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs, providing both single and double precision operators. Minimum instruction execution time is 1.86 microseconds. A block diagram of iSBC 80/20-4 functional components is shown in Figure 1.

# **Memory Addressing**

The 8080A has a 16-bit program counter which allows direct addressing of up to 65,536 bytes of memory. An external stack, located within any portion of read/write memory, may be used as a last-in/first-out storage area for the contents of the program counter, flags, accumulator, and all of the six general purpose registers. A 16-bit stack pointer controls the addressing of this external stack. This stack provides subroutine nesting bounded only by memory size.

## **Memory Capacity**

The iSBC 80/20-4 contains 4K bytes of static read/write memory using Intel low power static RAMs. All on-board RAM read and write operations are performed at maximum processor speed. Power for on-board RAM memory is provided on an auxiliary power bus, and memory protect logic is included for battery backup RAM requirements. Sockets for up to 8K bytes of nonvolatile read only memory are provided on the board. Read only

memory may be added in 1K-byte increments using Intel 2708 erasable and electrically reprogrammable ROMs (EPROMs), or read only memory may be added in 2K-byte increments using Intel 2716 EPROMs. All on-board ROM read operations are performed at maximum processor speed.

#### Parallel I/O Interface

The iSBC 80/20-4 contains 48 programmable parallel I/O lines implemented using two Intel 8255 programmable peripheral interfaces. The system software is used to configure the I/O lines in any combination of the unidirectional input/output, and bidirectional ports indicated in Table 1. Therefore, the I/O interface may be customized to meet specified peripheral requirements. In order to take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence, the flexibility of the I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the required sink current, polarity, and drive/termination characteristics for each application. The 48 programmable I/O lines and signal ground lines are brought out to two 50-pin edge connectors that mate with flat, woven, or round cable.

#### Serial I/O Interface

A programmable communications interface using Intel's 8251 Universal Synchronous/Asynchronous Receiver/Transmitter (USART) is contained on the iSBC

Figure 1. iSBC 80/20 and iSBC 80/20-4 Block Diagram Showing Functional Components

80/20-4 board. A software selectable baud rate generator provides the USART with all common communications frequencies. The USART can be programmed by the system software to select the desired asynchronous or synchronous serial data transmission technique (including IBM Bi-Sync). The mode of operation (i.e., synchronous or asynchronous), data format, control character parity. and baud rate are all under program control. The 8251 provides full duplex, double-buffered transmit and receive capability. Parity, overrun, and framing error detection are all incorporated in the USART. The RS232C compatible interface on each board, in conjunction with the USART, provides a direct interface to RS232C compatible terminals, cassettes, and asynchronous and synchronous modems. The RS232C command lines, serial data lines, and signal ground line are brought out to a 26-pin edge connector that mates with RS232C compatible flat or round cable.

# **Multimaster Capability**

The iSBC 80/20-4 is a full computer on a single board with resources capable of supporting the majority of OEM system requirements. For those applications requiring additional processing capacity and the benefits of multiprocessing (i.e., several CPUs and/or controllers logically share system tasks with communication over the system bus), the iSBC 80/20-4 provides full MULTIBUS arbitration control logic. This control logic allows up to three iSBC 80/20-4 or high speed controllers to share the system bus in serial (daisy chain) priority fashion, and up to 16 masters may share the system bus with the addition of an external priority network. Once

bus control is attained, a bus bandwidth of up to 5M bytes/sec may be achieved.

The bus controller provides its own clock which is derived independently from the processor clock. This allows different speed controllers to share resources on the same bus, and transfers via the bus proceed asynchronously. Thus, transfer speed is dependent on transmitting and receiving devices only. This design prevents slow master modules from being handicapped in their attempts to gain control of the bus, but does not restrict the speed at which faster modules can transfer data via the same bus. Once a bus request is granted, single or multiple read/write transfers can proceed at a maximum rate of 5 million data words per second. The most obvious applications for the master-slave capabilities of the bus are multiprocessor configurations, high speed direct-memory-access (DMA) operations and high speed peripheral control, but are by no means limited to these three.

# **Programmable Timers**

The iSBC 80/20-4 board provides three fully programmable and independent BCD and binary 16-bit interval timers/event counters utilizing an Intel 8253 Programmable Interval Timer. Two of these timers/counters are available to the systems designer to generate accurate time intervals under software control. Routing of these counters is jumper selectable. Each may be independently routed to the programmable interrupt controller, the I/O line drivers and terminators, or outputs from the 8255 programmable peripheral interfaces. The third interval timer in the 8253 provides the programmable baud

|      |                | Mode of Operation |                      |         |                   |               |                |

|------|----------------|-------------------|----------------------|---------|-------------------|---------------|----------------|

|      |                |                   | Unidirec             |         |                   |               |                |

| Port | Lines<br>(qty) | Lines Input       |                      | Ou      | tput              | Bidirectional | Control        |

|      | (413)          | Unlatched         | Latched &<br>Strobed | Latched | Latched & Strobed |               |                |

| 1    | 8              | X                 | X                    | Х       | X                 | X             |                |

| 2    | 8              | X                 | Х                    | Х       | X                 |               |                |

| 3    | 4              | X                 |                      | Х       |                   |               | X <sup>1</sup> |

|      | 4              | X                 |                      | Х       |                   |               | X <sup>1</sup> |

| 4    | 8              | X                 | Х                    | Х       | Х                 | X             |                |

| 5    | . 8            | X                 | Χ .                  | Х       | Х                 |               |                |

| 6    | 4              | X                 |                      | Х       |                   |               | X <sup>2</sup> |

|      | 4              | X                 |                      | X       |                   | *             | X <sup>2</sup> |

Table 1. Input/Output Port Modes of Operation

#### Note

- 1. Part of port 3 must be used as a control port when either port 1 or port 2 are used as a latched and strobed input or a latched and strobed output port or port 1 is used as a bidirectional port.

- 2. Part of port 6 must be used as a control port when either port 4 or port 5 are used as a latched and strobed input or a latched and strobed output port or port 4 is used as a bidirectional port.

rate generator for the iSBC 80/20-4 RS232C USART serial port. In utilizing the iSBC 80/20-4, the systems designer simply configures, via software, each timer independently to meet system requirements. Whenever a given time delay or count is needed, software commands to the programmable timers/event counters select the desired function. Seven functions are available, as shown in Table 2. The contents of each counter may be read at any time during system operation with simple read operations for event counting applications, and special commands are included so that the contents of each counter can be used "on the fly".

**Table 2. Programmable Timer Functions**

| Function                        | Operation                                                                                                                                                                                                                                              |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt on<br>terminal count  | When terminal count is reached, an interrupt request is generated. This function is extremely useful for generation of real-time clocks.                                                                                                               |

| Programmable one-shot           | Output goes low upon receipt of an external trigger edge or software command and returns high when terminal count is reached. This function is retriggerable.                                                                                          |

| Rate<br>generator               | Divide by N counter. The output will go low for one input clock cycle, and the period from one low-going pulse to the next is N times the input clock period.                                                                                          |

| Square-wave<br>rate generator   | Output will remain high until one-<br>half the count has been completed,<br>and go low for the other half of the<br>count.                                                                                                                             |

| Software<br>triggered<br>strobe | Output remains high until software loads count (N). N counts after count is loaded, output goes low for one input clock period.                                                                                                                        |

| Hardware<br>triggered<br>strobe | Output goes low for one clock<br>period N counts after rising edge on<br>counter trigger input. The counter<br>is retriggerable.                                                                                                                       |

| Event counter                   | On a jumper selectable basis, the clock input becomes an input from the external system. CPU may read the number of events occurring after the counting "window" has been enabled or an interrupt may be generated after N events occur in the system. |

#### Interrupt Capability

Operation and Priority Assignments — An Intel 8259 Programmable Interrupt Controller (PIC) provides vectoring for eight interrupt levels. As shown in Table 3, a selection of four priority processing modes is available to the systems designer so that the manner in which requests are processed may be configured to match system requirements. Operating mode and priority

assignments may be reconfigured dynamically via software at any time during system operation. The PIC accepts interrupt requests from the programmable parallel and serial I/O interfaces, the programmable timers, the system bus, or directly from peripheral equipment. The PIC then determines which of the incoming requests is of the highest priority, determines whether this request is of higher priority than the level currently being serviced, and if appropriate, issues an interrupt to the CPU. Any combination of interrupt levels may be masked through storage via software, of a single byte to the interrupt register of the PIC.

Table 3. Programmable Interrupt Modes

| Mode              | Operation                                                                                                                     |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Fully<br>nested   | Interrupt request line priorities fixed at 0 as highest, 7 as lowest.                                                         |

| Auto-<br>rotating | Equal priority. Each level, after receiving service, becomes the lowest priority level until the next interrupt occurs.       |

| Specific priority | System software assigns lowest priority level. Priority of all other levels based in sequence numerically on this assignment. |

| Polled            | System software examines priority-en-<br>coded system interrupt status via inter-<br>rupt status register.                    |

Interrupt Addressing — The PIC generates a unique memory address for each interrupt level. These addresses are equally spaced at intervals of 4 or 8 (software selectable) bytes. This 32- or 64-byte block may be located to begin at any 32- or 64-byte boundary in the 65,536-byte memory space. A single 8080 jump instruction at each of these addressed then provides linkage to locate each interrupt service routine independently anywhere in memory.

Interrupt Request Generation — Interrupt requests may originate from 26 sources. Four jumper selectable interrupt requets can be automatically generated by the programmable peripheral interface when a byte of information is ready to be transferred to the CPU (i.e., input buffer is full) or a byte of information has been transferred to a peripheral device (i.e., output buffer is empty). Two jumper selectable interrupt requests can be automatically generated by the USART when a character is ready to be transfer to the CPU (i.e., receive channel buffer is full), or a character is ready to be transmitted (i.e., transmit channel data buffer is empty). A jumper selectable request can be generated by each of the programmable timers. Nine additional interrupt request lines are available to the user for direct interface to user designated peripheral devices via the system bus, and eight interrupt request lines may be jumper routed directly from peripherals via the parallel I/O driver/terminator section.

**Power-Fail Control** — Control logic is also included for generation of a power-fail interrupt which works in conjunction with the AC-low signal from iSBC 635 Power Supply or equivalent.

# **Expansion Capabilities**

Memory and I/O capacity may be expanded and additional functions added using Intel MULTIBUS compatible expansion boards. High speed integer and floating-point arithmetic capabilities may be added by using the iSBC 310A High Speed Mathematics Unit. Memory may be expanded to 65,536 bytes by adding user specified combinations of RAM boards, EPROM boards, or combination boards. Input/output capacity may be increased by adding digital I/O and analog I/O expansion boards. Mass storage capability may be achieved by adding single or double density diskette controllers as subsystems. Modular expandable backplanes and cardcages are available to support multiboard systems.

#### Real-Time Software

The iSBC 80/20-4 is totally compatible with Intel's iRMX 80 Real-Time Multi-Tasking Executive. iSBC 80/20-4 based user programs (tasks) can take advantage of the iRMX 80 executive to do all necessary scheduling, intertask communication, and memory space allocation. iRMX 80 also provides standard I/O support software such as disk file handling, Intel analog board handling, and terminal handling.

## System Development Capability

The development cycle of iSBC 80/20-4 based products may be significantly reduced using an Intellec micro-computer development system. The resident macro-assembler, text editor, and system monitor greatly simplify the design, development, and debug of iSBC 80/20-4 system software. An optional diskette operating system provides a relocating macroassembler, a relocating loader and linkage editor, and a library manager. A unique in-circuit emulator (ICE-80) option provides the capability of developing and debugging

software directly on the iSBC 80/20-4 single board computer.

# **Programming Capability**

PL/M-80 — Intel's high level programming language, PL/M, is also available as a resident Intellec microcomputer development system option. PL/M provides the capability to program in a natural, algorithmic language and eliminates the need to manage register usage or allocate memory. PL/M programs can be written in a much shorter time than assembly language programs for a given application.

FORTRAN-80 — For applications requiring computational and formatted I/O capabilities, the high level FORTRAN-80 programming language is also available as a resident option of the Intellec system. The FORTRAN compiler produces relocatable object code that may be easily linked with PL/M or assembly language program modules. This gives the user a wide flexibility in developing software.

BASIC-80 - A high level language interpreter with extended disk capabilities which operates under the RMX/80 Real-Time Multi-Tasking Executive and translates BASIC-80 source programs into an internally executable form. This language interpreter, provided as a set of linkable object modules, is ideally suited to the OEM who requires a pass through programming lanquage. The BASIC-80 programs may be created, stored and interpreted on the iSBC 80 based system. The BASIC-80 language has a rich complement of statements, functions, and commands to program applications requiring a full range of 1) string manipulation and disk I/O for data processing, 2) single and double precision floating point and array handling for numeric analysis, or 3) port I/O with mask operations controlled through bit-wise Boolean logical operators.

# **SPECIFICATIONS**

#### Word Size

Instruction — 8, 16, or 24 bits Data — 8 bits

#### **Cvcle Time**

Basic Instruction Cycle —  $1.86~\mu s$

Note

Basic instruction cycle is defined as the fastest instruction (i.e., four clock cycles).

## **Memory Addressing**

**On-Board ROM/EPROM** — 0-0FFF (2708) or 0-1FFF (2716)

On-Board RAM — 4K bytes ending on a 16K boundary (e.g., 3FFF<sub>H</sub>, 7FFF<sub>H</sub>, BFFF<sub>H</sub>, . . . FFFF<sub>H</sub>)

## **Memory Capacity**

On-Board ROM/EPROM - 8K bytes (sockets only)

On-Board RAM - 4K bytes

Off-Board Expansion — Up to 65,536 bytes in user specified RAM, ROM, and EPROM

#### Note

ROM/EPROM may be added in 1K or 2K-byte increments.

# I/O Addressing

On-Board Programmable I/O (see Table 1)

| Port    | 8255 No. 1 |    | 8255 No. 2 |    | 8255<br>No. 1 | 8255<br>No. 2 | USART      |    |    |         |

|---------|------------|----|------------|----|---------------|---------------|------------|----|----|---------|

|         | 1          | 2  | 3          | 4  | 5             | 6             | Control Co |    |    | Control |

| Address | E4         | E5 | E6         | E8 | E9            | EΑ            | E7 .       | EB | EC | ED      |

# I/O Capacity

Parallel - 48 programmable lines (see Table 1)

Note

Expansion to 504 input and 504 output lines can be accomplished using optional I/O boards.

## **Serial Communications Characteristics**

Synchronous — 5-8 bit characters; internal or external character synchronization; automatic sync insertion

Asynchronous — 5-8 bit characters; break character generation; 1, 1½, or 2 stop bits; false start bit detection

#### **Baud Rates**

| Frequency (kHz)       | Baud Rate (Hz) |              |      |  |  |

|-----------------------|----------------|--------------|------|--|--|

| (Software Selectable) | Synchronous    | Asynchronous |      |  |  |

|                       |                | ÷ 16         | ÷ 64 |  |  |

| 153.6                 |                | 9600         | 2400 |  |  |

| 76.8                  | _              | 4800         | 1200 |  |  |

| 38.4                  | 38400          | 2400         | 600  |  |  |

| 19.2                  | 19200          | 1200         | 300  |  |  |

| 9.6                   | 9600           | 600          | 150  |  |  |

| 4.8                   | 4800           | 300          | 75   |  |  |

| 2.4                   | 2400           | 150          | –    |  |  |

| 1.76                  | 1760           | 110          | _    |  |  |

#### Note

Frequency selected by I/O write of appropriate 16-bit frequency factor to baud rate register.

## Register Address (hex notation, I/O address space)

DE Baud rate register

Note

Baud rate factor (16 bits) is loaded as two sequential output operations to same address (DE<sub>H</sub>).

## Interrupts

Register Addresses (hex notation, I/O address space)

DA Interrupt request register

DA In-service register

DB Mask register

DA Command register

DB Block address register

DA Status (polling register)

Note

Several registers have the same physical address; sequence of access and one data bit of control word determine which register will respond.

#### Timers

Register Addresses (hex notation, I/O address space)

DF Control register

DC Timer 1

DD Timer 2

Note

Timer counts loaded as two sequential output operations to same address, as given.

## Input Frequencies

| Reference                                   | Event Rate  |

|---------------------------------------------|-------------|

| 1.0752 MHz ± 10% (0.930 µs period, nominal) | 1.1 MHz max |

#### Note

Maximum rate for external events in event counter function.

#### **Output Frequencies/Timing Intervals**

| Function                        | Single Tin | ner/Counter | Dual Timer/Counter (Two Timers Cascaded) |            |  |  |

|---------------------------------|------------|-------------|------------------------------------------|------------|--|--|

|                                 | Min        | Max         | Min                                      | Max        |  |  |

| Real-time<br>interrupt          | 1.86 µs    | 60.948 ms   | 3.72 μs                                  | 1.109 hr   |  |  |

| Programmable one-shot           | 1.86 μs    | 60.948 ms   | 3.72 µs                                  | 1.109 hr   |  |  |

| Rate generator                  | 16.407 Hz  | 537.61 kHz  | 0.00025 Hz                               | 268.81 kHz |  |  |

| Square-wave rate generator      | 16.407 Hz  | 537.61 kHz  | 0.00025 Hz                               | 268.31 kHz |  |  |

| Software<br>triggered<br>strobe | 1.86 μs    | 60.948 ms   | 3.72 μs                                  | 1.109 hr   |  |  |

| Hardware<br>triggered<br>strobe | 1.86 μs    | 60.948 ms   | 3.72 μs                                  | 1.109 hr   |  |  |

#### Interfaces

Bus - All signals TTL compatible

Parallel I/O — All signals TTL compatible Interrupt Requests — All TTL compatible

Timer - All signals TTL compatible

Serial I/O - RS232C compatible, data set configuration

# System Clock (8080A CPU)

2.1504 MHz ± 0.1%

## **Auxiliary Power**

An auxiliary power bus is provided to allow separate power to RAM for systems requiring battery backup of read/write memory. Selection of this auxiliary RAM power bus is made via jumpers on the board.

## **Memory Protect**

An active-low TTL compatible memory protect signal is brought out on the auxiliary connector which, when asserted, disables read/write access to RAM memory on the board. This input is provided for the protection of RAM contents during system power-down sequences.

#### Connectors

| Interface                 | Double-<br>Sided Pins<br>(qty) | Centers<br>(in.) | Mating Connectors*                                                                                                                                                 |

|---------------------------|--------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MULTIBUS<br>System<br>Bus | 86                             | 0.156            | ELFAB BS1562043PBB<br>Viking 2KH43/9AMK12<br>Soldered PCB Mount<br>EDAC 337086540201<br>ELFAB BW1562D43PBB<br>EDAC 337086540202<br>ELFAB BW1562A43PBB<br>Wire Wrap |

| Auxiliary<br>Bus          | 60                             | 0.100            | EDAC 345060524802<br>ELFAB BS1020A30PBB<br>EDAC 345060540201<br>ELFAB BW1020D30PBB<br>Wire Wrap                                                                    |

| Parallel I/O              | 50                             | 0.100            | 3M 3415-001 Flat Crimp<br>GTE Sylvania<br>6AD01251A1DD<br>Soldered                                                                                                 |

| Serial I/O                | 26                             | 0.100            | AMP 15837151<br>EDAC 345026520202<br>PCB Soldered<br>3M 3462-0001<br>AMP 88373-5 Flat Crimp                                                                        |

<sup>\*</sup>Note: Connectors compatible with those listed may also be used.

## **Line Drivers and Terminators**

I/O Drivers — The following line drivers are all compatible with the I/O driver sockets on the iSBC 80/20-4.

| Driver | Characteristic | Sink Current (mA) |

|--------|----------------|-------------------|

| 7438   | I,OC           | 48                |

| 7437   | , I            | 48                |

| 7432   | NI             | 16                |

| 7426   | I,OC           | 16                |

| 7409   | NI,OC          | 16                |

| 7408   | NI             | 16                |

| 7403   | I,OC           | 16                |

| 7400   | 1              | 16                |

#### Note

I = inverting; NI = non-inverting; OC = open collector.

Ports 1 and 4 have 20 mA totem-pole bidirectional drivers and 1  $k\Omega$  terminators.

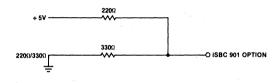

I/O Terminators —  $220\Omega/330\Omega$  divider or 1 k $\Omega$  pull-up

#### **Bus Drivers**

| Driver   | Characteristic | Sink Current (mA) |  |  |

|----------|----------------|-------------------|--|--|

| Data     | Tri-state      | 50                |  |  |

| Address  | Tri-state      | 50                |  |  |

| Commands | Tri-state      | 32                |  |  |

# **Physical Characteristics**

**Width** — 12.00 in. (30.48 cm)

Height - 6.75 in. (17.15 cm)

Depth — 0.50 in. (1.26 cm)

Weight - 14 oz (397.6 gm)

# **Electrical Characteristics**

#### **DC Power Requirements**

| Voltage<br>(±5%)        | Without<br>PROM <sup>1</sup><br>(max) | With 4K<br>PROM <sup>2</sup><br>(max) | With<br>ISBC 530 <sup>3</sup><br>(max) | RAM<br>Only <sup>4</sup><br>(max) | With 8K<br>PROM <sup>5</sup><br>(max) |

|-------------------------|---------------------------------------|---------------------------------------|----------------------------------------|-----------------------------------|---------------------------------------|

| V <sub>CC</sub> = +5V   | I <sub>CC</sub> = 4.0A                | 4.9A                                  | 4.9A                                   | 1.1A                              | 5.2A                                  |

| V <sub>DD</sub> = + 12V | I <sub>DD</sub> = 90 mA               | 350 mA                                | 450 mA                                 | -                                 | 90 mA                                 |

| V <sub>BB</sub> = -5V   | I <sub>BB</sub> =2 mA                 | 180 mA                                | 180 mA                                 | -                                 | 2 mA                                  |

| V <sub>AA</sub> = - 12V | I <sub>AA</sub> = 20 mA               | 20 mA                                 | 120 mA                                 | _                                 | 20 mA                                 |

#### Notes

- 1. Does not include power required for optional PROM, I/O drivers, and I/O terminators.

- 2. With four 2708 EPROMs and  $220\Omega/330\Omega$  input terminators installed for 32 I/O lines, all terminator inputs low.

- 3. With four 2708 EPROMs,  $220\Omega/330\Omega$  input terminators installed for 32 I/O lines, all terminator inputs low, and iSBC 530 Teletypewriter Adapter drawing power from serial port connector.

- 4. RAM chips powered via auxiliary power bus.

- 5. With four 8716 EPROMs and eight 220 $\Omega/330\Omega$  input terminators installed, all terminator inputs low.

## **Environmental Characteristics**

Operating Temperature — 0°C to 55°CC

## **Reference Manual**

**9800317D** — iSBC 80/20-5 Hardware Reference Manual (NOT SUPPLIED)

Reference manuals are shipped with each product only if designated SUPPLIED (see above). Manuals may be ordered from any Intel sales representative, distributor office or from Intel Literature Department, 3065 Bowers Avenue, Santa Clara, California 95051.

# ORDERING INFORMATION

## Part Number

# Description

SBC 80/20-4

Single Board Computer with 4K bytes

RAM