# iSBC 569 INTELLIGENT DIGITAL CONTROLLER

- Single board digital I/O controller with up to four microprocessors to share the digital input/output signal processing

- 3 MHz 8085A central control processor

- Three sockets for 8041/8741A Universal Peripheral Interface (UPI-41A) for distributed digital I/O processing, such as:

- Industrial signal processor

(iSBC 941)

- Custom programmed 8041A/8741A

- Three operational modes

- Stand-along digital controller

- MULTIBUS master

- Intelligent slave (slave to MULTIBUS master)

- 2K bytes of dual port static read/write memory

- Sockets for up to 8K bytes of Intel 2758, 2716, 2732 erasable programmable read only memory

- 48 programmable parallel I/O lines with sockets for interchangeable line drivers or terminators

- Three programmable counters

- 12 levels of programmable interrupt control

- Single +5V supply

- MULTIBUS standard control logic compatible with optional iSBC 80 and iSBC 86 CPU, memory, and I/O expansion boards

The Intel iSBC 569 Intelligent Digital Controller is a single board computer (8085A based) with sockets for three 8041A/8741A Universal Peripheral Interface chips (UPI-41A). The I/O processing algorithm may be tailored to application requirements using designer selected combinations of standard Intel industrial signal processors (e.g., iSBC 941) or user programmed UPI-41A processors. These devices may be used to offload the 8085A processor from time consuming tasks such as pulse counting, event sensing, and parallel or serial digital I/O data formatting with error checking and handshaking. The iSBC 569 board is a complete digital controller with up to four processors on a single 6.75 inches x 12.00 inches (17.15cm x 30.48cm) printed circuit board. The 8085A CPU, system clock, read/write memory, non-volatile memory, priority interrupt logic, programmable timers, MULTIBUS control and interface logic, optional UPI processors and optional line driver and terminators all reside on one board.

# **FUNCTIONAL DESCRIPTION**

### Intelligent Digital Controller

Three modes of operation — the iSBC 569 Intelligent Digital Controller is capable of operating in one of three modes; stand alone controller, bus master, or intelligent slave.

Stand alone controller — the iSBC 569 board may function as a stand alone, single board controller with CPU, memory, and I/O elements on a single board. Five volt (+5VDC) only operation allows configuration of low cost controllers with only a single power supply voltage. The on-board 2K bytes RAM and up to 16K bytes ROM/EPROM, as well as the assistance of three UPI-41A processors, allow significant digital I/O control from a single board.

Bus master — in this mode of operation, the iSBC 569 controller may interface with and control iSBC expansion memory and I/O boards, or even other iSBC 569 Intelligent Digital Controllers configured as intelligent slaves (but no additional bus masters).

Intelligent slave — the iSBC 569 controller can perform as an intelligent slave to any 8- or 16-bit MULTIBUS master CPU by offloading the master of digital control related tasks. Preprocessing of data for the master is controlled by the on-board 8085A CPU which coordinates up to three UPI-41A processors. Using the iSBC 569 board as an intelligent slave, multi-channel digital control can be managed entirely on-board, freeing a system master to perform other system functions. The dual port RAM memory allows the iSBC 569 controller to process and store data without MULTIBUS memory contention.

### Simplified Programming

By using Intel UPI-41A processors for common tasks such as counting, sensing change of state, printer control and keyboard scanning/debouncing, the user frees up time to

work on the more important application programming of machine or process optimization. Controlling the Intel UPI-41A processors becomes a simple task of reading or writing command and data bytes to or from the data bus buffer register on the UPI device. Programming the iSBC 941 Industrial Digital Processor to produce a pulse output, for example, is as simple as sending command and parameter bytes indicating initialization, pulse output selection, period and delay parameters, followed by a command to begin execution.

### **Central Processing Unit**

A powerful Intel 8085A 8-bit CPU, fabricated on a single LSI chip, is the central processor for the iSBC 569 TM controller. The six general purpose 8-bit registers may be addressed individually or in pairs, providing both single and double precision operations. The program counter can address up to 64K bytes of memory using iSBC expansion boards. The 16-bit stack pointer controls the addressing of an external stack. This stack provides sub-routine nesting bounded only by memory size. The minimum instruction execution time is 1.30 microseconds. The 8085A CPU is software compatible with the Intel 8080A CPU.

### **Bus Structure**

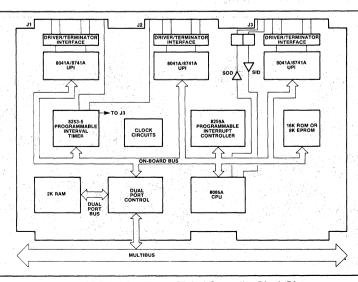

The iSBC 569 Intelligent Digital Controller utilizes a triple bus architecture concept. An internal bus is used for onboard memory and I/O operations. A MULTIBUS interface is available to provide access for all external memory and I/O operations. A dual port bus with controller enables access via the third bus to 2K bytes of static RAM from either the on-board CPU or a system master. Hence, common data may be stored in on-board memory and may be accessed either by the on-board CPU or by system masters. A block diagram of the iSBC 569 functional components is shown in Figure 1.

Figure 1. iSBC 569 Intelligent Digital Controller Block Diagram

### **RAM Capacity**

The iSBC 569 board contains 2K bytes of read/write memory using Intel 2114 static RAMs. RAM accesses may occur from either the iSBC 569 controller or from any other bus master interfaced via the MULTIBUS system bus. The iSBC 569 board provides addressing jumpers to allow the on-board RAM to reside within a one megabyte address space when accessed via the system bus. In addition, a switch is provided which allows the user to reserve a 1K byte segment of on-board RAM for use by the 8085A CPU. This reserved RAM space is not accessible via the system bus and does not occupy any system address space.

# **EPROM/ROM Capacity**

Two sockets for up to 16K bytes of nonvolatile read only memory are provided on the iSBC 569 board. Nonvolatile memory may be added in 1K-byte increments up to a maximum of 2K bytes using Intel 2758 erasable and electrically reprogrammable ROMs (EPROMs); in 2K-byte increments up to a maximum of 4K bytes using Intel 2316 ROMs or 2716 EPROMs; in 4K byte increments up to 8K bytes maximum using Intel 2732 EPROMs; or in 8K-byte increments up to 16K bytes maximum using Intel 2364 ROMs (both sockets must contain same type ROM/EPROM). All on-board ROM/EPROM operations are performed at maximum processor speed.

### Universal Peripheral Interfaces (UPI-41A)

The iSBC 569 Intelligent Digital Controller board provides three sockets for user supplied Intel 8041A/8741A Universal Peripheral Interface (UPI-41A) chips. Sockets are also provided for the associated line drivers and terminators for the UPI I/O ports. The UPI-41A processor is a single chip microcomputer containing a CPU, 1K bytes of ROM (8041A) or EPROM (8741A), 64 bytes of RAM, 16 programmable I/O lines, and an 8-bit timer/event counter. Special interface registers included in the chip allow the UPI-41A processor to function as a slave processor to the iSBC 569 controller board's 8085A CPU. The UPI processor allows the user to specify algorithms for controlling peripherals directly thereby freeing the 8085A for other system functions. For additional information, including UPI-41A instructions. refer to the UPI-41 User's Manual (Manual No. 9800504).

### Industrial Digital Processor (iSBC 941)

The iSBC 941 Industrial Digital Processor is a 40-pin DIP device which provides the user with easy-to-use processing of digital input and output signals desired in many industrial automation environments. One of nine digital I/O functions can be selected at any one time for measuring, counting, or controlling up to 16 separate I/O lines. An additional eight utility commands allow reading or setting the condition of unused I/O lines. Simplex serial input and output modes can assemble or disassemble bytes transmitted asynchronously over TTL lines, including insertion and deletion of start/stop bits. The iSBC 941 processor plugs into any of the three UPI-41A sockets on the iSBC 569 board. Simple programming commands from the master 8085A processor can thus implement up to 48 lines of preprocessed digital I/O signals. For specific commands and further information, refer to the iSBC 941 Data Sheet in this document.

### **Programmable Timers**

The iSBC 569 Intelligent Digital Controller board provides three independently programmable interval timer/counters utilizing one Intel 8253 Programmable Interval Timer (PIT). The Intel 8253 PIT provides three 16-bit BCD or binary interval timer/counters. Each timer may be used to provide a time reference for each UPITM processor or for a group of UPI processors. The output of each timer also connects to the 8259A Programmable Interrupt Controller (PIC) providing the capability of timed interrupts. All gate inputs, clock inputs, and timer outputs of the 8259 PIT are available at the I/O ports for external access.

Timer Functions — In utilizing the iSBC 569 controller, the systems designer simply configures, via software, each timer to meet systems requirements. The 8253 PIT modes are listed in Table 1. The contents of each counter may be read at any time during system operation with simple read operations for event counting applications. The contents of each counter can be read "on-the-fly" for time stamping events or time clock referenced program initiations.

Table 1. 8253 Programmable Timer Functions

| Function                        | Operátion                                                                                                                                                                                                                                              |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt on terminal count     | When terminal count is reached, an interrupt request is generated.                                                                                                                                                                                     |

| Programmable<br>one-shot        | Output goes low upon receipt of<br>an external trigger edge or soft-<br>ware command and returns high<br>when terminal count is reached.<br>This function is retriggerable.                                                                            |

| Rate<br>generator               | Divide by N counter. The output will go low for one input clock cycle, and the period from one lowgoing pulse to the next is N times the input clock period.                                                                                           |

| Square-wave rate generator      | Output will remain high until one-<br>half the count has been com-<br>pleted, and go low for the other<br>half of the count.                                                                                                                           |

| Software<br>triggered<br>strobe | Output remains high until soft-<br>ware loads count (N). N counts<br>after count is loaded, output goes<br>low for one input clock period.                                                                                                             |

| Hardware<br>triggered<br>strobe | Output goes low for one clock period N counts after rising edge on counter trigger input. The counter is retriggerable.                                                                                                                                |

| Event counter                   | On a jumper selectable basis, the clock input becomes an input from the external system. CPU may read the number of events occurring after the counting "window" has been enabled or an interrupt may be generated after N counts occur in the system. |

# Interrupt Capability

The iSBC 569 Intelligent Digital Controller provides interrupt service for up to 12 interrupt sources. Any of the 12 sources may interrupt the on-board processor. Four interrupt levels are handled directly by the 8085A CPU and eight levels are serviced from an Intel 8259A Programmable Interrupt Controller (PIC) routing an interrupt request output to the INTR input of the 8085A.

8085A Interrupt — Each of four direct 8085A interrupt inputs has a unique vector memory address. An 8085A jump instruction at each of these addresses then provides software linkage to interrupt service routines located independently anywhere in the memory.

**8259A Interrupts** — The eight interrupt sources originate from both on-board controller functions and the system bus:

UPI-41A Processors — one interrupt from each of three UPI processor sockets.

8253 PIT — one interrupt from each of three timer outputs. MULTIBUS System Bus — one of eight MULTIBUS interrupt lines may be jumpered to either of two 8259A PIC interrupt inputs.

Programmable Reset — The iSBC 569 Intelligent Digital Controller board has a programmable output latch used to control on-board functions. Three of the outputs are connected to separate UPI-41A RESET inputs. Thus, the user can reset any or all of the UPI-41A processors under software control. A fourth latch output may be used to generate an interrupt request onto the MULTIBUS interrupt lines. A fifth latch output is connected to a lightemitting diode which may be used for diagnostic purposes.

### **Expansion Capabilities**

When the iSBC 569 controller is used as a single board digital controller, memory and I/O capacity may be expanded using Intel MULTIBUS compatible expansion boards. In this mode, no other bus masters may be in the system. Memory may be expanded to a 64K byte capacity by adding user specified combinations of RAM boards, EPROM boards, or combination boards. Input/output capacity may be increased by adding I/O expansion boards. Multiple iSBC 569 boards may be included in an

expanded system using one iSBC 569 Intelligent Digital Controller as the system master and additional controllers as intelligent slaves.

# Intelligent Slave Programming

When used as an intelligent slave, the iSBC 569 controller appears as an additional RAM memory module. System bus masters communicate with the iSBC 569 board as if it were just an extension of system memory. To simplify this communication, the user has been given some specific tools:

Flag Interrupt — The Flag Interrupt is generated any time a write command is performed by an off-board CPU to the first location of ISBC 569 RAM. This interrupt provides a means for the master CPU to notify the ISBC 569 controller that it wished to establish a communications sequence. The flag interrupt is cleared when the onboard processor reads the first location of its RAM. In systems with more than one intelligent slave, the flag interrupt provides a unique interrupt to each slave outside the normal MULTIBUS interrupt lines (INTO/-INT7/).

RAM — The on-board 2K byte RAM area that is accessible to both an off-board CPU and the on-board 8085A may be configured for system access on any 2K boundary.

MULTIBUS Interrupts — The third tool to improve system operation as an intelligent slave is access to the MULTIBUS interrupt lines. The iSBC 569 controller can both respond to interrupt signals from an off-board CPU, and generate an interrupt to the off-board CPU via the system bus.

### System Development Capability

Software development for the iSBC 569 Intelligent Digital Controller board is supported by the Intellec® Microcomputer Development System including a resident macroassembler, text editor, system monitor, a linker, object code locator, and Library Manager. In addition, both PL/M and FORTRAN language programs can be compiled to run on the iSBC 569 board. A unique incircuit emulator (ICE-85TM) option provides the capability of developing and debugging software directly on the iSBC 569 board. This greatly simplifies the design, development, and debug of iSBC 569 system software.

# **SPECIFICATIONS**

### 8085A CPU

Word Size — 8, 16 or 24 bits

Cycle Time — 1.30  $\mu$ sec  $\pm$  .1% for fastest executable instruction; i.e., four clock cycles.

Clock Rate — 3.07 MHz ± .1%

### System Access Time

Dual port memory — 725 nsec

### Memory Capacity

On-board ROM/EPROM — 2K, 4K, 8K, or 16K bytes of user installed ROM or EPROM

On-board RAM — 2K bytes of static RAM. Fully

accessible from on-board 8085A. Separately addressable from system bus.

Off-board expansion — up to 64K bytes of EPROM/ROM or RAM capacity.

# I/O Capacity

Parallel-Timers — Three timers, with independent gate input, clock input, and timer output user-accessible. Clock inputs can be strapped to an external source or to an on-board 1.3824 MHz reference. Each timer is connected to a 8259A Programmable Interrupt Controller and may also be optionally connected to UPI processors.

UPI-I/O — Three UPI-41A interfaces, each with two 8-bit I/O ports plus the two UPI Test Inputs. The 8-bit ports are user-configurable (as inputs or outputs) in groups of four.

Serial — 1 TTL compatible serial channel utilizing SID and SOD lines of on-board 8085A CPU

### On-Board Addressing

All communications to the UPI-41A processors, to the programmable reset latch, to the timers, and to the interrupt controller are via read and write commands from the on-board 8085A CPU.

# **Memory Addressing**

**On-board ROM/EPROM** — 0-07FF (using 2758 EPROMs); 0-OFFF (using 2716 EPROMs or 2316 ROMs); 0-1FFF (using 2732 EPROMs); 0-3FFF (using the 2364 ROMs)

**On-board RAM** — 8000-87FF System access — any 2K increment 00000-FF800 (switch selectable); 1K bytes may be disabled from bus access by switch selection.

# I/O Addressing

| Source             | Addresses |

|--------------------|-----------|

| .8253              | 0E0H-0E3H |

| UPI0               | 0E4H-0E5H |

| UPI1               | 0E6H-0E7H |

| UPI2               | 0E8H-0E9H |

| PROGRAMMABLE RESET | 0EAH-0EBH |

| 8259A              | 0ECH-0EDH |

# **Timer Specifications**

Input frequencies - jumper selectable reference

Internal: 1.3824 MHz ± .1% (.723 μsec, nominal) External: User supplied (2 MHz maximum)

Output Frequencies (at 1.3824 MHz)

| Function                        | Min¹      | Max <sup>1</sup> |

|---------------------------------|-----------|------------------|

| Real-time<br>interrupt interval | 1.45 μsec | 47.4 msec        |

| Rate Generator<br>(frequency)   | 21.09 Hz  | 691.2 KHz        |

| 1. Single 16-bit binary count   |           |                  |

### Interfaces

MULTIBUS™ Interface — All signals compatible with iSBC and MULTIBUS architecture

Parallel I/O - All signals TTL compatible

Interrupt Requests - All TTL compatible

Timer - All signals TTL compatible

Serial I/O - All signals TTL compatible

### Connectors

| Interface    | Pins<br>(qty) | Centers<br>(in.) | Mating Connectors            |

|--------------|---------------|------------------|------------------------------|

| Bus          | 86            | 0.156            | Viking 3KH43/9AMK12          |

| Parallel I/O | 50            | 0.1              | 3M 3415-000 or<br>TI H312125 |

### **Physical Characteristics**

Width - 30.48 cm (12.00 inches)

**Depth** — 17.15 cm (6.75 inches) **Thickness** — 1.27 cm (0.50 inch) **Weight** — 3.97 gm (14 ounces)

### **Electrical Characteristics**

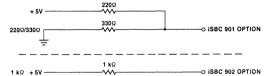

**DC Power Requirements** — +5V @ 2.58A with no optional devices installed. For each 8741A add 135 mA. For each 220/330 resistor network, add 60 mA. Add the following for each EPROM/ROM installed.

| Туре  | +5.0V Current Requirement |        |

|-------|---------------------------|--------|

|       | 1ROM                      | 2ROMS  |

| 2758  | 100 mA                    | 125 mA |

| 2716  | 100 mA                    | 125 mA |

| 2316E | 120 mA                    | 240 mA |

| 2732  | 40 mA                     | 55 mA  |

| 2364  | 40 mA                     | 55 mA  |

### Line Drivers and Terminators

I/O Drivers — The following line drivers are all compatible with the I/O driver sockets on the iSBC 569 Intelligent Digital Controller.

| Driver | Characteristic | Sink Current (mA) |  |

|--------|----------------|-------------------|--|

| 7438   | I,OC           | 48                |  |

| 7437   | i i            | 48                |  |

| 7432   | NI             | 16                |  |

| 7426   | 1,00           | 16                |  |

| 7409   | NI,OC          | 16                |  |

| 7408   | NI             | 16                |  |

| 7403   | I,OC           | 16                |  |

| 7400   | Í.             | 16                |  |

Note | = inverting; NI = non-inverting; OC = open collector.

### I/O Terminators — $220\Omega/330\Omega$ divider or 1 k $\Omega$ pullup

# **Environmental Characteristics**

Operating Temperature — 0°C to 55°C (32°F to 131°F)

Relative Humidity — To 90% without condensation

# **Reference Manuals**

9800845-01 — iSBC 569 Intelligent Digital Controller Board Hardware Reference Manual (NOT SUPPLIED)

9803077 — iSBC 941 Digital Signal Processor User's Guide (NOT SUPPLIED)

Reference manuals are shipped with each product only if designated SUPPLIED (see above). Manuals may be ordered from any Intel sales representative, distributor office or from Intel Literature Department, 3065 Bowers Avenue, Santa Clara, California 95051.

# ORDERING INFORMATION

### **Part Number**

# Description

SBC 569

Intelligent Digital Controller