intel

# iSBC 519 (or pSBC 519\*) PROGRAMMABLE I/O EXPANSION BOARD

- iSBC I/O expansion via direct MULTIBUS Interface

- 72 programmable I/O lines with sockets for interchangeable line drivers and terminators

- Jumper selectable I/O port addresses

- Jumper selectable 0.5, 1.0, 2.0, or 4.0 ms interval timer

- Eight maskable interrupt request lines with priority encoded and programmable interrupt algorithms

The iSBC 519 Programmable I/O Expansion Board is a member of Intel's complete line of iSBC memory and I/O expansion boards. The iSBC 519 interfaces directly to any iSBC single board computer via the system bus to expand input and output port capacity. The iSBC 519 provides 72 programmable I/O lines. The system software is used to configure the I/O lines to meet a wide variety of peripheral requirements. The flexibility of the I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the required sink current, polarity, and drive/termination characteristics for each application. Address selection is accomplished by using wire-wrap jumpers to select one of 16 unique base addresses for the input and output ports. The board operates with a single + 5V power supply.

\*Same product, manufactured by Intel Puerto Rico, Inc.

# FUNCTIONAL DESCRIPTION

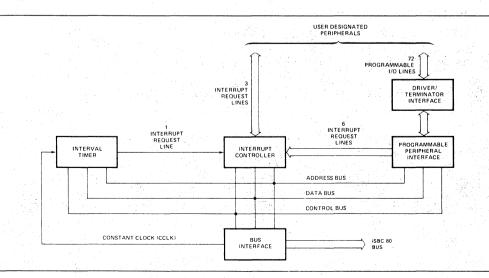

The 72 programmable I/O lines on the iSBC 519 are implemented utilizing three Intel 8255 programmable peripheral interfaces. The system software is used to configure the I/O lines in any combination of unidirectional input/output and bidirectional ports indicated in Table 1. In order to take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. The 72 programmable I/O lines and signal ground lines are brought out to three 50-pin edge connectors that mate with flat, round, or woven cable.

Typical I/O read access time is 350 nanoseconds.

The interval timer provided on the iSBC 519 may be used to generate real time clocking in systems requiring the periodic monitoring of I/O functions. The time interval is derived from the constant clock (BUS CCLK) and the timing interval is jumper selectable. Intervals of 0.5, 1.0, 2.0, and 4.0 milliseconds may be selected when an iSBC single board computer is used to generate the clock. Other timing intervals may be generated if the user provides a separate constant clock reference in the system.

Typical I/O read/write cycle time is 450 nanoseconds.

# **Eight-Level Vectored Interrupt**

An Intel 8259 programmable interrupt controller (PIC) provides vectoring for eight interrupt levels. As shown in Table 2, a selection of three priority processing algorithms is available to the system designer so that the

| Ports |                |                     |                             |                                 |                                             |

|-------|----------------|---------------------|-----------------------------|---------------------------------|---------------------------------------------|

|       |                | Unidire             | ctional                     | Bidirectional                   | Control                                     |

|       | Lines<br>(qty) | Input               | Output                      |                                 |                                             |

|       | (413)          | Unlatched & Strobed | Latched & Latched & Strobed | n fan frank<br>Heferika<br>Lite |                                             |

| 1,4,7 | 8              | X X                 | X X                         | X                               | n an    |

| 2,5,8 | 8              | X X                 | x x                         |                                 | n dae gebeerde geb<br>die de State of State |

| 3,6,9 | 4              | x                   | Х                           |                                 | X <sup>1,2,3</sup>                          |

|       | 4              | X                   | X C C                       |                                 | χ1,2,3                                      |

Table 1. Input/Output Port Modes of Operation

#### Notes

Interval Timer

1. Part of port 3 must be used as a control port when either port 1 or port 2 are used as a latched and strobed input or a latched and strobed output port or port 1 is used as a bidirectional port.

2. Part of port 6 must be used as a control port when either port 4 or port 5 are used as a latched and strobed input or a latched and strobed output port or port 4 is used as a bidirectional port.

3. Part of port 9 must be used as a control port when either port 7 or port 8 are used as a latched and strobed input or a latched and strobed output port or port 7 is used as a bidirectional port.

Figure 1. iSBC 519 Programmable I/O Expansion Board Block Diagram

#### Table 2. Interrupt Priority Options

| Algorithm         | Operation                                                                                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Fully nested      | Interrupt request line priorities<br>fixed at 0 as highest, 7 as<br>lowest.                                                                     |

| Auto-rotating     | Equal priority. Each level, after<br>receiving service, becomes the<br>lowest priority level until next<br>interrupt occurs.                    |

| Specific priority | System software assigns<br>lowest priority level. Priority of<br>all other levels are based in se-<br>quence numerically on this<br>assignment. |

manner in which requests are serviced may be configured to match system requirements. Priority assignments may be reconfigured dynamically via software at any time during system operation. The PIC accepts interrupt requests from the programmable parallel I/O interfaces, the interval timer, or direct from peripheral equipment. The PIC then determines which of the

## SPECIFICATIONS

#### Addressing

| • | Port    | 1  | 2  |    | 8255<br>No. 1<br>Control | 4  | 5  | 6  | 8255<br>No. 2<br>Control | 7  | 8  | 9  | 8255<br>No. 3<br>Control |

|---|---------|----|----|----|--------------------------|----|----|----|--------------------------|----|----|----|--------------------------|

|   | Address | X0 | X1 | X2 | X3                       | X4 | X5 | X6 | X7                       | X8 | X9 | XA | ХВ                       |

#### Interrupts

Register Addresses (hex notation, I/O address space)

- XD Interrupt request register

- XC In-service register

- XD Mask register

- XC Command register

- XD Block address register

- XC Status (polling register)

#### Note

Several registers have the same physical address; sequence of access and one data bit of control word determines which register will respond.

Ten interrupt request lines may originate from the programmable peripheral interface (6 lines), or user specified devices via the I/O edge connector (3 lines), or interval timer (1 line).

## Interval Timer

**Output Register** — Timer interrupt register output is cleared by an output instruction to I/O address XE or XF1.

Timing Intervals — 500, 1,000, 2,000, and 4,000 ms  $\pm$  1%; jumper selectable<sup>2</sup>.

#### Notes

1. X is any hex digit assigned by jumper selection.

2. Assumes constant clock (CCLK) frequency of 9.216 MHz ± 1%.

incoming requests is of the highest priority, determines whether this request is of higher priority than the level currently being serviced, and if appropriate, issues an interrupt to the system master. Any combination of interrupt levels may be masked through storage, via software, of a single byte to the interrupt mask register of the PIC.

Interrupt Request Generation — Interrupt requests may originate from 10 sources. Six jumper selectable interrupt requests can be automatically generated by the programmable peripheral interfaces when a byte of information is ready to be transferred to the system master (i.e., input buffer is full) or a character has been transmitted (i.e., output data buffer is empty). Three interrupt request lines may be interfaced to the PIC directly from user designated peripheral devices via the I/O edge connectors. One interrupt request may be generated by the interval timer.

Bus Line Drivers — The PIC interrupt request output line may be jumper selected to drive any of the nine interrupt lines on the MULTIBUS. Any of the on-board request lines may also drive any interface interrupt line directly via jumpers and buffers on the board.

## Interfaces

Bus — All signals TTL compatible Parallel I/O — All signals TTL compatible Interrupt Requests — All TTL compatible

## Connectors

| Interface              | Pins<br>(qty) | Centers<br>(in.) | Mating Connectors              |

|------------------------|---------------|------------------|--------------------------------|

| Bus                    | 86            | 0.156            | Viking 3KH43/9AMK12            |

| Parallel I/O           | 50            | 0.1              | 3M 3415-000 or<br>TI H312125   |

| Serial I/O             | 26            | 0.1              | 3M 3462-000 or<br>TI H312113   |

| Auxiliary <sup>1</sup> | 60            | 0.1              | AMP PE5-14559 or<br>TI H311130 |

Note

1. Connector heights and wirewrap pin lengths are not guaranteed to conform to Intel OEM or System packaging.

#### Line Drivers and Terminators

**I/O Drivers** — The following line drivers and terminators are compatible with all the I/O driver sockets on the iSBC 519:

| Driver | Characteristic | Sink Current (mA) |

|--------|----------------|-------------------|

| 7438   | 1,00           | 48                |

| 7437   | I I            | 48                |

| 7432   | NI             | 16                |

| 7426   | I,OC           | 16                |

| 7409   | NI,OC          | 16                |

| 7408   | NI             | 16                |

| 7403   | 1,00           | 16                |

| 7400   | l l            | 16                |

Note

I = inverting; NI = non-inverting; OC = open-collector.

#### I/O Terminators — 220Ω/330Ω divider or 1 kΩ pullup

|              | <b>220</b> Ω          | <ul> <li>State</li> </ul> |

|--------------|-----------------------|---------------------------|

| + 5V         | 2000                  | And a failer of the       |

| 220Ω/330Ω    | <b>330</b> Ω          | O ISBC 901 OPTION         |

| wai <u>P</u> | an fuera al el remaio | and a state of            |

|              | 1 kΩ                  |                           |

| 1 kΩ + 5V    |                       | o iSBC 902 OPTION         |

Ports 1, 4, and 7 may use any of the drivers or terminators shown above for unidirectional (input or output) port configurations. Either terminator and the following bidirectional drivers and terminators may be used for ports 1, 4, and 7 when these ports are used as bidirectional ports.

#### **Bidirectional Drivers**

| ſ | Driver     | Characteristic | Sink Current (mA) |

|---|------------|----------------|-------------------|

| Γ | Intel 8216 | NI, TS         | 25 ,              |

|   | Intel 8226 | I, TS          | 50                |

#### Note

I = inverting; NI = non-inverting; TS = three-state.

**Terminators** (for ports 1, 4, and 7 when used as bidirectional ports)

| Supplier | Product Series |

|----------|----------------|

| CTS      | 760-           |

| Dale     | LDP14k-02      |

| Beckman  | 899-1          |

#### **Bus Drivers**

| Function | Characteristic | Sink Current (mA) |

|----------|----------------|-------------------|

| Data     | Tri-state      | 50                |

| Commands | Tri-state      | 25                |

# **ORDERING INFORMATION**

Part Number SBC 519

# Description

the sector of the constraints and the

Programmable I/O Expansion Board

#### Physical Characteristics

Width — 12.00 in. (30.48 cm) Height — 6.75 in. (17.15 cm) Depth — 0.50 in. (1.27 cm) Weight — 14 oz (397.3 gm)

## Electrical Characteristics Average DC Current

| Voltage                | Without Termination <sup>1</sup> | With Termination <sup>2</sup> |

|------------------------|----------------------------------|-------------------------------|

| $V_{CC} = +5V \pm 5\%$ | I <sub>CC</sub> = 1.5A max       | 3.5A max                      |

Note

1. Does not include power required for optional I/O drivers and I/O terminators.

2. With 18  $220 \ensuremath{\Omega}/330 \ensuremath{\Omega}$  Input terminators installed, all terminator inputs low.

# **Environmental Characteristics**

Operating Temperature - 0°C to + 55°C

#### **Reference Manual**

grand the Ch

9800385B — iSBC 519 hardware Reference Manual (NOT SUPPLIED)

Manuals may be ordered from any Intel sales representative, distributor office or from Intel Literature Department, 3065 Bowers Avenue, Santa Clara, California 95051.