# iSBX<sup>™</sup> 350 PARALLEL MULTIMODULE<sup>™</sup> BOARD HARDWARE REFERENCE MANUAL

# iSBX 350<sup>™</sup> PARALLEL MULTIMODULE<sup>™</sup> BOARD HARDWARE REFERENCE MANUAL

Manual Order Number: 9803191-02

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may be used only to identify Intel products:

| BXP    | Intel           | Megachassis |

|--------|-----------------|-------------|

| CREDIT | Intelevision    | Micromap    |

| i      | Intellec        | Multibus    |

| iCE    | iRMX            | MULTIMODULE |

| iCS    | iSBC            | PROMPT      |

| im     | iSBX            | Promware    |

| Insite | Library Manager | RMX/80      |

| Intel  | MCS             | UPI         |

|        |                 | μScope      |

and the combination of ICE, iCS, iRMX, iSBC, iSBX, or MCS and a numerical suffix.

This manual provides general information, installation, programming information, principles of operation, and service information for the Intel iSBX 350 Parallel Multimodule Board. Additional information is available in the following documents:

- Intel MCS-85 User's Manual, Order No. 9800366

- Intel Peripheral Design Handbook, Order No. 9800676

- Intel 8080/8085 Assembly Language Programming Manual, Order No. 9800301

- Intel 8255A Programmable Peripheral Interface, Application Note AP-15

- Intel MULTIBUS Interfacing, Application Note AP-28

- Intel MULTIBUS Specification, Order No. 9800683

#### CHAPTER 1 GENERAL INFORMATION

| GENERAL INFORMATION  | PA | GE  |

|----------------------|----|-----|

| Introduction         |    | 1-1 |

| Description          |    | 1-1 |

| Equipment Supplied   |    | 1-1 |

| Compatible Equipment |    | 1-2 |

| Specifications       |    | 1-2 |

### CHAPTER 2 PREPARATION FOR USE

| Introduction                     | 2-1 |

|----------------------------------|-----|

| Unpacking and Inspection         | 2-1 |

| Installation Considerations      | 2-1 |

| Power Requirement                | 2-1 |

| Cooling Requirement              | 2-1 |

| Mounting Requirement             | 2-1 |

| Dimensions                       | 2-1 |

| DC Interface Characteristics     | 2-3 |

| Connector Configuration          | 2-3 |

| Jumper Configuration             | 2-4 |

| Line Drivers and I/O Terminators | 2-8 |

| Installation Procedure           | 2-8 |

|                                  |     |

### **CHAPTER 3**

| PROGRAMMING INFORMATION | PA(       | GΕ  |

|-------------------------|-----------|-----|

| Introduction            |           | 3-1 |

| PPI Programming         |           | 3-1 |

| Addressing              |           | 3-1 |

| Control Word Format     | • • • • • | 3-1 |

| Initialization          |           | 3-2 |

| Operation               |           | 3-2 |

| Read Operation          |           | 3-2 |

| Write Operation         |           | 3-2 |

|                         |           |     |

### **CHAPTER 4**

PRINCIPLES OF OPERATION

| Introduction                    | 4-1 |

|---------------------------------|-----|

| iSBX <sup>™</sup> Bus Interface | 4-1 |

| Port Interface                  | 4-2 |

### CHAPTER 5 SERVICE INFORMATION

| Introduction                  | 5 - 1 |

|-------------------------------|-------|

| Replaceable Parts             | 5-1   |

| Service Diagrams              | 5-1   |

| Service and Repair Assistance | 5-1   |

# TABLES

| Table | Title                          | Page | Table | Title                                   | Page |

|-------|--------------------------------|------|-------|-----------------------------------------|------|

| 1-1.  | Specifications                 | 1-2  | 3-1.  | Port Addressses                         | 3-1  |

| 2-1.  | DC Characteristics             | 2-3  | 3-2.  | Typical PPI Initialization Subroutine . | 3-2  |

| 2-2.  | Connector P1 Pin Assignments   | 2-3  | 3-3.  | Typical PPI Port READ Subroutine        | 3-2  |

| 2-3.  | Connector J1 Pin Assignments   | 2-4  | 3-4.  | Typical PPI Port WRITE Subroutine       | 3-2  |

| 2-4.  | Compatible Connector Details   | 2-5  | 4-1.  | PPI Operations                          | 4-1  |

| 2-5.  | Port Configuration Jumpers for |      | 4-2.  | Mode Definition Summary Table           | 4-2  |

|       | Multimodule™ Board             | 2-5  | 5-1.  | Replaceable Parts                       | 5-1  |

| 2-6.  | Compatible Line Drivers        | 2-8  | 5-2.  | Manufacturer Codes                      | 5-1  |

# ILLUSTRATIONS

| Figure               | Title                                                                       | Page | Figure | Title                                                                             | Page |

|----------------------|-----------------------------------------------------------------------------|------|--------|-----------------------------------------------------------------------------------|------|

| 1-1.                 | iSBX 350™ Parallel Multimodule™<br>Board                                    | 1-1  | 3-2.   | PPI Port C Bit Set/Reset<br>Control Word Format                                   | 3-2  |

| 2-1.<br>2-2.         | Board Dimensions (Inches)<br>Mounting Clearances (Inches)                   |      | 5-1.   | iSBX 350 <sup>™</sup> Parallel Multimodule <sup>™</sup><br>Parts Location Diagram | 5-3  |

| 2-3.<br>2-4.<br>3-1. | Compatible I/O Terminators<br>Mounting Technique<br>PPI Control Word Format | 2-9  | 5-2.   | iSBX 350 <sup>™</sup> Parallel Multimodule <sup>™</sup><br>Schematic Diagram      | 5-5  |

### CHAPTER 1 GENERAL INFORMATION

### **1-1. INTRODUCTION**

**1-2. DESCRIPTION**

The iSBX 350 Parallel Multimodule Board (hereafter referred to as the Multimodule board) is a member of Intel's growing line of expansion Multimodule boards designed to increase the capabilities of any iSBC microcomputer that contains a Multimodule connector. This manual describes the general information, preparation for use, programming, principles of operation, and service information for the Multimodule board.

Figure 1-1 shows the iSBX 350 Parallel Multimodule

Board. The Multimodule board provides expansion capability of 24 programmable parallel I/O lines for

a host iSBC microcomputer. The additional I/O

lines are configurable via the system software and the line driver/receiver devices on the Multimodule board. The Multimodule board contains an 8255A-5 Programmable Peripheral Interface (PPI) device that may be initialized in one of 3 modes; MODE ZERO - the basic input/output mode, MODE ONE the strobed input/output mode, and MODE TWO the bidirectional bus interface mode. The board also includes two socketed 8226 Bidirectional Bus Driver devices for interfacing to external devices.

### **1-3. EQUIPMENT SUPPLIED**

The following are supplied with each iSBX 350 Parallel Multimodule Board:

- a. Schematic Diagram, dwg. no. 2003069

- b. Assembly Diagram, dwg. no. 1003067

- c. 1 spacer, plastic,  $\frac{1}{2} \times \frac{6}{32}$

- d. 2 screws, plastic, 1/4 x 6/32.

Figure 1-1. iSBX 350<sup>™</sup> Parallel Multimodule<sup>™</sup> Board

In addition, the user must supply a host iSBC microcomputer; line driver/terminator devices for Multimodule sockets XU3, XU4, XU5, and XU6, if required by the application; and an interconnecting cable and connector.

### **1-4. COMPATIBLE EQUIPMENT**

The Multimodule board must be used with a host

Intel iSBC microcomputer that includes a compatible mating connector.

### **1-5. SPECIFICATIONS**

The specifications for the iSBX 350 Parallel Multimodule Board are listed in table 1-1.

| I/O ADDRESSING                                       | All addressing for the used on the host iSE |                                                         |           |               | t on the Multimodule connector    |  |

|------------------------------------------------------|---------------------------------------------|---------------------------------------------------------|-----------|---------------|-----------------------------------|--|

| INTERFACE COMPATIBILITY                              |                                             |                                                         | mputer    | Thereforeneou |                                   |  |

| Parallel Interface                                   | 24 programmable line                        | s (8 lines p                                            | er port); | one port in   | cludes bidirectional bus drivers  |  |

|                                                      |                                             |                                                         | stallatio | n of line dr  | rivers and/or I/O terminators, as |  |

| Overheime Dive                                       | required by the applic                      |                                                         |           |               |                                   |  |

| System Bus                                           | Compatible with the                         | ISBX DUS                                                | specifica | ations.       |                                   |  |

| PARALLEL INTERFACE CONNECTOR                         | RS                                          |                                                         |           |               | ,                                 |  |

|                                                      |                                             | No. of                                                  |           | Centers       |                                   |  |

|                                                      | Interface                                   | Pins                                                    | in.       | mm            | Mating Connectors                 |  |

|                                                      |                                             |                                                         |           |               | AMP-88083-1                       |  |

|                                                      | J1 Channel                                  | 25/50                                                   | 0.1       | 2.54          | 3M-3415-0000                      |  |

| POWER REQUIREMENTS                                   |                                             |                                                         | L         |               |                                   |  |

| FOWER REQUIREMENTS                                   | Power Requiremen                            | t                                                       |           | Conf          | iguration                         |  |

|                                                      | · · · · · · · · · · · · · · · · · · ·       |                                                         |           |               |                                   |  |

|                                                      | +5V @ 320 mA                                | Sockets XU3, XU4, XU5, and XU6 empty (As-shipped).      |           |               |                                   |  |

|                                                      | +5V @ 500 mA                                | mA Sockets XU3, XU4, XU5, and XU6 contain 7438 buffers. |           |               |                                   |  |

|                                                      | +5V @ 620 mA                                |                                                         |           |               | and XU6 contain iSBC 901          |  |

|                                                      |                                             | Termin                                                  | ation de  | evices.       |                                   |  |

| ENVIRONMENTAL REQUIREMENTS<br>Operating Temperature: | 0° to 55°C (32° to 13                       | 1°F).                                                   |           |               |                                   |  |

| Relative Humidity:                                   | To 90% without cond                         | ensation.                                               |           |               |                                   |  |

| PHYSICAL CHARACTERISTICS                             |                                             |                                                         |           |               |                                   |  |

| Width:                                               | 7.24 cm (2.85 inches                        | ).                                                      |           |               |                                   |  |

| Length:                                              | 9.40 cm (3.70 inches                        |                                                         |           |               |                                   |  |

| Thickness:                                           | 2.03 cm (0.80 inch)                         |                                                         |           | •             |                                   |  |

| · · · · · · · · · · · · · · · · · · ·                | 2.82 cm (1.13 inches                        |                                                         | lule and  | iSBC boa      | rd.                               |  |

| Weight:                                              | 51 gm (1.79 ounces).                        |                                                         |           |               |                                   |  |

### **Table 1-1. Specifications**

# CHAPTER 2 PREPARATION FOR USE

### 2-1. INTRODUCTION

This chapter provides information on preparing and installing the iSBX 350 Parallel Multimodule Board. Included are instructions on unpacking and inspection; installation considerations, such as physical, power, cooling, and mounting requirements; jumper configurations; ac and dc characteristics; connector assignments; and installation procedures.

### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, contact the Intel Technical Support Center to obtain a Return Authorization Number and further instructions. A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be shipped.

### 2-3. INSTALLATION CONSIDERATIONS

The iSBX 350 Parallel Multimodule Board is designed to interface with all Intel iSBC Single Board Computers that contain the I/O interface connector required to support Multimodule boards. Other installation considerations such as power, cooling, mounting, and physical size requirements, are outlined in the following paragraphs.

### 2-4. POWER REQUIREMENT

The power requirements for the Multimodule board vary depending on the configuration of the board. The Multimodule board with no user-installed buffers (sockets XU3 through XU6) requires +5V ( $\pm 0.25V$ ) at 320 mA (maximum).

With four 7438 buffers installed in sockets XU3 through XU6, the board requires +5V ( $\pm 0.25V$ ) at 500 mA (maximum).

If iSBC 901 termination packages are used, the board requires  $+5V (\pm 0.25V)$  at 620 mA (maximum).

All power for the Multimodule board is derived from the host iSBC microcomputer and drawn through the iSBX bus (P1) on the Multimodule board. Table 1-1 contains these power requirements in tabular form.

### NOTE

If modification of a Multimodule board is required, ensure that none of the Multimodule specifications and standards are violated in doing so.

### 2-5. COOLING REQUIREMENT

The iSBX 350 Parallel Multimodule Board dissipates 44.1 gram-calories/minute (0.18 BTU/minute) and adequate circulation of air must be provided to prevent a temperature rise above  $55^{\circ}$ C (131°F).

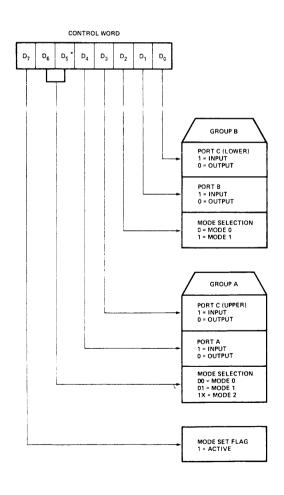

### 2-6. MOUNTING REQUIREMENT

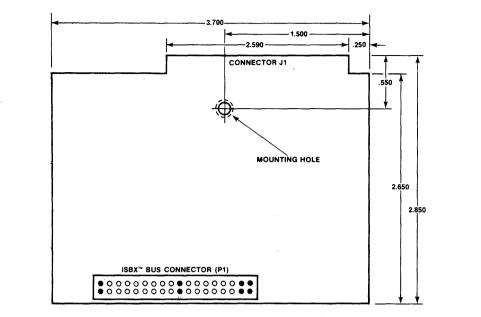

The Multimodule boards will mount onto any iSBC microcomputer containing an iSBX bus connector. Figure 2-1 shows the P1 connector and mounting hole location on the Multimodule board. The mounting hardware supplied as part of the Multimodule board includes:

- a. 1 plastic spacer,  $\frac{1}{2}$  inch x 6/32, separate from the board.

- b. 36-pin connector P1, factory-installed onto the board.

- c. 2 plastic screws,  $\frac{1}{4}$  inch x 6/32, separate from board.

### NOTE

Plan your cardcage space allocation. The Multimodule board, when installed onto a host microcomputer, occupies an additional card slot adjacent to the component side of the host microcomputer in an iSBC 604/614 Cardcage.

### **2-7. DIMENSIONS**

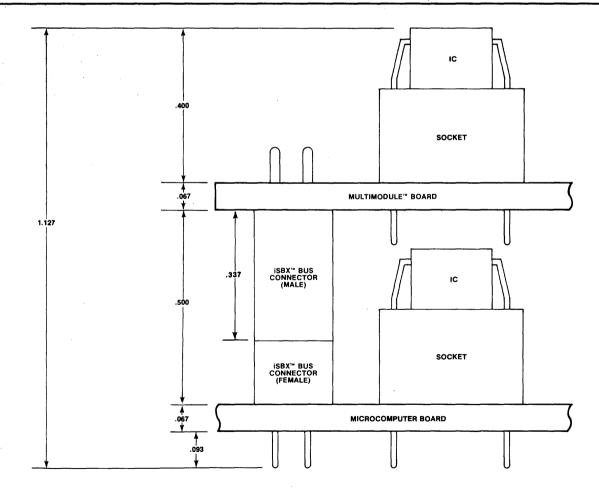

Figure 2-1 shows the dimensions for the Multimodule board, and figure 2-2 shows the clearances for a Multimodule board mounted onto a host iSBC microcomputer. The physical dimensions of the Multimodule board are as follows:

- a. Width: 7.27 cm (2.85 inches).

- b. Length: 9.40 cm (3.70 inches).

- c. Thickness: 2.05 cm (0.80 inch) Multimodule board only; 2.82 cm (1.13 inches) Multimodule and iSBC board.

Figure 2-1. Board Dimensions (Inches)

Figure 2-2. Mounting Clearances (Inches)

### 2-8. DC INTERFACE CHARACTERISTICS

The dc characteristics of the Multimodule board at the J1 connector are listed in table 2-1.

### 2-9. CONNECTOR CONFIGURATION

The Multimodule board is designed to mount onto a Multimodule connector on a host iSBC microcomputer. Connector P1 interfaces all data and control signals between the host iSBC microcomputer and the Multimodule board. The signals found on each pin of the P1 connector are listed in table 2-2. Reference chapter 4 for signal descriptions.

Connector J1 on the Multimodule board handles parallel I/O communication between the Multimodule board and an external device. The signals found on each pin of the J1 connector are listed in table 2-3.

| Output<br>Signal                         | Type<br>Drive    | lo∟ MAX<br>(mA)                         | V <sub>oL</sub> MAX<br>(I <sub>oL</sub> =MAX) | І <sub>ОН</sub> МАХ<br>(μА)                           | V <sub>OH</sub> MIN<br>(I <sub>OH</sub> ≕MAX) | C <sub>o</sub> MIN<br>(pf) |

|------------------------------------------|------------------|-----------------------------------------|-----------------------------------------------|-------------------------------------------------------|-----------------------------------------------|----------------------------|

| Port A                                   | TTL              | 20                                      | 0.45                                          | -10mA                                                 | 2.4                                           | 18                         |

| Input<br>Signal                          | Type<br>Receiver | l <sub>ı∟</sub> MAX<br>(mA)<br>(Vı∟=.45 | VIL MAX                                       | I <sub>IH</sub> MAX<br>(mA)<br>(V <sub>IH</sub> =2.4) | V⊮ MIN                                        | C <sub>1</sub> MAX<br>(pf) |

| Port A                                   | TTL              | -5.2                                    | 0.80                                          | -2.2                                                  | 2.0                                           | 18                         |

| Port B & C:<br>1K Pull-Up<br>Port B & C: | TTL              | -5.0                                    | 0.80                                          | -2.2                                                  | 2.0                                           | 20                         |

| 220/330 Terminator                       | TTL              | -21.00                                  | 0.80                                          | -3.0                                                  | 2.0                                           | 20                         |

| EXT INTR (J1 Pin 50)                     | TTL              | -6.5                                    | 0.50                                          | -2.2                                                  | 2.4                                           | 40                         |

Table 2-1. DC Characteristics

Capacity values are approximations.

| Table 2-2 | . Connector | Pl Pin | Assignments |  |

|-----------|-------------|--------|-------------|--|

|           |             |        |             |  |

\_\_\_\_

.

.. . . . .

| Pin | Mnemonic | Description      | Pin | Mnemonic | Description     |

|-----|----------|------------------|-----|----------|-----------------|

| 35  | GND      | SIGNAL GROUND    | 36  | +5V      | +5 Volts        |

| 33  | MD0      | MDATA BIT 0      | 34  | _        | RESERVED        |

| 31  | MD1      | MDATA BIT 1      | 32  | _        | RESERVED        |

| 29  | MD2      | MDATA BIT 2      | 30  | OPT0     | OPTION 0        |

| 27  | MD3      | MDATA BIT 3      | 28  | OPT1     | OPTION 1        |

| 25  | MD4      | MDATA BIT 4      | 26  | -        | RESERVED        |

| 23  | MD5      | MDATA BIT 5      | 24  | _        | RESERVED        |

| 21  | MD6      | MDATA BIT 6      | 22  | MCS0/    | M CHIP SELECT 0 |

| 19  | MD7      | MDATA BIT 7      | 20  | _        | RESERVED        |

| 17  | GND      | SIGNAL GROUND    | 18  | +5V      | +5 Volts        |

| 15  | IORD/    | IO READ COMMAND  | 16  | -        | RESERVED        |

| 13  | IOWRT/   | IO WRITE COMMAND | 14  | MINTRO   | M INTERRUPT 0   |

| 11  | MAO      | M ADDRESS 0      | 12  | MINTR1   | M INTERRUPT 1   |

| 9   | MA1      | M ADDRESS 1      | 10  | _        | RESERVED        |

| 7   | _        | RESERVED         | 8   | MPST/    | M PRESENT       |

| 5   | RESET    | RESET            | 6   | -        | RESERVED        |

| 3   | GND      | SIGNAL GROUND    | 4   | +5V      | +5 Volts        |

| 1   |          | RESERVED         | 2   |          | RESERVED        |

| Pin | Signal | Pin | Signal         |  |

|-----|--------|-----|----------------|--|

| .1  | Ground | 2   | PORT B - BIT 7 |  |

| 3   | Ground | 4   | PORT B - BIT 6 |  |

| 5   | Ground | 6   | PORT B - BIT 5 |  |

| 7   | Ground | 8   | PORT B - BIT 4 |  |

| 9   | Ground | 10  | PORT B - BIT 3 |  |

| 11  | Ground | 12  | PORT B - BIT 2 |  |

| 13  | Ground | 14  | PORT B - BIT 1 |  |

| 15  | Ground | 16  | PORT B - BIT 0 |  |

| 17  | Ground | 18  | PORT C - BIT 3 |  |

| 19  | Ground | 20  | PORT C - BIT 2 |  |

| 21  | Ground | 22  | PORT C - BIT 1 |  |

| 23  | Ground | 24  | PORT C - BIT 0 |  |

| 25  | Ground | 26  | PORT C - BIT 4 |  |

| 27  | Ground | 28  | PORT C - BIT 5 |  |

| 29  | Ground | 30  | PORT C - BIT 6 |  |

| 31  | Ground | 32  | PORT C - BIT 7 |  |

| 33  | Ground | 34  | PORT A - BIT 7 |  |

| 35  | Ground | 36  | PORT A - BIT 6 |  |

| 37  | Ground | 38  | PORT A - BIT 5 |  |

| 39  | Ground | 40  | PORT A - BIT 4 |  |

| 41  | Ground | 42  | PORT A - BIT 3 |  |

| 43  | Ground | 44  | PORT A - BIT 2 |  |

| 45  | Ground | 46  | PORT A - BIT 1 |  |

| 47  | Ground | 48  | PORT A - BIT 0 |  |

| 49  | Ground | 50  | Optional *     |  |

Table 2-3. Connector J1 Pin Assignments

Table 2-4 contains a listing of some of the details for compatible connectors that may be user-supplied to interface to the J1 connector on the Multimodule board.

### 2-10. JUMPER CONFIGURATION

The Multimodule board contains 26 wirewrap posts (E1 through E26). These may be user-configured to provide the flexibility needed to support all three modes of operation of the PPI. Table 2-5 lists the functions of each jumper.

**Port Enables.** Each of the Port C I/O lines contains enable/disable jumper options (E7-E14 and E19-E26). Additional jumpers (E15-E18) provide ability to input or output four other signals (MINTR0, MINTR1, OPT0, OPT1) via Port C; thus the user can buffer these signals to the interface.

Interrupt/Options. E6 provides a convenient method to send the MINTR0, MINTR1, OPT0, or

OPT1 signal to pin 50 of the J1 connector. E6 may also be jumpered to +5 volts when the application dictates. Reference to table 2-5.

If E6 is wired to +5V, ensure that the connector is installed properly onto J1; the +5V signal must always interface to pin 50 of J1. Failure to do so could result in damage to the terminator/driver devices in XU1 through XU6.

**Driver Control.** E2 provides direction control for the bidirectional bus drivers, and may be jumpered to E1 or any of the Port C control lines.

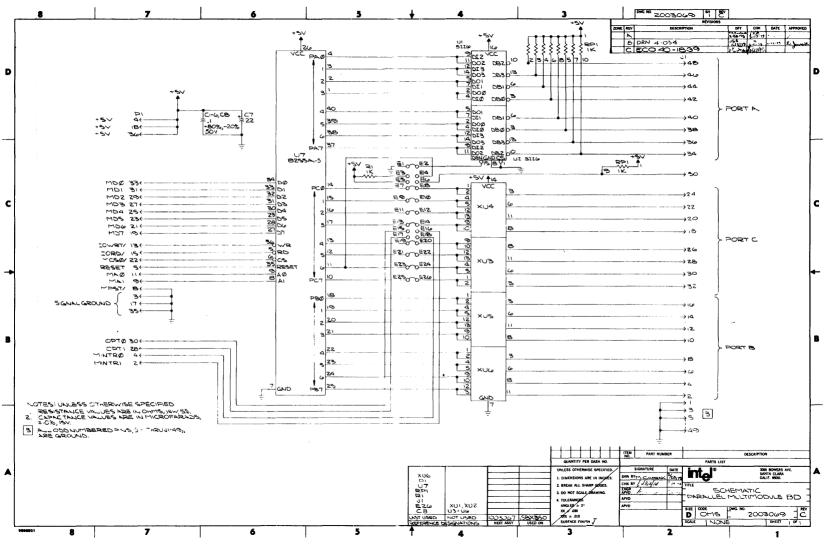

The schematic drawing of the Multimodule board (reference figure 5-2) shows the "as shipped" configuration of the jumpers, including connections from E1 to E2, E7 to E8, E9 to E10, E11 to E12, E13 to E14, E19 to E20, E21 to E22, E23 to E24, and E25 to E26.

| Function                     | No. Of<br>Pairs/<br>Pins | Centers<br>(inches) | Connector<br>Type     | Vendor                           | Vendor Part No.                                                                   |

|------------------------------|--------------------------|---------------------|-----------------------|----------------------------------|-----------------------------------------------------------------------------------|

| Parallel<br>I/O<br>Connector | 25/50                    | 0.1                 | Female,<br>Flat Crimp | 3M<br>3M<br>AMP<br>ANSLEY<br>SAE | 3415-0000 WITH EARS<br>3415-0000 W/O EARS<br>88083-1<br>609-5015<br>SD6750 SERIES |

| Paraliei<br>I/O<br>Connector | 25/50                    | 0.1                 | Female,<br>Soldered   | AMP<br>VIKING<br>TI              | 2-583485-6<br>3VH25/1JV5<br>H312125                                               |

| Parallel<br>I/O<br>Connector | 25/50                    | 0.1                 | Female,<br>Wirewrap   | TI<br>VIKING<br>ITT CANNON       | H311125<br>3VH25/1JND5<br>EC4A050A1A                                              |

Table 2-4. Compatible J1 Connector Details

| Table 2-5  | Dort | Configuration | Jumpore | for | MultimoduloIM | Roard |

|------------|------|---------------|---------|-----|---------------|-------|

| Table 2-5. | FOR  | Configuration | Jumpers | IOL | multimodule   | Doaru |

| Dout I Mada I | Driver (D)/                                        | Jumper Configuration  |               |                                             |                                             | Restrictions                              |                                                                                                   |                                                                                         |

|---------------|----------------------------------------------------|-----------------------|---------------|---------------------------------------------|---------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|               | Terminator (T)                                     | Delete                | Add           | Effect                                      | Port                                        | neatrictiona                              |                                                                                                   |                                                                                         |

| X0            | 0 Input                                            | 8226: U1, U2          | *E1-E2        | E3-E2                                       | 8226 = input enabled.                       | X1                                        | None; can be in Mode 0 or 1, input or output.                                                     |                                                                                         |

|               |                                                    |                       |               |                                             |                                             | X2                                        | None; can be in Mode 0,<br>input or output, unless<br>Port X1 is in Mode 1.                       |                                                                                         |

| X0            | 0 Output<br>(latched)                              | 8226: U1, U2          |               | *E1-E2                                      | 8226 = output enabled.                      | X1                                        | None; can be in Mode 0 or<br>1, input or output.                                                  |                                                                                         |

|               |                                                    |                       |               |                                             |                                             | X2                                        | None; can be in Mode 0,<br>input or output, unless<br>Port X1 is in Mode 1.                       |                                                                                         |

| X0            | 1 Input 8226: U1, U2<br>(strobed) T: XU3<br>D: XU4 | (strobed) T: XL       | T: XU3        | *E1-E2                                      | E3-E2                                       | 8226 = input enabled.                     | X1                                                                                                | None; can be in Mode 0 or<br>1, input or output.                                        |

|               |                                                    |                       | *E19-E20      | Connects J1-26 to STB <sub>A</sub> / input. | X2                                          | Port X2 bits perform the following:       |                                                                                                   |                                                                                         |

|               |                                                    |                       |               | *E21-E22<br>and                             | E21-E14                                     | Connects IBF <sub>A</sub> output to J1-18 |                                                                                                   | <ul> <li>Bits 0, 1, 2 — Control<br/>for Port X1 if Port X1 is<br/>in Mode 1.</li> </ul> |

|               |                                                    |                       | *E13-E14      | E13-E16                                     | Connects INT <sub>A</sub> output to MINTR1. |                                           | <ul> <li>Bit 3 — Port X0 Inter-<br/>rupt (PA INTR) to inter-<br/>rupt jumper matrix.</li> </ul>   |                                                                                         |

|               |                                                    |                       | or<br>E13-E18 | or<br>E13-E18                               | Connects INT <sub>A</sub> output to         |                                           | <ul> <li>Bit 4 — Port X0 Strobe<br/>(STB/) input.</li> </ul>                                      |                                                                                         |

|               |                                                    |                       |               |                                             | MINTRO.                                     |                                           | <ul> <li>Bit 5 — Port X0 input<br/>Buffer Full (IBF) output.</li> </ul>                           |                                                                                         |

|               |                                                    |                       |               |                                             |                                             |                                           | <ul> <li>Bits 6, 7 — Port X2 input<br/>or output (both must be<br/>in same direction).</li> </ul> |                                                                                         |

| *Defau        |                                                    | nected at the factory |               |                                             |                                             |                                           |                                                                                                   |                                                                                         |

| D                   |                                                         | Driver (D)/            |                                      | Jumper (                                                          | Restrictions                                   |                                                  |                                                                                                     |

|---------------------|---------------------------------------------------------|------------------------|--------------------------------------|-------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Port Mode Terminato | Terminator (T)                                          | Delete                 | Add                                  | Effect                                                            | Port                                           | nestrictions                                     |                                                                                                     |

| X0                  | 1 Output<br>(latched)                                   | 8226: U1, U2<br>T: XU3 |                                      | *E1-E2                                                            | 8226 = output enabled.                         | X1                                               | None; can be in Mode 0 or<br>1, input or output.                                                    |

|                     |                                                         | D: XU4                 |                                      | *E23-E24                                                          | Connects J1-30 to ACK <sub>A</sub> / input.    | X2                                               | Port X1 bits perform the following:                                                                 |

|                     |                                                         |                        | *E13-E14<br>and<br>*E25-E26          |                                                                   | Connects OBF₄ output<br>to J1-18.              |                                                  | <ul> <li>Bits 0, 1, 2 — Control<br/>for Port X1 if Port X1 is<br/>in Mode 1.</li> </ul>             |

|                     |                                                         |                        |                                      | E13-E16<br>or                                                     | Connects INT <sub>A</sub> output to MINTR1.    | -                                                | <ul> <li>Bit 3 — Port X0 inter-<br/>rupt (PA INTR) to inter-<br/>rupt jumper matrix.</li> </ul>     |

|                     |                                                         |                        |                                      | E13-E18                                                           | Connects INT <sub>A</sub> output to<br>MINTR0. |                                                  | <ul> <li>Bits 4, 5 — Port X2 input<br/>or output (both must be<br/>in same direction).</li> </ul>   |

|                     |                                                         |                        |                                      |                                                                   |                                                |                                                  | <ul> <li>Bit 6 — Port X0 Ac-<br/>knowledge (ACK/) in-<br/>put.</li> </ul>                           |

|                     |                                                         |                        |                                      |                                                                   |                                                |                                                  | <ul> <li>Bit 7 — Port X0 Output<br/>Buffer Full (OBF/) out-<br/>put.</li> </ul>                     |

| X0                  | X0 2 8226: U1, U2<br>(bi- T: XU3<br>directional) D: XU4 | *E1-E2                 | E4-E2                                | Allows ACK <sub>4</sub> / input to control 8226 in/out direction. | X1                                             | None; can be in Mode 0 or<br>1, input or output. |                                                                                                     |

|                     | ,                                                       | *E19-E20 Con           | Connects J1-26 to STB <sub>4</sub> / | X2 Port X2 bits<br>following:                                     | Port X2 bits perform the following:            |                                                  |                                                                                                     |

|                     |                                                         |                        | *E7-E8                               | E21-E8                                                            | input.<br>Connects IBF₄ output<br>to J1-24.    |                                                  | <ul> <li>Bits 0, 1, 2 — Can be<br/>used for input or output<br/>if Port X2 is in Mode 0.</li> </ul> |

|                     |                                                         |                        | and<br>*E21-E22                      | *E23-E24                                                          | Connects J1-30 to<br>ACK₄/ input.              |                                                  | <ul> <li>Bit 3 — Port X0 inter-<br/>rupt (PA INTR) to inter-<br/>rupt jumper matrix.</li> </ul>     |

|                     |                                                         |                        | *E13-E14<br>and                      | E25-E14                                                           | Connects OBF <sub>A</sub> / output to J1-18.   |                                                  | <ul> <li>Bit 4 — Port X0 Strobe<br/>(STB/) input.</li> </ul>                                        |

|                     |                                                         |                        | *E25-E26                             | E13-E16<br>or                                                     | Connects INT <sub>A</sub> output to<br>MINTR1. |                                                  | Bit 5 — Port X0 input<br>Buffer Full (IBF) output.                                                  |

| 1 1111111           |                                                         |                        |                                      | E13-E18                                                           | Connects INT <sub>A</sub> output to<br>MINTR0. |                                                  | <ul> <li>Bit 6 — Port X0 Ac-<br/>knowledge (ACK/) in-<br/>put.</li> </ul>                           |

|                     |                                                         |                        |                                      |                                                                   |                                                |                                                  | <ul> <li>Bit 7 — Port X0 Output<br/>Buffer Full (OBF/) out-<br/>put.</li> </ul>                     |

| X1                  | 0 Input                                                 | T: XU5, XU6            | None                                 | None                                                              |                                                | X0                                               | None.                                                                                               |

|                     |                                                         |                        |                                      |                                                                   |                                                | X2                                               | None; Port X2 can be in<br>Mode 0, input or output, if<br>Port X0 is also in Mode 0.                |

| *Defa               | ult jumper conn                                         | ected at the factory.  | L                                    |                                                                   | L                                              |                                                  |                                                                                                     |

### Table 2-5. Port Configuration Jumpers For Multimodule<sup>™</sup> Board (Continued)

| Port          | Mode      | Driver (D)/      |                                       | Jumper C                                     | Restrictions                                                                                                                                                        |                                                                      |                                                                                                                                                                                                                                                                                                       |

|---------------|-----------|------------------|---------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 011         | Mode      | Terminator (T)   | Delete                                | Add                                          | Effect                                                                                                                                                              | Port                                                                 | neathchona                                                                                                                                                                                                                                                                                            |

| X1            | 0 Output  | D: XU5, XU6      | None                                  | None                                         |                                                                                                                                                                     | X0                                                                   | None                                                                                                                                                                                                                                                                                                  |

|               | (latched) |                  |                                       |                                              |                                                                                                                                                                     | X2                                                                   | None; Port X2 can be in<br>Mode 0, input or output, if<br>Port X0 is also in Mode 0.                                                                                                                                                                                                                  |

| X1            | 1 Input   | T: XU3, XU5, XU6 |                                       | *E9-E10                                      | Connects IBF <sub>B</sub> output                                                                                                                                    | X0                                                                   | None.                                                                                                                                                                                                                                                                                                 |

|               | (strobed) | D: XU4           | *E25-E26<br>*E11-E12<br>*E7-E8        | E26-E11<br>E7-E16<br>or<br>E7-E18            | to J1-22.<br>Connects J1-32 to<br>STB <sub>B</sub> / input.<br>Connects INT <sub>B</sub> output to<br>MINTR1.<br>Connects INT <sub>B</sub> output to<br>MINTR0.     | X2                                                                   | <ul> <li>Port X2 bits perform the following:</li> <li>Bit 0 — Port X1 interrupt (PB INTR) to interrupt (PB INTR) to interrupt jumper matrix.</li> <li>Bit 1 — Port X1 Input Buffer Full (IBF) output.</li> </ul>                                                                                      |

|               |           |                  |                                       |                                              |                                                                                                                                                                     |                                                                      | <ul> <li>Bit 2 — Port X1 Strobe<br/>(STB/) input.</li> <li>Bits 3, 4, 5, 6, 7 — Depends on Port X0 mode.</li> </ul>                                                                                                                                                                                   |

| X1            |           |                  | *E9-E10                               | Connects OBF <sub>B</sub> / output           | X0                                                                                                                                                                  | None.                                                                |                                                                                                                                                                                                                                                                                                       |

|               | (latched) | D: XU4, XU5, XU6 | *E11-E12<br>and<br>*E25-E26<br>*E7-E8 | E11-E26<br>E7-E16<br>or<br>E7-E18            | output J1-22.<br>Connects J1-32 to<br>ACK <sub>B</sub> / input.<br>Connects INT <sub>B</sub> output to<br>MINTR1.<br>Connects INT <sub>B</sub> output to<br>MINTR0. | X2                                                                   | <ul> <li>Port X2 bits perform the following:</li> <li>Bit 0 — Port X1 interrupt (PB INTR) to interrupt jumper matrix.</li> <li>Bit 1 — Port X1 Output Buffer Full (OBF/) output.</li> <li>Bit 2 — Port X1 Acknowledge (ACK/) input.</li> <li>Bits 3, 4, 5, 6, 7 — Depends on Port X0 mode.</li> </ul> |

| X2<br>(upper) | 0 Input   | T: XU3           | None                                  | *E19-E20<br>*E21-E22<br>*E23-E24<br>*E25-E26 | Connects bit 4 to J1-26.<br>Connects bit 5 to J1-28.<br>Connects bit 6 to J1-30.<br>Connects bit 7 to J1-32.                                                        | X0<br>X1                                                             | Port X0 must be in Mode 0<br>for all four bits to be avail-<br>able.<br>Port X1 must be in Mode 0<br>for all four bits to be avail-<br>able.                                                                                                                                                          |

| X2<br>(lower) | 0 Input   | T: XU4           | None                                  | *E7-E8<br>*E9-E10<br>*E11-E12<br>*E13-E14    | Connects bit 0 to J1-24.<br>Connects bit 1 to J1-22.<br>Connects bit 2 to J1-20.<br>Connects bit 3 to J1-18.                                                        | XO                                                                   | Port X0 must be in Mode 0<br>for all four bits to be avail-<br>able.                                                                                                                                                                                                                                  |

|               |           |                  |                                       |                                              | X1                                                                                                                                                                  | Port X1 must be in Mode 0<br>for all four bits to be avail-<br>able. |                                                                                                                                                                                                                                                                                                       |

### Table 2-5. Port Configuration Jumpers For Multimodule<sup>™</sup> Board (Continued)

| Port Mode     | <b>111</b>            | Driver (D)/ | Jumper Configuration |                                              |      |              |                                              |  |

|---------------|-----------------------|-------------|----------------------|----------------------------------------------|------|--------------|----------------------------------------------|--|

|               | Terminator (T)        | Delete      | Add                  | Effect                                       | Port | Restrictions |                                              |  |

| X1<br>(upper) | 0 Output<br>(latched) | D: XU3      | None                 | Same as for Port X2 (upper) mode<br>0 Input. |      | хо           | Same as for Port X2<br>(upper) Mode 0 Input. |  |

| X1<br>(lower) | 0 Output<br>(latched) | D: XU4      | None                 | Same as for Port X2 (lower) Mode<br>0 Input. |      | X2           | Same as for Port X2<br>(lower) Mode 0 Input. |  |

Table 2-5. Port Configuration Jumpers For Multimodule<sup>™</sup> Board (Continued)

### 2-11. LINE DRIVERS AND I/O TERMINATORS

All 24 I/O lines on the Multimodule board can be buffered with drivers or terminators at sockets XU1, XU2, XU3, XU4, XU5, and XU6 on the board. The 24 I/O lines may be divided into three groups of eight. The group labeled Port A is connected to the socketed 8226 Bidirectional Bus Driver devices. Unlike Port B and Port C, Port A may be used in the "as-shipped" configuration with no additional components.

### NOTE

The 8226's are inverting devices. You may wish to substitute Intel 8216 non-inverting bidirectional bus driver devices, as required by the application.

Port B and Port C each interface to two sockets compatible with any 7400 pinout type driver. Table 2-6 lists some of the common drivers and their characteristics.

| Driver Characteristic <sup>1</sup> |       | I <sub>OL</sub> (mA)² | I <sub>он</sub> (mA) <sup>3</sup> |

|------------------------------------|-------|-----------------------|-----------------------------------|

| 7438                               | I,OC  | 48                    |                                   |

| 7437                               |       | 48                    | -1.2                              |

| 7432                               | NI    | 16                    | -0.8                              |

| 7426                               | I,OC  | 16                    |                                   |

| 7409                               | NI,OC | 16                    |                                   |

| 7408                               | NI    | 16                    | -0.8                              |

| 7403                               | I,OC  | 16                    | —                                 |

| 7400                               | 1     | 16                    | -0.4                              |

NOTES:

1. I = Inverting; OC = Open Collector; NI = Non Inverting.

2.  $I_{OL}$  specified for  $V_{OL} = 0.4$  Volt.

3.  $I_{OH}$  specified for  $V_{OH} = 2.4$  Volts.

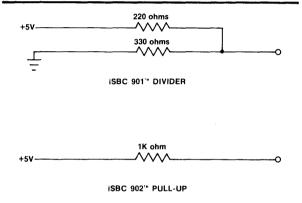

The Port B and Port C sockets are also compatible with two special terminator resistor packs available through Intel; the iSBC 901 Terminator and the iSBC 902 Pull-Up. The packs are shown in figure 2-3 and useful in interfacing to the Intel 8255A-5 PPI device in an input application.

Each of the Port C lines also includes two wirewrap posts that provide the flexibility needed to support all three modes of operation of the PPI. Uses for the wirewrap posts are contained in section 2-10.

### 2-12. INSTALLATION PROCEDURE

The Multimodule board mounts onto the host iSBC microcomputer. Install the board as follows:

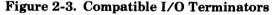

- a. With a non-metal  $\frac{1}{4}$  inch x 6/32 screw, secure the  $\frac{1}{2}$  inch plastic spacer to the host iSBC microcomputer as shown in figure 2-4.

- b. Locate pin 1 on the iSBX bus connector (P1) and align it with pin 1 of the iSBX bus connector on the host iSBC microcomputer.

- c. Align the Multimodule board mounting hole with the spacer on the host iSBC microcomputer; reference figure 2-1.

- d. Gently press the two boards together until the connector seats.

e. Secure the Multimodule board to the top of the spacer with the other  $\frac{1}{4}$  inch x 6/32 screw.

### NOTE

The placement of an installed Multimodule board and the host board connector number may vary according to the type of host iSBC microcomputer that is used.

### CHAPTER 3 PROGRAMMING INFORMATION

### **3-1. INTRODUCTION**

This chapter describes the programming of the iSBX 350 Parallel Multimodule Board, which entails programming the 8255A-5 Programmable Peripheral Interface (PPI). Three basic modes of operation for the PPI are supported; the basic Input/Output mode (Mode 0), the strobed Input/Output mode (Mode 1), and the Bidirectional Bus mode (Mode 2).

### **3-2. PPI PROGRAMMING**

The PPI programming presented in the following text consists of sections on addressing, control word format, initialization, and operation of the PPI. Examples are included for a typical PPI port READ and port WRITE subroutine.

### **3-3. ADDRESSING**

The PPI uses four consecutive addresses either X0 through X3 or X4 through X7 for the Multimodule board for data transfer and for port control. (Refer to table 3-1.) In some instances there may be more than one connector for a Multimodule board on the host iSBC microcomputer; each connector requires its own port address. In the examples in the following text, the first digit of the port address (X) is determined by the host iSBC microcomputer.

Table 3-1. Port Addresses

| 8255<br>Ports | Multimodule™ Connector<br>Address |

|---------------|-----------------------------------|

| Port A        | X0 or X4                          |

| Port B        | X1 or X5                          |

| Port C        | X2 or X6                          |

| Control       | X3 or X7                          |

| Reserved      | X8 to XF                          |

NOTE: The first digit of each port I/O address is listed as "X" since it will change dependent on the type of host iSBC microcomputer used. Refer to the Hardware Reference Manual for your host iSBC microcomputer to determine the first digit of the port address.

### NOTE

Note that addresses X8 through XF on the host microcomputer are reserved for the Multimodule board and must not be used by another device when the Multimodule board is installed onto the host iSBC microcomputer.

### **3-4. CONTROL WORD FORMAT**

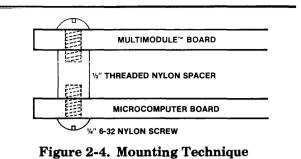

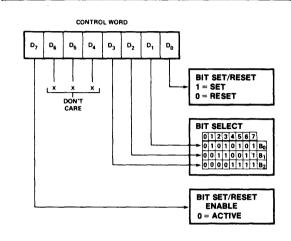

The control word format shown in figure 3-1 is used to initialize the PPI to define the operating mode of the three ports. Note that the ports are separated into two groups. Group A (control word bits 3

Figure 3-1. PPI Control Word Format

through 6) defines the operating mode for Port A (address X0 or X4) and the upper four bits of Port C (address X2 or X6). Group B (control word bits X0 through X2) defines the operating mode for Port B (address X1 or X5) and the lower four bits of Port C (address X2 or X6). Bit 7 of the control word reflects the mode set flag.

### **3-5. INITIALIZATION**

To initialize the PPI, write a control word to port address X3 (or X7). Refer to figure 3-1 and table 3-2and assume that the control word is 92 (hexadecimal). This initializes the PPI as follows:

- a. Mode Set Flag active

- b. Port A (X0 or X4) set to Mode 0 Input

- c. Port C (X2 or X6) upper set to Mode 0 Output

- d. Port B (X1 or X5) set to Mode 0 Input

- e. Port C (X2 or X6) lower set to Mode 0 Output

### **3-6. OPERATION**

After the PPI has been initialized, the operation is simply performing a READ or a WRITE to the appropriate port. **3-7. READ OPERATION.** A typical read subroutine for Port A is given in table 3-3.

**3-8. WRITE OPERATION.** A typical write subroutine for Port C is given in table 3-4. As shown in figure 3-2, any of the Port C bits can be selectively set or cleared by writing a control word to address X3.

### Figure 3-2. PPI Port C Bit Set/Reset Control Word Format

#### Table 3-2. Typical PPI Initialization Subroutine

| USES-A: [ | NITIALIZES I<br>DESTROYS-A | PARALLEL PORTS.    |                                                           |

|-----------|----------------------------|--------------------|-----------------------------------------------------------|

| INT PAR:  | MVI<br>OUT<br>RET<br>END   | A,92H<br>BASAD + 3 | MODE WORD TO PPI PORT A & B IN, C OUT<br>BASE ADDRESS + 3 |

|           |                            |                    |                                                           |

#### Table 3-3. Typical PPI Port READ Subroutine

| ;AREAD READS A BYTE FROM PORT A INTO REG A.<br>:USES-A; DESTROYS-A. |           |       |                           |  |  |  |  |

|---------------------------------------------------------------------|-----------|-------|---------------------------|--|--|--|--|

| AREAD:                                                              | IN<br>RET | BASAD | INPUT BYTE (BASE ADDRESS) |  |  |  |  |

| <br>                                                                | END       |       |                           |  |  |  |  |

### Table 3-4. Typical PPI Port WRITE Subroutine

| ;COUT OUTPUTS A BYTE FROM REG A TO PORT C.<br>;USES-A; DESTROYS-NOTHING. |            |           |                                |  |

|--------------------------------------------------------------------------|------------|-----------|--------------------------------|--|

| COUT:                                                                    | OUT<br>RET | BASAD + 2 | OUTPUT BYTE (BASE ADDRESS + 2) |  |

|                                                                          | END        |           |                                |  |

### CHAPTER 4 PRINCIPLES OF OPERATION

### 4-1. INTRODUCTION

This chapter presents the principles of operation of the iSBX 350 Parallel Multimodule Board. Included are sections covering the interfaces between the host microcomputer and the Multimodule board and between the parallel I/O lines and the Multimodule board. The interfaces to the Multimodule board and the interrupt system are detailed in the following text.

### 4-2. iSBX<sup>™</sup> BUS INTERFACE

The interface to the host iSBC microcomputer consists of several signals which control the Multimodule board functions. Each signal is described in the following paragraphs and shown in the schematic diagram, included as figure 5-2.

RESET (Reset). This active high signal to the PPI provides initialization for the chip, resets the control register, and conditions all 8255A-5 ports to the input mode. RESET is derived from the microprocessor reset signal in the host iSBC microcomputer.

IOWRT/ (Write). This active low input to the Multimodule board indicates that data or a command is to be written into the PPI from the iSBX bus (MD0-MD7). Reference table 4-1.

IORD/ (Read). This active low input indicates that data is to be read from the PPI and made available on the iSBX bus (MD0-MD7). Reference table 4-1.

MCSO/ (Chip Select). This active low input selects the PPI, enabling communication between the PPI and the host iSBC microcomputer. Reference table 4-1.

MA0, MA1 (Address lines). The active high inputs to the Multimodule board, in conjunction with the IORD/ and IOWRT/ lines, control selection of one of three ports or the Control Word Register in the PPI. Reference table 4-1.

MD0-MD7 (Bidirectional Data Bus). These active high lines provide the interface for data and command transfer between the PPI and the host iSBC microcomputer.

MPST/ (Module present). This active low output signal indicates to the host iSBC microcomputer that a Multimodule board has been installed.

OPT0, OPT1 (Option signals). These user-defined signals are included to provide application flexibility for the Multimodule board. These signals, if required by the application, must be user-configured via jumpers.

MINTRO, MINTR1 (Interrupt signals). These signals are included to provide interrupt generation on the Multimodule board. These signals, if required by the application, must be user-configured via jumpers.

| MA1 | MAO     | IORD/ | IOWRT/                                | MCS0/ | INPUT OPERATION (READ)   |

|-----|---------|-------|---------------------------------------|-------|--------------------------|

| 0   | 0       | 0     | 1                                     | 0     | Port A - Data Bus        |

| 0   | 1       | 0     | 1                                     | 0     | Port B - Data Bus        |

| 1   | 0       | 0     | 1                                     | 0     | Port C - Data Bus        |

| 1   | 1       | 0     | 1                                     | 0     | Illegal Condition        |

|     | •       |       | · · · · · · · · · · · · · · · · · · · |       | OUTPUT OPERATION (WRITE) |

| 0   | 0       | 1     | 0                                     | 0     | Data Bus - Port A        |

| 0   | 1       | 1     | 0                                     | 0     | Data Bus - Port B        |

| 1   | 0       | 1     | 0                                     | 0     | Data Bus - Port C        |

| 1   | 1       | 1     | 0                                     | 0     | Data Bus - Control       |

|     | · · · · |       |                                       |       | DISABLE FUNCTION         |

| x   | x       | ×     | x                                     | 1     | Data Bus - 3-State       |

| х   | x       | 1     | 1                                     | x     | Data Bus - 3-State       |

### 4-3. PORT INTERFACE

The parallel port I/O (via connector J1) on the Multimodule board consists of three 8-bit ports that may be configured in one of several modes, as listed in table 4-2. The eight bits of Port A and eight bits of Port B must be configured as units to either input or output mode, but Port C may be broken into two groups of four, either of which can be used in input and/or output mode.

Data I/O through Port A passes through two 8226 Bidirectional Bus Drivers (U1 and U2) which control the direction of data flow according to the condition of DIEN/, the signal on jumper post E2. When DIEN/ is low, data flows from the PPI to the port data lines. Conversely, when DIEN/ is high, data flows from the port data lines to the PPI.

Four 14-pin DIP sockets are provided for usersupplied line driver/receiver device installation onto the Port B and Port C data lines. The type of line driver/receiver device is determined by the application.

|                 | Mode 0 |     | Mode 1             |                    | Mode 2             |  |

|-----------------|--------|-----|--------------------|--------------------|--------------------|--|

| Port/Bit        | IN     | Ουτ | IN                 | Ουτ                | GROUP A ONLY       |  |

| PAo             | IN     | OUT | IN                 | OUT                | Bidirectional      |  |

| PA <sub>1</sub> | IN     | OUT | IN                 | OUT                | Bidirectional      |  |

| PA <sub>2</sub> | IN     | OUT | IN                 | OUT                | Bidirectional      |  |

| PA₃             | IN     | OUT | IN                 | OUT                | Bidirectional      |  |

| PA₄ ,           | IN     | OUT | IN                 | OUT                | Bidirectional      |  |

| PAs             | IN     | OUT | IN                 | OUT                | Bidirectional      |  |

| PA <sub>6</sub> | IN     | ООТ | IN                 | OUT                | Bidirectional      |  |

| PA <sub>7</sub> | IN     | OUT | IN                 | OUT                | Bidirectional      |  |

| PBo             | IN     | ОUT | IN                 | OUT                | _                  |  |

| PB <sub>1</sub> | IN     | OUT | IN                 | OUT                | _                  |  |

| PB₂             | IN     | OUT | IN                 | OUT                | _                  |  |

| PB₃             | IN     | OUT | IN                 | OUT                | _                  |  |

| PB₄             | IN     | OUT | IN                 | OUT                | _                  |  |

| PB₅             | IN     | OUT | IN                 | OUT                | _                  |  |

| PB <sub>6</sub> | IN     | OUT | IN                 | OUT                | _                  |  |

| PB7             | IN     | OUT | IN                 | OUT                | -                  |  |

| PCo             | IN     | OUT | INTR <sub>8</sub>  | INTR <sub>B</sub>  | 1/0                |  |

| PC <sub>1</sub> | IN     | OUT | IBF <sub>B</sub>   | OBF₀/              | 1/0                |  |

| PC <sub>2</sub> | IN     | ООТ | STB <sub>B</sub> / | ACK <sub>B</sub> / | 1/0                |  |

| PC₃             | IN     | ООТ | INTRA              | INTRA              | INTRA              |  |

| PC₄             | IN     | ООТ | STB <sub>A</sub> / | 1/0                | STB <sub>A</sub> / |  |

| PC₅             | IN     | OUT | IBF <sub>A</sub>   | 1/0                | IBF <sub>A</sub>   |  |

| PC <sub>6</sub> | IN     | ОИТ | 1/0                | ACK <sub>A</sub> / | ACK <sub>A</sub> / |  |

| PC <sub>7</sub> | IN     | ООТ | 1/0                | OBF <sub>A</sub> / | OBF <sub>A</sub> / |  |

Table 4-2. Mode Definition Summary Table

# CHAPTER 5 SERVICE INFORMATION

### **5-1. INTRODUCTION**

This chapter provides a list of replaceable parts, service diagrams, and service and repair assistance instructions for the iSBX 350 Parallel Multimodule Board.

### **5-2. REPLACEABLE PARTS**

Table 5-1 provides a list of replaceable parts for the Multimodule board. Table 5-2 identifies and locates the manufacturers specified in the MFR CODE column in table 5-1. Intel parts that are available on the open market are listed in the MFR CODE column as "COML"; every effort should be made to procure these parts from a local (commercial) distributor.

### 5-3. SERVICE DIAGRAMS

The parts location diagram and schematic diagram for the Multimodule board are provided in Figures 5-1 and 5-2, respectively. On the schematic diagram, a signal mnemonic that ends with a slash (e.g. MCSO/) is active low. Conversely, a signal mnemonic without a slash (e.g. OPT0) is active high.

### Table 5-2. Manufacturer Codes

| Mfr. Code | Manufacturer               | Address         |  |

|-----------|----------------------------|-----------------|--|

| AMP       | AMP, Inc.                  | Harrisburg, PA  |  |

| INTEL     | Intel Corporation          | Santa Clara, CA |  |

| ТІ        | Texas Instruments          | Dallas, TX      |  |

| COML      | Any Commercial Source      |                 |  |

|           | Order By Description (OBD) |                 |  |

### 5-4. SERVICE AND REPAIR ASSISTANCE

United States customers can obtain service and repair assistance from Intel by contacting the MCSD Technical Support Center in Santa Clara, California at one of the following numbers:

Telephone:

From Alaska, Arizona, or Hawaii call: (602) 869-4600

From all other U.S. locations call toll free: (800) 528-0595

TWX Number: 910-951-1330

| Reference<br>Designation | Description                                   | Mfg. Part<br>No. | Mfr.<br>Code | Qty. |

|--------------------------|-----------------------------------------------|------------------|--------------|------|

| U1, U2                   | IC, 8226 Bidirectional Data Buffer            | 8226             | INTEL        | 2    |

| XU3,XU4,XU5,XU6          | Socket, 14-pin DIP                            | C93-14-02        | тι           | 4    |

| U7                       | IC, 8255A-5 Programmable Peripheral Interface | P8255A-5         | INTEL        | 1    |

| R1                       | Resistor, 1K, ¼W, 5%                          | OBD              | COML         | 1    |

| RP1                      | Resistor Pack, 10-pin, 1K 2%                  | OBD              | COML         | 1    |

| C7                       | Capacitor, tant, 22µf, 15V, 10%               | OBD              | COML         | 1    |

| C1,C2,C3,C4,<br>C5,C6,C8 | Capacitor, 0.1μf, 50V<br>+80% -20%            | OBD              | COML         | 7    |

| P1                       | Connector, 36 pin, male                       | 103109-001       | INTEL        | 1    |

| E1-E26                   | Post, Wire wrap                               | 87022-1          | AMP          | 26   |

| XU1,XU2                  | Socket, 16-pin DIP                            | C93-16-02        | ті           | 2    |

### Table 5-1. Replaceable Parts

Always contact the MCSD Technical Support Center before returning a product to Intel for service or repair. You will be given a "Repair Authorization Number", shipping instructions, and other important information which will help Intel provide you with fast, efficient service. If the product is being returned because of damage sustained during shipment from Intel, or if the product is out of warranty, a purchase order is necessary in order for the MCSD Technical Support Center to initiate the repair.

In preparing the product for shipment to the MCSD Technical Support Center, use the original factory packaging material, if available. If the original packaging is not available, wrap the product in a cushioning material such as Air Cap TH-240 (or equivalent) manufactured by the Sealed Air Corporation, Hawthorne, N.J., and enclose in a heavy-duty corrugated shipping carton. Seal the carton securely, mark it "FRAGILE" to ensure careful handling, and ship it to the address specified by MCSD Technical Support Center personnel.

### NOTE

Customers outside of the United States should contact their sales source (Intel Sales Office or Authorized Intel Distributor) for directions on obtaining service or repair assistance.

### REQUEST FOR READER'S COMMENTS

Intel Corporation attempts to provide documents that meet the needs of all Intel product users. This form lets you participate directly in the documentation process.

Please restrict your comments to the usability, accuracy, readability, organization, and completeness of this document.

1. Please specify by page any errors you found in this manual.

2. Does the document cover the information you expected or required? Please make suggestions for improvement.

3. Is this the right type of document for your needs? Is it at the right level? What other types of documents are needed?

4. Did you have any difficulty understanding descriptions or wording? Where?

5. Please rate this document on a scale of 1 to 10 with 10 being the best rating.

| NAME    |                 |         | DATE       |

|---------|-----------------|---------|------------|

| TITLE   |                 |         |            |

| COMPANY | NAME/DEPARTMENT | <u></u> |            |

| ADDRESS |                 |         |            |

| CITY    |                 | STATE   | _ ZIP CODE |

|         |                 |         |            |

Please check here if you require a written reply.

### WE'D LIKE YOUR COMMENTS . . .

This document is one of a series describing Intel products. Your comments on the back of this form will help us produce better manuals. Each reply will be carefully reviewed by the responsible person. All comments and suggestions become the property of Intel Corporation.

#

NO POSTAGE NECESSARY IF MAILED IN THE UNITED STATES

# BUSINESS REPLY MAIL

FIRST CLASS PERMIT NO. 79 BEAVERTON, OR

POSTAGE WILL BE PAID BY ADDRESSEE

Intel Corporation 5200 N.E. Elam Young Pkwy. Hillsboro, Oregon 97123

**OMO Technical Publications**

1

### INTEL CORPORATION, 3065 Bowers Avenue, Santa Clara, California 95051 (408) 987-8080

Printed in U.S.A.

OM-083/1.2K/0184/OSPS iSBC