# int

**APPLICATION** NOTE

August 1977

Related Intel Publications

"MCS-48<sup>™</sup> Microcomputer User's Manual"

"Using the 8251 Universal Synchronous/Asynchronous Receiver/Transmitter"

"8255 Programmable Peripheral Interface Applications"

# Contents

|                                    | INTRODUCTION                                                 |

|------------------------------------|--------------------------------------------------------------|

|                                    | THE MCS-48 <sup>™</sup> FAMILY 1                             |

| Application Techniques             | ANALOG I/O                                                   |

| for the MCS-48 <sup>™</sup> Family | RECEIVING SERIAL CODES _<br>BASIC APPROACHES 8               |

|                                    | RECEIVING SERIAL CODE – A MOKE<br>SOPHISTICATED ALGORITHM 12 |

|                                    | TRANSMITTING SERIAL CODE 22                                  |

|                                    | GENERATING PARITY 22                                         |

|                                    | CONCLUSION 23                                                |

|                                    |                                                              |

# INTRODUCTION

The INTEL<sup>®</sup> MCS-48<sup>TM</sup> family consists of a series of seven parts, including three processors, which take advantage of the latest advances in silicon technology to provide the system designer with an effective solution to a wide variety of design problems. The significant contribution of the MCS-48 family is that instead of consisting of integrated microcomputer components it consists of integrated microcomputer systems. A single integrated circuit contains the processor, RAM, ROM (or PROM), a timer. and I/O.

This application note suggests a variety of application techniques which are useful with the MCS-48. Rather than presenting the design of a complete system it describes the implementation of "subsystems" which are common to many microprocessor based systems. The subsystems described are analog input and output, the use of tables for function evaluation, receiving serial code, transmitting serial code, and parity generation. After an overview of the MCS-48 family these areas are discussed in a more or less independent manner.

# THE MCS-48<sup>™</sup> FAMILY

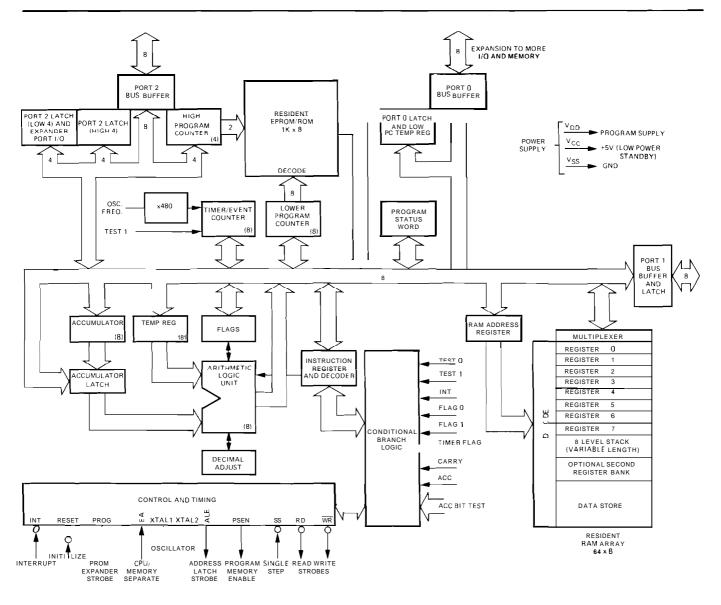

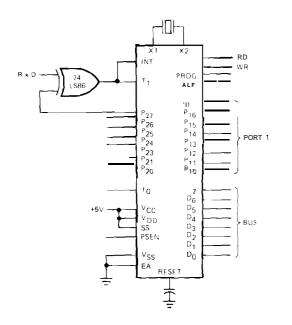

The processors in the MCS-48 family all share an identical architecture. The only significant difference is the type of on board program storage which is provided. The 8748 (see Figure 1) includes 1024 bytes of erasable, programmable, ROM (EPROM), the 8048 replaces the EPROM with an equivalent amount of mask programmed ROM, and the 8035 provides the CPU function with no on board program storage. All three of these processors

MCS-48<sup>™</sup> Internal Structure

# **INSTRUCTION SET**

|              | Mnemonic             | Description                         | Bytes | Cycle |            | Mnemonic                      | Description E                    | Bytes  | Cycles |

|--------------|----------------------|-------------------------------------|-------|-------|------------|-------------------------------|----------------------------------|--------|--------|

|              | ADD A,R              | Add register to A                   | 1     | 1     | Subroutine | CALL                          | Jump to subroutine               | 2      | 2      |

|              | ADD A. @R            | Add data memory to A                | 1     | 1     | E I        | RET                           | Return                           | 1      | 2      |

|              | ADD A, #data         | Add immediate to A                  | 2     | 2     | ق          | RETR                          | Return and restore status        | 1      | 2      |

|              | ADDC A, R            | Add register with carry             | 1     | 1     | ้ง         |                               |                                  |        |        |

|              | ADDC A, @R           | Add data memory with carry          | 1     | 1     |            | CLR C                         | Clear Carry                      | 1      | 1      |

|              | ADDC A, #data        | Add immediate with carry            | 2     | 2     |            | CPL C                         | Complement Carry                 | 1      | 1      |

|              | ANLA, R              | And register to A                   | 1     | 1     | Flags      | CLR FO                        | Clear Flag 0                     | 1      | 1      |

|              | ANLA, @R             | And data memory to A                | 1     | 1     | Ē          | CPL FO                        | Complement Flag 0                | 1      | 1      |

|              | ANLA.#data           | And immediate to A                  | 2     | 2     |            | CLR F1                        | Clear Flag 1                     | 1      | 1      |

| 5            | ORL A, R             | Or register to A                    | 1     | 1     |            | CPL F1                        | Complement Flag 1                | 1      | 1      |

| atc          | ORL A, @R            | Or data memory to A                 | 1     | 1     |            |                               |                                  |        |        |

| Accumulator  | ORL A, #data         | Or immediate to A                   | 2     | 2     |            |                               | Move register to A               | 1      | 1      |

| 5            | XRLA, <b>R</b>       | Exclusive Or register to A          | 1     | 1     |            | MOV A, R                      | Move register to A               | 1<br>1 | 1      |

| AC.          | XRLA, @R             | Exclusive or data memory to A       | 1     | 1     |            | MOV A, @R                     | Move data memory to A            |        |        |

|              | XRLA.#data           | Exclusive or immediate to A         | 2     | 2     |            | MOV A, #data                  | Move immediate to A              | 2      | 2      |

|              | INC A                | Increment A                         | 1     | 1     |            | MOV R, A                      | Move A to register               | 1      | 1<br>1 |

|              | DEC A                | Decrement A                         | 1     | 1     |            | MOV @R,A                      | Move A to data memory            | 1      |        |

|              | CLR A                | Clear A                             | 1     | 1     | <u></u>    | MOV R, #data<br>MOV @R, #data | Move immediate to register       | 2      | 2      |

|              | CPL A                | Complement A                        | 1     | 1     | Data Mov   | • • •                         |                                  |        | 2      |

|              | DAA                  | Decimal Adjust A                    | 1     | 1     | ate        | MOV A, PSW                    | Move PSW to A                    | 1      | 1      |

|              | SWAP A               | Swap nibbles of A                   | 1     | 1     |            | MOV PSW, A                    | Move A to PSW                    | 1      | 1      |

|              | RLA                  | Rotate A left                       | 1     | 1     |            | XCH A, R                      | Exchange A and register          | 1      | 1      |

|              | RLC A                | Rotate A left through carry         | 1     | 1     |            | XCH A, @R                     | Exchange A and data memory       | 1      | 1      |

|              | RR A                 | Rotate A right                      | 1     | 1     |            | XCHD A, @R                    | Exchange nibble of A and registe |        | 1      |

|              | RRC A                | Rotate A right through carry        | 1     | 1     |            | MOVX A, @R                    | Move external data memory to A   |        | 2      |

|              |                      |                                     |       |       |            |                               | Move A to external data memory   |        | 2      |

|              | IN A,P               | Input port to A                     | 1     | 2     |            | MOVP A, @ A                   | Move to A from current page      | 1      | 2      |

|              | OUTL P, A            | Output A to port                    | 1     | 2     |            | MOV P3 A, @ A                 | Move to A from Page 3            | 1      | 2      |

|              | ANLP, #data          | And immediate to port               | 2     | 2     |            |                               |                                  |        |        |

| 5            | ORL P, #data         | Or immediate to port                | 2     | 2     |            |                               |                                  |        |        |

| Input/Output | INS A, BUS           | Input BUS to A                      | 1     | 2     |            | MOV A, T                      | Read Timer/Counter               | 1      | 1      |

| ĮÕ           | OUTL BUS, A          | Output A to BUS                     | 1     | 2     | r/Count    | ΜΟΥ Τ, Α                      | Load Timer/Counter               | 1      | 1      |

| Ľ,           | ANL BUS, #data       | And immediate to BUS                | 2     | 2     | Į Ž        | STRTT                         | Start Timer                      | 1      | 1      |

| <u> </u>     | ORL BUS, #data       | Or immediate to BUS                 | 2     | 2     | 1 2        | STRTCNT                       | Start Counter                    | 1      | 1      |

|              | MOVD A, P            | Input Expander port to A            | 1     | 2     |            | STOP TCNT                     | Stop TimerlCounter               | 1      | 1      |

|              | MOVD P, A            | Output A to Expander port           | 1     | 2     | <b>⊢</b>   | EN TCNTI                      | Enable Timer/Counter Interrupt   | 1      | 1      |

|              | ANLD P, A            | And A to Expander port              | 1     | 2     |            | DIS TCNTI                     | Disable Timer/Counter Interrup   | 1      | 1      |

|              | ORLD P, A            | Or A to Expander port               | 1     | 2     |            |                               |                                  |        |        |

| ers          | INC R                | Increment register                  | 1     | 1     |            | EN I                          | Enable external interrupt        | 1      | 1      |

| Registers    | INC @R               | Increment data memory               | 1     | 1     |            | DISI                          | Disable external interrupt       | 1      | 1      |

| 3eg          | DEC R                | Decrement register                  | 1     | 1     | 5          | SELRBO                        | Select register bank 0           | 1      | 1      |

|              |                      |                                     | -     |       | Ħ          | SEL RB1                       | Select register bank 1           | 1      | 1      |

| ]            |                      |                                     | 2     | 2     | S          | SEL MBO                       | Select memory bank 0             | 1      | 1      |

|              | JMP addr<br>JMPP @ A | Jump unconditional<br>Jump indirect | 2     | 2     | -          | SEL MB1                       | Select memory bank 1             | 1      | 1      |

|              |                      |                                     | 1     | 2     |            | ENTOCLK                       | Enable Clock output on TO        | 1      | 1      |

|              | DJNZ R, addr         | Decrement register and skip         | 2     | 2     |            |                               |                                  |        |        |

|              | JC addr              | Jump on Carry ≈ 1                   | 2     | 2     |            |                               |                                  | _      |        |

|              | JNC addr             | Jump on Carry = 0                   | 2     | 2     |            | NOP                           | No Operation                     | 1      | 1      |

|              | J Z addr             | Jump on A Zero                      | 2     | 2     |            | NOF                           |                                  | 1      | 1      |

| ء            | JNZ addr             | Jump on A not Zero                  | 2     | 2     |            |                               |                                  |        |        |

| Branch       | JTO addr             | Jump on TO = 1                      | 2     | 2     |            |                               |                                  | _      |        |

| Bra          | JNTO addr            | Jump on TO = 0                      | 2     | 2     |            |                               |                                  |        |        |

| -            | JT1 addr             | Jump on $T1 = 1$                    | 2     | 2     | I          |                               |                                  |        |        |

|              | JNT1 addr            | Jump on $T1 = 0$                    | 2     | 2     |            |                               |                                  |        |        |

|              | JFO addr             | Jump on FO = 1                      | 2     | 2     |            | Mnemonics                     | copyright Intel Corporation 1976 |        |        |

|              | JF1 addr             | Jump  on  F1 = 1                    | 2     | 2     |            | WINE THUR IICS                | septingin inter corporation 1970 |        |        |

|              | JTF addr             | Jump on timer flag                  | 2     | 2     |            |                               |                                  |        |        |

|              | JNI addr             | Jump on INT = 0                     | 2     | 2     |            |                               |                                  |        |        |

| 1            | JBb addr             | Jump on Accumulator Bit             | 2     | 2     |            |                               |                                  |        |        |

operate from a single 5-volt power supply. The 8748 requires an additional 25-volt supply only while the on board EPROM is being programmed. When installed in a system only the 5-volt supply is needed. Aside from program storage, these chips include 64 bytes of data storage (RAM), an eight bit timer which can also be used to count external events, 27 programmable I/O pins and the processor itself. The processor offers a wide range of instruction capability including rnany designed for bit, nibble, and byte manipulation. The instruction set is summarized in Figure 2.

Aside from the processors, the MCS-48 family includes 4 devices: one pure I/O device and 3 combination memory and I/O devices. The pure I/O device is the 8243, a device which is connected to a special 4 bit bus provided by the MCS-48 processors and which provides 16 I/O pins which can be programmatically controlled.

The combination memory and I/O devices consist of the 8355, the 8755, and the 8155. The 8355 and the 8755 both provide 2,048 bytes of program storage and two eight bit data ports. The only difference between these devices is that the 8355 contains masked program ROM and the 8755 contains EPROM. The 8155 combines 256 bytes of data storage (RAM), two eight bit data ports, a six bit control port, and a 14 bit programmable timer.

Figure 3 shows the various system configurations which can be achieved using the MCS-48 family of parts. It should also be noted that eight of the processors' I/O lines have been configured as a bidirectional bus which can be used to interface to standard Intel peripheral parts such as the 8251 USART (for serial I/O), the 8255A PPI (provides 24 I/O lines) and the complete range of memory components.

More detailed information concerning the MCS-48 family can be obtained from the "MCS-48 Microcomputer User's Manual" which provides a complete description of the MCS-48 family and its members. A general familiarity with this document will make the application techniques which follow easier to understand.

# ANALOG I/O

If analog I/O is required for a MCS-48<sup>™</sup> system there are many alternatives available from the makers of analog I/O modules. By searching through their catalogs it is possible to find almost any cornbination of features which is technically feasible. Perhaps the best example of such modules are the MP-10 and MP-20 hybrid modules recently introduced by Burr-Brown Research Corporation. The MP-10 provides two analog outputs and the MP-20 provides 16 analog inputs. Both of these units were

| 1088                                                                                        |                                              |             |                                                              | r of Ava<br>of Availa |                                                              | e Timers<br>/O Lines | 5                                                                |            |

|---------------------------------------------------------------------------------------------|----------------------------------------------|-------------|--------------------------------------------------------------|-----------------------|--------------------------------------------------------------|----------------------|------------------------------------------------------------------|------------|

| 1K                                                                                          | L_                                           |             |                                                              |                       |                                                              |                      | I                                                                |            |

|                                                                                             | 80                                           | 48          |                                                              | 35<br>55              |                                                              | 948<br>955           |                                                                  | 35<br>3355 |

|                                                                                             | 4-8                                          | 8155        | 4-8                                                          | 3155                  | 4-8                                                          | 8155                 | 4-8                                                              | 3155       |

| 832                                                                                         | [5]                                          | (101)       | [5]                                                          | (116)                 | [5]                                                          | (116)                | [5]                                                              | (131)      |

| 768                                                                                         | <br>                                         |             | _                                                            |                       | <u> </u>                                                     |                      |                                                                  |            |

| (W)                                                                                         |                                              | )48<br>8155 | 8035<br>8355<br>3-8155                                       |                       | 8048<br>8355<br>3-8155                                       |                      | 8035<br>2-8355<br>3-8155                                         |            |

| A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A | [4]                                          | (80)        | [4]                                                          | (95)                  | [4]                                                          | (95)                 | [4]                                                              | (110)      |

| ATA MEMORY (RAM)<br>215<br>825<br>825<br>825                                                |                                              | )48<br>8155 | 8035<br>8355<br>2-8155                                       |                       | 8048<br>8355<br>2-8155                                       |                      | 8035<br>2-8355<br>2-8155                                         |            |

| A T 330                                                                                     | [3]                                          | (59)        | [3]                                                          | (74)                  | [3]                                                          | (74)                 | [3]                                                              | (39)       |

| 256<br>256                                                                                  | 8048<br>8155<br>[2] (38)<br>8048<br>[1] (24) |             | 8035<br>8355<br>8155<br>[2] (53)<br>8035<br>8355<br>[1] (28) |                       | 8048<br>8355<br>8155<br>[2] (53)<br>8048<br>8355<br>[1] (28) |                      | 8035<br>2-8355<br>8155<br>[2] (68)<br>8035<br>2-8355<br>[1] (43) |            |

| 04                                                                                          |                                              |             |                                                              |                       |                                                              |                      |                                                                  |            |

|                                                                                             |                                              | 1           | ĸ                                                            | 2                     | ĸ                                                            | 3                    | ĸ                                                                | 4K         |

|                                                                                             | PROGRAM MEMORY (ROM)                         |             |                                                              |                       |                                                              |                      |                                                                  |            |

| Figure 3. | The Expanded MCS-4 | 8 <sup>™</sup> System |

|-----------|--------------------|-----------------------|

|-----------|--------------------|-----------------------|

specifically designed to interface with microprocessors.

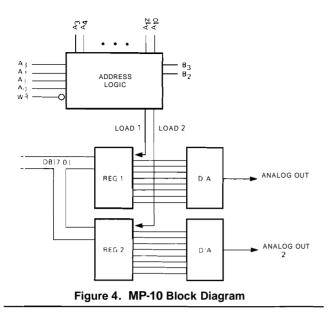

A block diagram of the MP-10 is shown in Figure 4. It consists of two eight bit digital to analog conferters, two eight bit latches which are loaded from the data bus, and address decoding logic to deterrnine when the latches should be loaded. The D/A converters each generate an analog output in the range of 10 volts with an output impedance of  $\Omega$ . Accuracy is  $\pm 0.4\%$  of full scale and the output is stable  $25\mu$ sec after the eight bit binary data is loaded into the appropriate latch. The latches are loaded by the write pulse (WR) whenever the proper address is presented to the MP-10. The lower two addresses (A<sub>0</sub> and A<sub>1</sub>) are used in-ernally by the device. Addresses A2 & A3 are compared with the address determination inputs  $B\gamma$ and B3. If their signals are found to be equal, and if addresses A4-A13 are all high, then the device is selected and one of the latches will be loadzd. Address bit A1 selects between output 1 and output 2. If address bit  $A_0$  is set then the initialization channel of the DIA is selected. In order to prepare for operation a data pattern of 80H must

be output to this channel following the reset of the device.

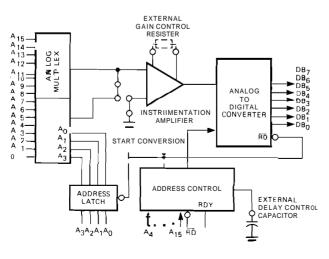

A block diagram of the MP-20 analog to digital converter is shown in figure 5. This unit consists of a 16 input analog multiplexer, an instrumentation amplifier, an eight bit successive approximation analog to digital converter, and control logic. The 16 input multiplexer can be used to input either 16 single ended or 8 differential inputs. The output from the multiplexer is fed into the instrumentation amplifier which is configured so that it can easily be strapped for single ended 0-5 volt inputs, single ended  $\pm 5$  volt inputs, or differential 0-5 volt signals. Provisions are made for an external gain control resistor on the amplifier. The gain control equation is:

$$G = 2 + \frac{50k\Omega}{Rext}$$

Figure 5. MP-20 Analog Subsystem

With no  $R_{ext}$  ( $R_{ext} = \infty$ ) the gain is two and the input is 0-5 or ±5 volts full scale. Adding an external resistor results in higher gain so that low level  $(\pm 50 \text{mV})$  signals from thermocouples and strain gauges can be accommodated. The output from the amplifier is applied to the actual A/D converter which provides an eight bit output with guaranteed monotonicity and an accuracy of  $\pm 0.4\%$ of full scale. Note that this accuracy is specified for the entire module, not just for the converter itself. The control logic monitors address lines A15 through A4 to determine when the address of the unit has been selected. An address that the unit will respond to is determined by 11 address control pins, labeled  $\overline{A4}$  through  $\overline{A14}$ . If one of these pins is tied to a logic 0 then the corresponding address pin must be high in order for the unit to be selected. If the pin is tied to a logic 1 then the corresponding address pin must be low. If the address of the module is selected when  $\overline{\text{MEMR}}$  pulse occurs, the lower four addresses  $(A_3-A_0)$  are stored in a latch which addresses the multiplexer. The coincidence of the proper address and  $\overline{\text{MEMR}}$  also initiates a conversion and gates the output of the converter on to the eight bit data bus.

The control logic of the MP-20 was designed to operate directly with an MCS-80<sup>TM</sup> system. When a MEMR occurs and a conversion is initiated the MP-20 generates a READY signal which is used to extend the cycle of the 8080A for the duration of the conversion. READY is brought high after the conversion is complete which allows the 8080A to initiate a conversion and read the resulting data in a single, albeit long, memory or I/O cycle. The conversion time of the MP-20 depends on the gain selected for the amplifier. With no external resistor (R =  $\infty$ ) the gain is two and the conversion time is 35 psec. For R = 510 $\Omega$  the gain is:

$$G = 2 + \frac{50k\Omega}{.51k\Omega} \cong 100$$

and the conversion time becomes  $100\mu$ sec. These settling times are specified in the MP-20 data sheet and range from 35 to 175 microseconds. The READY timing is controlled by an external capacitor. For a gain of 2 no external capacitor is required but if higher gains are selected a capacitor is needed to extend the timing.

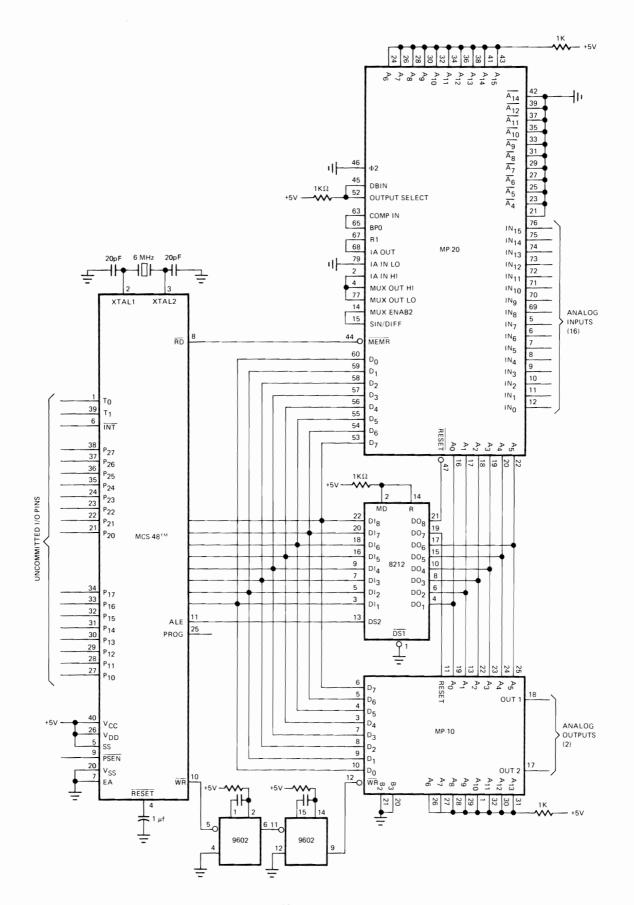

A schematic showing both the MP-10 D/A and the NIP-20 A/D connected to the 8748 is shown in Figure 6. This configuration, which consists of only four major components, gives an excellent example of what modern technology can do for

MCS-48<sup>™</sup> Based Analog Processor

the system designer. The four components provide:

- a. An eight bit microprocessor

- b. 64 bytes of RAM

- c. 1024 bytes of UV erasable PROM

- d. A timer/event counter

- e. 16 digital I/O pins

- f. 2 testable input pins

- g. An interrupt capability

- h. 16 eight bit analog inputs

- i. 2 eight bit analog outputs

The MCS-48 communicates with the D/A and A/Dconverters in a memory mapped mode (i.e., it treats the devices as if they were external RAM). By setting an address in either R0 or R1 and then executing a MOVX the software can transfer data between the accumulator and the analog I/O. When the MCS-48 executes the MOVX instruction it first sends the eight bit address out on the bus and strobes it into the 8212 latch with the ALE (Address Latch Enable) signal. After the address is latched, the MCS-48 uses the same bus to transfer data to or from the accumulator. If data is being sent out (MOVX  $\partial R_i$ , A) the WR strobe is used; if the data is being moved into the accumulator (MOVX A,  $\partial R_i$  the  $\overline{RD}$  strobe is used. The one shots on the  $\overline{WR}$  line are used to delay the write strobe of the MCS-48 to meet the data set up specifications of the MP-10.

In order to provide reset capability for the analog devices without dedicating an I/O pin from the MCS-48, special addresses are used as reset channels. Executing any MOVX with an address of 0XXXXXXX will reset the A/D module; a similar operation with an address of X1XXXXX will reset the D/A; a MOVX with an address of 01XXXXXX will reset both devices. All data transfers are accomplished with the upper two bits of the address field equal to 10. A summary of the addressing of the analog devices is shown in Table 1. Notice that except for an initialization channel for the D/A (which must

#### Table 1. Analog Interface Addresses

|         | INPUT OR OUTPUT               |                          |  |  |  |  |

|---------|-------------------------------|--------------------------|--|--|--|--|

| 0 X X X | $\times \times \times \times$ | Reset A/D                |  |  |  |  |

| X 1 X X | хххх                          | Reset D/A                |  |  |  |  |

|         | INPUT                         |                          |  |  |  |  |

| 0 0 1 1 | nnnn                          | Read A/D Channel n n n n |  |  |  |  |

|         | OUTPUT                        |                          |  |  |  |  |

| 1011    | 0001                          | Initialize D/A           |  |  |  |  |

| 1011    | 0000                          | Write Channel 1          |  |  |  |  |

| 1011    | 0010                          | Write Channel 2          |  |  |  |  |

be written to following a reset to initialize its internal logic) all channels involve some form of data transfer.

As was mentioned previously, the MP-20 was designed to use the READY line of the 8080A. Obviously this presents a problem since the MCS-48 does not support a READY line (with its attendant requirement of entering WAIT state). The necessity of a READY input can be overcome by performing a read operation to set the channel address, waiting the required delay (35  $\mu$ sec for a gain of two) and then performing a second read to actually obtain the data. The second read will read in the data from the channel selected by the first read irrespective of the channel selected for the second read. Thus it is possible to use the second read to set up the channel for the third read. Each read can read in the current channel and select the next channel for conversion.

The MP-20 is shown in Figure 6 strapped to input 16 single ended  $\pm 5$  volts signals. Programs which were used to test this configuration are shown in Figure 7. The first of these programs uses the D/A converter to generate sawtooth waveforms by outputting an incrementing value to the D/A converters. The second program scans the analog inputs and stores their digital values in a table located in RAM.

| LOC OBJ   | SEQ SOURCE STATEMENT                            |  |

|-----------|-------------------------------------------------|--|

|           | 0                                               |  |

|           | 1                                               |  |

|           | 2 :                                             |  |

|           | 3 : TEST PROGRAM FOR ANALOG OUTPUT              |  |

|           | 4 : THIS PROGRAM OUTPUTS A SAW-                 |  |

|           | 5 ; TOOTH WAVEFORM BY OUTPUTING                 |  |

|           | 6 ; AN INCREMENTING PATTRERN.                   |  |

|           | 7 ;                                             |  |

|           | 8                                               |  |

|           | 9;                                              |  |

|           | 10 ; EQUATES                                    |  |

|           | 11 ;                                            |  |

|           | 12                                              |  |

| ØØB3      | 13 INITCH EQU ØB3H ; D/A INITIALIZATION CHANNEL |  |

| 0080      | 14 INITOT EQU 80H ; D/A INITIALIZATION DATA     |  |

| 00B0      | 15 DATCH EQU ØBØH ; D/A DATA CHANNEL            |  |

|           | 16                                              |  |

|           | 17 ;<br>18 : START OF TEST                      |  |

|           | 18 ; START OF TEST<br>19 :                      |  |

| 0100      | 20 ORG 100H                                     |  |

| 0100      | 21 : INITIALIZE D/A                             |  |

| 0100 2380 | 22 START: MOV A. #INITOT                        |  |

| Ø102 B8B3 | 23 MOV RØ, #INITCH                              |  |

| 0104 90   | 24 MOVX (RØ,A                                   |  |

| 0101 70   | 25 : TEST LOOP-OUTPUT SAWTOOTH                  |  |

| Ø1Ø5 B8BØ | 26 LOOP: MOV RØ, #DATCH                         |  |

| 0107 17   | 27 INC A                                        |  |

| 0108 90   | 28 MOVX @RØ,A                                   |  |

| 0109 2405 | 29 JMP LOOP                                     |  |

|           | 30 ; END OF PROGRAM                             |  |

|           | 31 END                                          |  |

Figure 7a. D/A Exercise Program

| LAC UBJ                | ಸರ್ಶ               | SUURCE       | STATEMEN         | I                                                           |

|------------------------|--------------------|--------------|------------------|-------------------------------------------------------------|

|                        | ŵ                  |              |                  |                                                             |

|                        | 1                  |              |                  |                                                             |

|                        |                    |              |                  | LOG INPUT                                                   |

|                        |                    |              |                  | THE INPUT CHANNELS                                          |

|                        |                    |              |                  | DINGS IN A TABLE                                            |

|                        | 6 : 5'1            |              |                  |                                                             |

|                        |                    |              |                  |                                                             |

|                        | 8                  |              |                  |                                                             |

|                        | 9;                 |              |                  |                                                             |

|                        | 1J ; μUΑ           | قبالة.       |                  |                                                             |

|                        | 11 ;               |              |                  |                                                             |

|                        | 12                 |              |                  |                                                             |

| lo to zili             | 13 BUFF<br>14 MANU | Liyu         | 2011             | ; STARL OF BUFFER                                           |

| blut                   | 14 MAXON           | ليان         | 15               | ; NO OF ANALOG INPUTS                                       |

| ษยม                    | 15 AINCH           | Lul          | N PRH            | ; BASE ADDRESS OF A ALOG INPUTS<br>; EXECUTION TIME OF DUNZ |

| 5 d did                | 16 11CK            | եպե          | 2                | ; EXECUTION TIME OF LONG                                    |

|                        | 18 :               |              | -                |                                                             |

|                        | 19 ; 51AF          |              |                  |                                                             |

|                        | 20 ;               |              |                  |                                                             |

| ษไษย                   | 21                 | UKG          |                  |                                                             |

|                        | 22                 |              |                  | ; SETUP TO SCAN ANALLIG INPUTS                              |

| 0106 6926              | 23 5IAKI:          | Nov          | Rl,∦BU           | FF+MAXCH                                                    |

| 102 biskal             | 24                 | MOV          | R3,#MA           | JXCH                                                        |

| wlw4 BoBF              | 25                 | MOV          | HØ,#(A           | INCH+MAXCH)                                                 |

|                        | 26                 |              |                  | ; SELECT CHANNEL 15                                         |

| ulu6 cu                | 27                 | ⊡vX          | A, and           |                                                             |

| 1.7.000                | 28                 |              |                  | ; MAIT >40 MICROSECONES                                     |

| ⊌107 BC65<br>⊎109 LC09 | 29<br>3w           | MOV<br>DJINZ | R4,#40           | 1/11CK                                                      |

| 0109 1009              | 31                 | DOIND        | E.4.7.4          | : NOW SCAN ANALOGS                                          |

| WiwB it                | 32 Lever:          | DEC          | kω               | , non bart needad                                           |

| 0100 10                | 33                 |              |                  | ; GEI DAIA                                                  |

| WINC BU                | 14                 | NOVX         | A,eRU            |                                                             |

|                        | 35                 |              |                  | ; NOVE INTO BUFFER                                          |

| bløL Al                | 36                 | MUV          | enl,A            |                                                             |

|                        | 37                 |              |                  | DLCREMENT BUFFER POINT                                      |

| əluL C9                | Jo                 | DEC          | ы                |                                                             |

|                        | 39                 |              | <b>6 1</b> 11 12 | ; PAD 20 MICROSEC                                           |

| Ø10F BC04              | 40                 | MOV          | R4,#20           | 9/11CK                                                      |

| 6111 till              | 41<br>4∠           | CJN2         | R4,\$            | ; LOOP UNTIL DONE                                           |

| 0113 EB0B              | 42                 | 15162        | к3,100           |                                                             |

| 0111 2000              | 4.5                | 101112       | 1.3,200          | ; REPEAT TEST FOREVER                                       |

| ы))5-24øы              | 45                 | JNE          | STARI            | ,                                                           |

|                        | 46                 |              |                  | ; END OF FROGRAM                                            |

|                        | 47                 | 6ND          |                  |                                                             |

#### Figure 7b. A/D Exercise Program

# TABLE LOOKUP TECHNIQUES

In the previous section the interface between analog I/O devices and the MCS- $48^{TM}$  was discussed. In many applications involving analog I/O one quickly finds that nature is inherently nonlinear, and the mathematics involved in 'linearizing it' can tax the computational power of the microprocessor, particularly if it has other tasks to perform. Problems of this nature are good candidates for the use of tables.

As an example of how tables can be used as part of an analog output scheme, consider a system which requires an MCS-48 to output a variable frequency sinusoidal waveform. One method of performing this function would be to use the timer to generate an interrupt at a fixed rate of 256 times the desired output frequency. At each interrupt the appropriate value of the sine function could be calculated from the MacLaurin series:

Sin x = x -

$$\frac{x^3}{3!}$$

+  $\frac{x^5}{5!}$  -  $\frac{x^7}{7!}$  ...  $\frac{(-1)^k x^{2k+1}}{(2K+1)!}$

Where K is chosen to be large enough to provide the required accuracy.

The above calculation, although conceptually simple, would be time consuming and would severely limit the possible output frequencies which could be obtained. As an alternative to calculating these values in real time, the values could be precalculated off line and stored in a table. Upon each interrupt the MCS-48 would merely have to retrieve the appropriate value from the table and output it to the D/A converter. the MCS-48 provides a special instruction which can be used to access data in a table. If the table is stored in the last 256 bytes of the first kilobyte of MCS-48 memory then the table lookup can be performed by loading the independent variable (time in this case) into the accumulator and executing the instruction.

## MOVP3 A, @ A

This instruction uses the initial contents of the accumulator to index into page 3 of program storage. The location pointed to is read and the contents placed in the accumulator. If (as is often the case) a table of fewer than 256 entries is required, then the table can be located in any page of program memory and the instruction:

# MOVP A, @ A

can be used to retrieve data from the table. This instruction operates in the same manner as does the previous instruction except that the current page of program storage is assumed to contain the table.

If it is possible to devote slightly more of the microprocessor's time to the table look up process, then a much smaller table can often be utilized by taking advantage of interpolation to determine values of the function between values which are actual entries in the table. As an example of this

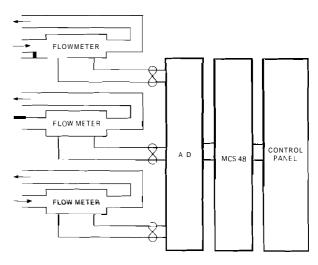

Figure 8. Flow Monitoring System

process consider the hypothetical system shown in Figure 8. The purpose of this system is to measure the flow through the three pipes, add them, and display the total flow on the control panel. The system consists of three flow meters which generate a differential voltage which is some function of flow, an A/D system with at least three differential inputs, an MCS-48, and a control panel. The schematic shown in Figure 6 could easily become part of this system, with the spare digital I/O of the MCS-48 used as an interface to the control pane). The simplicity of this system is clouded by the flow transducers, which are assumed to be not only nonlinear but also to require individual calibration (this is not an unreasonable assumption for a flow transducer). By using a table look up process and an 8748 the flow transducers can be calibrated and the results of the calibration tests stored directly in tables in the 8748. (The 8748 has a PROM in place of the ROM of the 8048 and thus makes such 'one off' programming practical.)

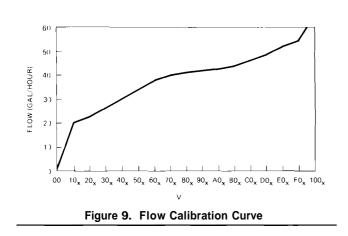

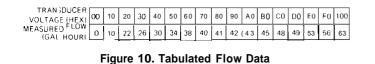

The results which might be obtained from calibrating one of the flow meters is shown in Figure 9. The results are plotted as gals/hour versus the measured voltage generated by the transducer. The voltage is shown in hexadecimal form so that it corresponds directly to the digital output of the analog to digital converter. The flow required to generate seventeen evenly spaced voltages (OH-100H in steps of 10H) has been measured and plotted. This information is shown in tabular form in Figure 10. It is necessary to generate a program which will convert any measured input from 00H to FFH into the flow in units which can be interpreted by a human operator. This can easily be done by simple interpolation.

The eight bits of independent variable (voltage) can be looked on as two four bit fields. The most significant four bits (7-4) will be used to retrieve one of the table values. The lower four bits (3-0) will be used to interpolate between this value and the value retrieved from the next higher location in the table. If the upper four bits are given the symbol I and the lower four bits the symbol N, then the interpolation can be expressed as:

$$F(x) = F(I) + \frac{N}{16} [F(I+1) - F(I)]$$

Where x is the measured voltage and F(x) is the corresponding flow.

If, as an example, the transducer voltage was measured as 48H then the flow (ref. Figure 10) would be:

$$F = 30 + \frac{8}{16} (34-30) = 32$$

A subroutine which implements this calculation is shown in Figure 11. Before it is called the independent variable (V) is placed in the accumulator and register R1 is set to point at the first value in the table. Aside from simple additions and subtractions the only arithmetic required is to multiply two values and then divide them by 16. The multiplication is handled via a subroutine which is also shown in Figure 11. The division by 16 can be performed by a four place right shift followed by a rounding operation. The routine shown will handle a monotonic increasing function of a single independent variable. Fairly simple modifications are required for nonmonotonic functions. Functions of two variables can be handled by interpolating on a plane rather than along a straight line. Although this is more time consuming, requiring an interpolation for each of the independent variables and a third to interpolate the final answer, it still provides a simple means of quickly calculating the required function. The use of tables can offer a powerful technique for function evaluation to the designer.

# RECEIVING SERIAL CODE–BASIC APPROACHES

Many microprocessor based systems require some form of serial communication. Serial communication is extensively used because it allows two or more pieces of equipment to exchange information with a minimal number of interconnecting wires. The minimization of interconnecting wires results in simpler, cheaper, interconnects because fewer (or smaller) cables and connectors are required. Since the required number of drivers and receivers required is reduced, it can become economically feasible to provide much higher noise immunity

| LUC UBJ                | SEQ             | SOURCE S   | STATEMENT        |                                         | roc c        | ഖ    | SEL            | SOURCE S'  | TATEMENT        |                                          |

|------------------------|-----------------|------------|------------------|-----------------------------------------|--------------|------|----------------|------------|-----------------|------------------------------------------|

|                        |                 | ******     | ******           | ******                                  | #11C         | 83   | 56             | REI        |                 |                                          |

|                        | 1;              |            |                  |                                         |              |      | 51<br>58       |            |                 |                                          |

|                        | 2;<br>3;        | APPROX     |                  | A PROVIDE A PARTICIPANT                 |              |      | 59             |            |                 |                                          |

|                        | 4;              | AT EA      |                  | DINTSAT TABLE<br>S INDEPENDANI VARIABLE |              |      | 611 ; MUL      | TIPLY      |                 |                                          |

|                        | 5 :             |            | A DAS            | INDEPENDINI VARIABLE                    |              |      | 61             |            |                 |                                          |

|                        | 6 : *****       | ******     | *******          | *********                               |              |      | 62             |            |                 | ; SET UP OWNT AND AEX                    |

|                        |                 |            |                  |                                         | ØllD         |      | 63 MUL1:       |            | COUNT, #        | 8                                        |

|                        | 8 ·             |            |                  |                                         | 0118         | BAØØ | 64             | MOV        | A£X,¶Ø          |                                          |

|                        | 9 : LijUAI      | £S         |                  |                                         | 121ھ         | 07   | 65<br>66 LOOPA | CT D       | С               | : CLEAR CARRY                            |

|                        | 10              |            |                  |                                         | 0121         |      | 61             | ; CLAN     | ·.              | ; IF MULIPLIER[0] <> I THEN SHIFT PRODUC |

| 0600                   | 11<br>12 RXØ    | E. 43      | 50               | : POINTER Ø                             | 0122         | 1228 | 68 LOUPB       | 180        | SSUM            | , IF NOEPETER [6] (7 I THEN DITES FROM   |

| 66661                  | 13 KAU          | ELU<br>ELU |                  | ; POINTER D<br>; POINTER 1              | p124         |      | 63             | хсь        | A, AEX          |                                          |

| 0002                   | 14 AEX          | ыũ         |                  | ; EXTENSION OF A REGISTER               | 0125         | 67   | 70             | RRC        | A               |                                          |

| 0603                   | 15 COUNT        | EUU        |                  | - COUNTER                               | Ø126         | 2A   | 71             | ХСН        | A, AEX          |                                          |

| 0004                   | 16 TEMP         | EQU        |                  | : IEMP STORAGE                          | wi 27        | 67   | 12             | F.F.C      | Α               |                                          |

|                        | 17              | -          |                  |                                         |              |      | 73             |            |                 | : LOOP DATIL DONE                        |

|                        | 18              |            |                  |                                         | 0128         |      | 74             | DJWZ       | COUNT, LA       | )OPB                                     |

|                        | 19 ; APPRO      |            |                  |                                         | w1.2A        | 83   | 75             | REI        |                 |                                          |

|                        |                 |            | -                |                                         |              |      | 76             | 200        |                 | ; ELSE ADD MULTIPLIER AND HIF' PRODUCT   |

| .10                    | 21              |            |                  |                                         | 612B<br>612C |      | 71 SSUN:<br>76 | XCH<br>ADD | A,AŁX<br>A,⊌RX0 |                                          |

| a100                   | 22              | ORG        | 100h             |                                         | 012C<br>012D |      | 78             | RKC        | A               |                                          |

| 100 5804               | 23<br>24 APROX: | 1787       | RX0,(1EM         | ; POINT RX0 AT TEMP                     | 0125<br>0125 |      | <del>เ</del> ย | ХСн        | A, A£X          |                                          |

| 0100 0004              | 24 APROA:<br>25 | KJV        |                  | IF<br>; TEMP≈N AND ØF6                  | 0125<br>0125 |      | 81             | KRC        | A               |                                          |

|                        | 26              |            |                  | ; A=P AND ØFH                           | <b>U</b> I I |      | 82             | 1416       |                 | ; LOOP UNTIL DONE                        |

| 6102 B000              | 21              | MOV        | €RXØ,∎Ø          | ,                                       | 6130         | EB21 | b 3            | [JN2       | COUNT, L        |                                          |

| wlw4 36                | 28              | XCHD       | A, URX0          |                                         | 1013Z        | 83   | 84             | RE I       |                 |                                          |

| 6165 47                | 29              | SWAP       | Α                |                                         |              |      | 85             |            |                 |                                          |

|                        | 30              |            |                  | ; RX1=BASE+A                            |              |      | 86             |            |                 |                                          |

| 0106 69                | 31              | ADL        | A,RX1            |                                         |              |      | 87             |            |                 |                                          |

| 0107 A9                | 32              | MÖV        | κxl,Α            |                                         |              |      |                |            | T PROGRAM       |                                          |

|                        | 33<br>34        |            |                  | ; RX1=TABLE(P)<br>; A=TABLE(P+1)        |              |      | 90             |            |                 |                                          |

| al08 E3                | 35              | MOVE3      | A,eA             | ; A=IABUE(P+1)                          | 0350         |      | 91             | ∪kG        | 380H            |                                          |

| 109 29                 | 36              | XCH        | A,RX1            |                                         |              |      | 92             | 5110       | 5000            |                                          |

| 10A 17                 | 37              | INC        | A                |                                         | 0380         | 68   | 93 TABLE       | : D8       | 00              | ; THIS TABLE IS FROM FIG 10              |

| 116B E3                | 38              | MOVP3      | A, eA            |                                         | 0381         | 0A   | 94             | DB         | 10              |                                          |

|                        | 39              |            |                  | ; A=TABLE(P+1)-TABLE(P)                 | 6382         |      | 95             | DB         | 22              |                                          |

| ð10C 37                | 40              | CPL        | A                |                                         | 0363         |      | 96             | DB         | 26              |                                          |

| 01WD 69                | 41              | ADU        | A,RX1            |                                         | Ø 384        |      | 97             | DB         | 38              |                                          |

| 010E 37                | 42              | CPL        | A                |                                         | Ø385<br>Ø386 |      | 98<br>99       | DB<br>DB   | 14<br>38        |                                          |

| olwF 3410              | 43<br>44        | CALL       |                  | ; A=N*A/16                              | 0387         |      | 100            | D6         | 40              |                                          |

| 010F 3410<br>0111 B502 | 44              | NOV        | MULT<br>RXØ,#AEX |                                         | 0388         |      | 1111           | DB         | 41              |                                          |

| 0111 8002              | 45              | XChD       | A, GRXD          |                                         | 0389         |      | 102            | DB         | 42              |                                          |

| 0114 47                | 47              | SWAP       | A                |                                         | 038A         |      | 103            | DB         | 43              |                                          |

| 8115 ZA                | 48              | KCh        | A,AEX            |                                         | Ø 38B        | 2D   | 104            | DB         | 45              |                                          |

| 0116 7219              | 49              | JB3        | ADJUST           |                                         | Ø38C         |      | 105            | DB         | 48              |                                          |

| J118 2A                | 50              | XCh        | A, AEX           |                                         | 0386         |      | 1U6            | CB         | 49              |                                          |

| 0119 2A                | 51 ALJUST:      |            | A,AEX            |                                         | Ø36E         |      | 187            | DB<br>DB   | 53              |                                          |

| 011A 17                | 52              | INC        | Α                |                                         | 038F         |      | 168            | DB<br>DB   | 56              |                                          |

|                        | 53              |            |                  | ; A=A+1ABLE(P)                          | 0390         | 31   | 109            | DB         | 63              |                                          |

| v118 69                | 54              | ADG        | A, RX1           | 5 (5. (c))                              |              |      | 110<br>111     | END        |                 |                                          |

|                        | 55              |            |                  | ; RETURN                                |              |      | 111            | La 1 L     |                 |                                          |

| Figure 11. Table Lookup With Interpo | olation |

|--------------------------------------|---------|

|--------------------------------------|---------|

with more sophisticated (and expensive) line terminators. The final, and usually most persuasive, argument in favor of serial cornrnunication is that it may be the only method available to accomplish the job. The obvious example of this is telecommunications where it is necessary to encode parallel information into serial format in order to communicate via the telephone network. The intent of this section is to show how the facilities of the MCS-48<sup>TM</sup> can be brought to bear on the problem of serial communication.

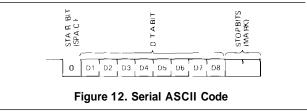

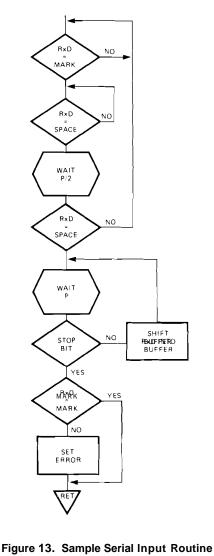

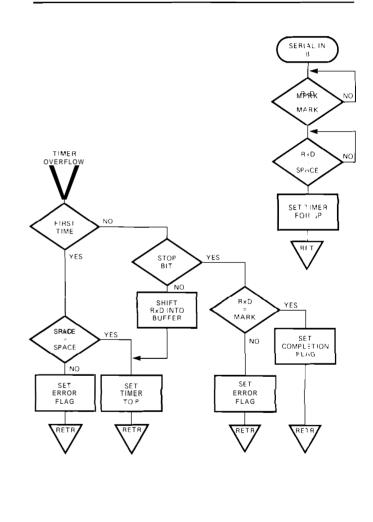

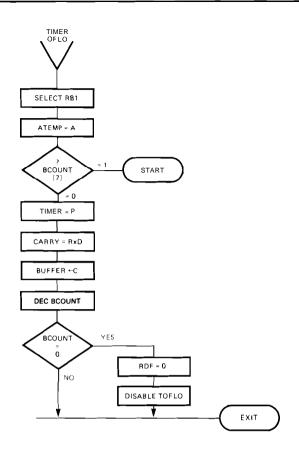

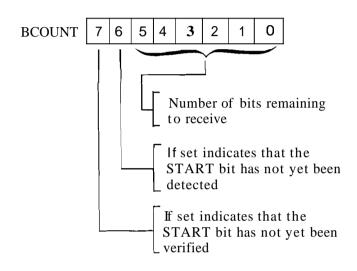

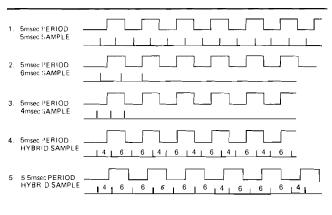

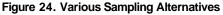

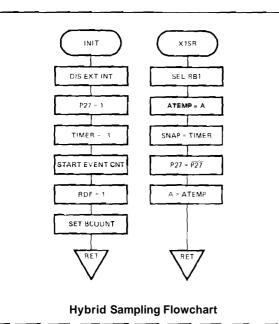

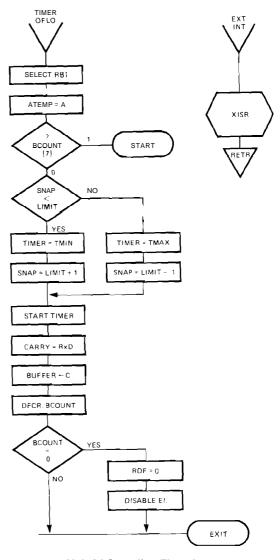

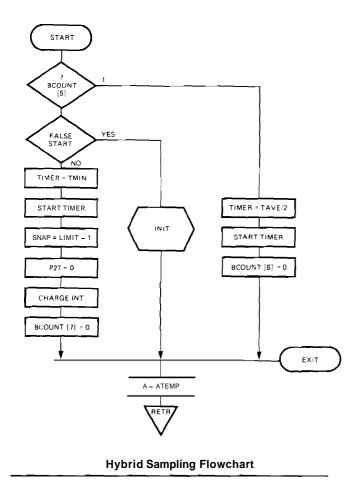

Probably the most common form of serial communication is that used by the obiquitous Teletypeserial ASCII. This format, shown in Figure 12, consists of a START bit (0 or SPACE) followed by eight data bits which are in turn followed by two STOP bits (1 or MARK). In actual practice the eighth data bit usually consists of even parity on the remaining seven data bits; for the purposes of this discussion the eighth bit will be considered only as data. A minor variation of this format deletes one of the STOP bits. An algorithm which might be used to sample serial data under software control using a microprocessor is shown in Figure 13. Th: basic intent of this algorithm is to minimize the effects of distortion and transmission rate variations on the reliability of the communication by sampling each data bit as close to its center as possible. Upon entry to this routine the software first samples the incorning data in a tight loop until it is sensed as a MARK (logical one). As soon as a MARK is detected, a second loop is entered during which the software waits until the received data goes to a SPACE (logical zero). The purpose of this construction is to detect as accurately as possible the leading edge of the START bit. This instant of time will be used as a reference point for sampling all of the following bits in the character. After sensing the leading edge of the START bit a wait of one half the expected bit time is implemented. The period of the incoming signal is called P for convenience. At the end of this wail the serial line is tested-if it is MARK then the START bit was

SERIALIN .

invalid and the process is reinitialized. If the line is still a SPACE, then the START bit is assumed to be valid and a delay of one bit time is started. At the completion of the delay the first data bit is sampled and a new delay of one bit time is initiated. This process is repeated until all eight data bits have been sampled. The last bit sampled is checked to determine if it is a valid STOP bit (a MARK). If it is, the character is assumed to be valid; if it is not, the character has a framing error and is probably invalid. A listing of a program which implements the above procedure is shown in Figure 14.

A disadvantage of the approach outlined in Figure 13 is that while the processor is inputting data serially it must totally dedicate itself to this task. Accurate timing can only be maintained if the program remains in a tight wait loop without allowing itself to be diverted to other functions. During reception of a character from a Teletype the processor will spend only a  $100\mu secs$  or so processing data and the rest of the 100 millisecs waiting to do the processing at the right time. This lack of efficiency (approximately 0.1%) in the utilization of processing power is why devices such as the 8251 USART find broad application in microprocessor systems.

| LOC     | CBJ   | SEQ                                   | SOURCE            | SIATEMEN      | г                                                                        |

|---------|-------|---------------------------------------|-------------------|---------------|--------------------------------------------------------------------------|

|         |       |                                       | * * * * * * * * * | ******        | ****                                                                     |

|         |       | Ι:                                    |                   |               |                                                                          |

|         |       | 2;                                    |                   | SERIAL        |                                                                          |

|         |       | 3 ;                                   |                   |               | UMES RXD IS                                                              |

|         |       | 4 ;                                   |                   | CTED TO       |                                                                          |

|         |       | ð : ***                               | ******            | ******        | *******                                                                  |

|         |       | 7                                     |                   |               |                                                                          |

|         |       | 8<br>9 ; EQU                          |                   |               |                                                                          |

|         |       | 10                                    |                   |               |                                                                          |

|         |       | 11                                    |                   |               |                                                                          |

| 6665    |       | 12 COUNT                              | EQU               | R2            | ; COUNTER<br>; NO OF BITS TO RECEIVE<br>; HI DLY COUNT<br>; LO DLY COUNT |

| 8600    |       | 13 BI1NO                              | ELU               | 8             | ; NO OF BITS TO RECEIVE                                                  |

| 1111112 |       | 14 DLYHI                              | EQU               | 2             | ; HI DLY COUNT                                                           |

| 00A4    |       | 15 DLYLO                              | 6 <u>.</u> 0      | ØА4н          | ; LO DLY COUNT                                                           |

| 0100    |       | 16                                    | 000               | 1400          |                                                                          |

| 0100    |       | 17<br>18                              | ORG               | төрн          | ; LOOP UNTIL RXD=MARK                                                    |

| u1aa    | 26011 | 19 SERIN                              | INTR              | s             | ; LOOP UNITE, RAD-MARK                                                   |

| 0100    | 20011 | 20                                    | . 0010            | 5             | ; NOW LOOP UNTIL RXD=SPACE                                               |

| 0102    | 3602  | 21                                    | JTØ               |               | , NOW LOOP ONTER NOD DIVICE                                              |

|         | 5002  | 22                                    |                   |               | ; WAIT 1/2 BIT TIME                                                      |

| 0104    | 341C  | 23                                    | CALL              | 58I1          | ,                                                                        |

|         |       | 24                                    |                   |               | ; IF FALSE START REINTIALIZE                                             |

| 01116   | 3600  | 25                                    | $JT\theta$        | SERIN         |                                                                          |

|         |       | 26                                    |                   |               | ; ELSE SET BIT COUNT                                                     |

| 0108    | BA69  | 27                                    | MOV               | COUNT,        |                                                                          |

|         |       | 28                                    |                   |               | ; WAIT 1 BIT TIME                                                        |

|         | 341C  | 29 LOOP:                              | CALL              | HBIT          |                                                                          |

| 010C    | 341C  | 36                                    | CALL              | HBIT          |                                                                          |

|         |       | 31                                    |                   |               | : DECREMENT COUNT                                                        |

|         |       | 32<br>33                              |                   |               | 7 - 1F ZERO EXIT WITH CARRY SET<br>7 -FRAMING ERROR                      |

| 010F    | EA15  | 34                                    | WNZ               | COUNT,        | COAD                                                                     |

| 0110    |       | 35                                    | CLR               | C             |                                                                          |

| ø111    | 3614  | 3 5<br>36                             | JTØ               | C<br>EXIT     |                                                                          |

| 0113    |       | 37                                    | CPL               | С             |                                                                          |

| 0114    | 83    | 38 EXIT:                              |                   |               |                                                                          |

|         |       | 39                                    |                   |               | ; LOAD DATA                                                              |

| 0115    |       | 40 LOAD:                              | ÇLR               | C             |                                                                          |

|         | 2619  | 39<br>40 LOAD:<br>41<br>42<br>42 LLA: | JNIØ              | LLLA          |                                                                          |

| 0118    |       | 42                                    | CPL               | С             |                                                                          |

| 0119    | 67    |                                       |                   |               |                                                                          |

| 011A    | 24ØA  | 44<br>45                              | I W               | 1008          | ; AND LOOP                                                               |

| 0101    | 2 100 | 45                                    |                   | <b>D</b> 0001 |                                                                          |

|         |       | 47 •                                  |                   |               |                                                                          |

|         |       |                                       | AY ONE HA         |               | IME                                                                      |

|         |       |                                       |                   |               |                                                                          |

|         |       | 50                                    |                   |               |                                                                          |

|         |       | 51                                    |                   |               | : SET DP LOOP                                                            |

| Ø11C    | 602   | 5.2 HBIT:                             | MOV               |               |                                                                          |

|         |       | 53                                    |                   |               | LOOP MILTIME DONE                                                        |

|         | BBA4  |                                       | MOV               | R3,#DL        | чш                                                                       |

|         | EB2Ø  | 55                                    |                   |               | ~~~                                                                      |

|         | ECLE  | 56                                    | DJN2              | R4,HLC        | UP .                                                                     |

| 0124    | 63    | 57                                    | RE1               |               | ; END OF PRUGRAM                                                         |

|         |       | 58                                    | <b>CD</b>         |               | , END OF FRAMMENT                                                        |

|         |       | 59                                    | END               |               |                                                                          |

#### Figure 14. Simple Serial Input

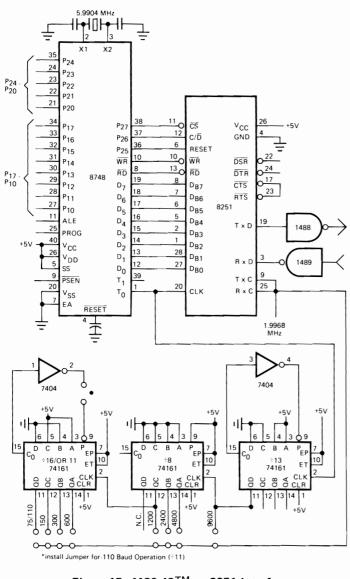

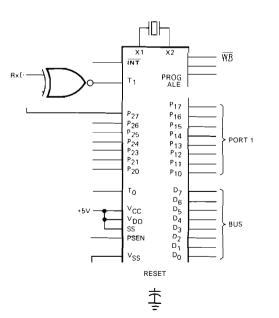

The 8251 USART is simple to interface to the MSC-48. Figure 15 shows such an interface. The USART requires a high speed clock (CLK), an initilization signal (RESET), data clocks (TxC and RxC), and data in order to operate. A circuit showing the connection of an 8748 to an 8251 USART is shown in Figure 15. In the circuit shown the high speed clock (which is used for internal sequencing by the USART) is provided by con-

Figure 15. MCS-48<sup>™</sup> to 8251 Interface

necting the CLK signal of the USART to the T0 pin of the MCS-48. The T0 pin of the MCS-48 can either be used as a directly testable input pin or it can become, under program control, an output pin which oscillates at one third of the crystal frequency. (Note that once this pin is designated by the software to be an output it will remain so until the system is reset.) In Figure 15 the crystal frequency is 5.9904 MHz so the clock provided to the 8251 is 1.9968 MHz, which conforms to its specifications.

The initialization signal to the USART (RESET) is provided programmatically by manipulation of bit 5 of port 2. It was necessary to place the reset of the 8251 under program control for two reasons. The first reason is that the MCS-48 does not supply a reset signal to other devices. The reason for this is that it was felt to be more useful to provide another pin of I/O function instead of a RESET OUT signal from the MCS-48. Although this situation could have been circumvented by the use of an externally generated reset which drove both the MCS-48 and the 8251, the second reason for program control of the reset to the USART still stands. The USART requires the presence of the CLK signal during reset in order to properly initialize itself. The ENTO CLK instruction which the MCS-48 must execute before the 8251 will receive the CLK can obviously not be executed until after the system reset has ended. Reset of the USART can be accomplished by the following code segment:

| ENT0<br>ORL | CLK<br>P2, #00100000B  | ; TURN ON CLOCK<br>; START RESET |

|-------------|------------------------|----------------------------------|

| MOV         | R2, #DELAY<br>R2, LOOP | ; DELAY USART<br>: RESET TIME    |

| <br>ANL     | P2, #11011111B         | ; END RESET                      |

This code first enables the clock, then asserts the reset signal of a time period determined by the constant DELAY. The delay invoked is (10 + 5\*DELAY) microseconds for DELAY >0. The USART requires a reset of approximately 6 CLK periods so DELAY is chosen to be 1 which ensures adequate reset timing. Note that for delays this short, NOP instructions could also be used to time the pulse.

The data clocks required by the USART are provided by the modem if the USART is operated in the synchronous mode. In the more common asynchronous mode, however, these clocks must be provided by circuitry associated with the 8251.

The 5.9904 MHz crystal was chosen because the resulting 1.9968 MHz clock to the USART can be evenly divided to provide transmit and receive clocks to the USART. Assuming the USART is in the x16 mode (i.e. it requires data clocks 16 times the baud rate) the 1.9968 MHz signal can be divided by 13 to generate the proper clock rate for 9600 baud operation. This 9600 baud clock can be further divided to give 4800, 2400, 1200, 600, and 300 baud signals. The 1200 baud signal can be divided by 11 to give a 109.1 baud signal which is within 1% of the 110 baud required by Teletypes.

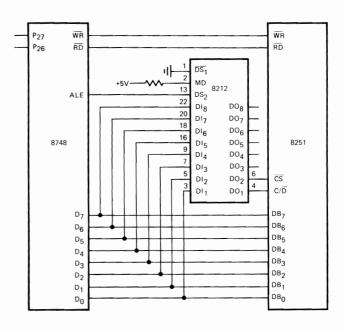

The MCS-48 communicates with the 8251 in a memory mapped mode (i.e. as if the 8251 were external RAM). The instructions available to do this are MOVX  $\partial Rj$ , A which stores the contents of the accumulator at the external RAM location addressed by Rj (j=0 or 1), and its complement, the MOVX A, @ Rj instruction which moves data from the external RAM into the accumulator. Since the MCS-48 multiplexes addresses and data on the same eight bit bus an external latch would be required in order to address the USART with

| LOC OBJ              | SDJ            | SOURCE S                      | TATEMENT                                                            |

|----------------------|----------------|-------------------------------|---------------------------------------------------------------------|