## INTELLEC® MDS IN-CIRCUIT EMULATORS

## MDS-ICE-80 8080 IN-CIRCUIT EMULATOR

Extends powerful Intellec MDS diagnostic capabilities into user configured system allowing real time (2 MHz) emulation of the user system 8080.

User configured system can share Intellec MDS RAM, ROM, and PROM memory.

I/O translation allows user configured systems to share Intellec MDS input/output facilities.

Capability to display previously executed instructions with corresponding address, data, and 8080 status information.

Capability to examine and alter CPU registers and main memory.

Direct Intellec MDS connection to user configured system via an external cable and 40-pin plug.

ICE-80 is an Intellec MDS resident module that interfaces to any user configured 8080 system and allows the designer to emulate the user 8080 in real time, single step the user system's 8080, substitute Intellec MDS memory and I/O for user system equivalents, and extend powerful debug functions into the user system.

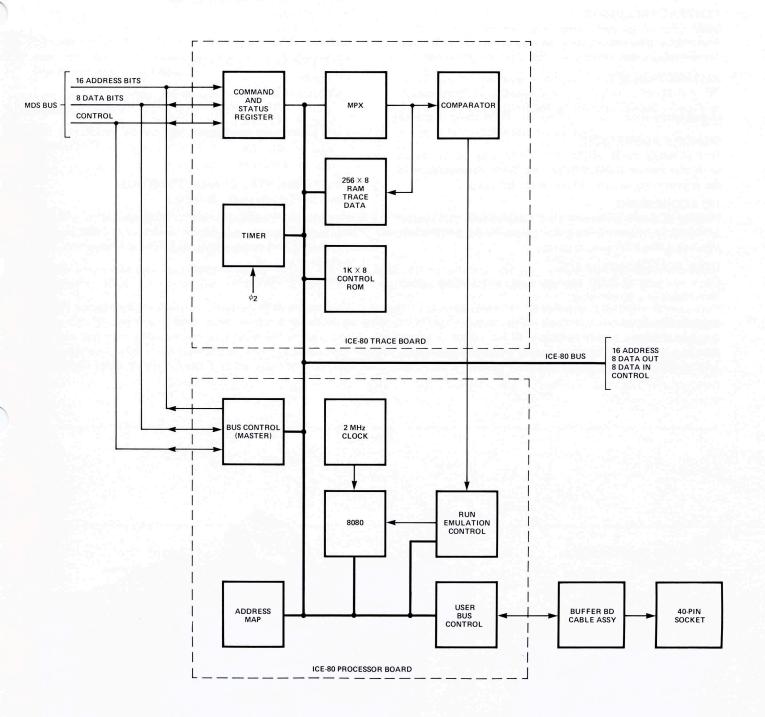

ICE-80 consists of two PC boards which reside in the Intellec MDS. The interface to the user system is an external cable terminated with a 40-pin connector. Hence, the ICE-80 cable plugs directly into the 8080 socket in the user system.

ICE-80 hardware combines with Intellec MDS resident ICE software to provide powerful hardware and software development tools. ICE-80 operates in three basic modes: Emulation, Single-Step and Interrogation. In the emulation mode, ICE-80 controls the user hardware and executes user programs in real time. In the single-step mode, ICE-80 controls the user hardware and executes user programs in a single-step or multiple single-step fashion. Status information is stored or displayed at the end of each instruction cycle. When ICE-80 is in the interrogation mode, CPU registers and memory locations can be examined or modified.

ICE-80 allows the user to assign Intellec MDS resident memory and I/O to the user system. Once assigned, the MDS memory or I/O becomes a part of the user system. The user system may operate with all MDS resident memory and I/O, all user provided memory and I/O, or a combination of both.

ICE-80 debug features include the setting of breakpoints in two hardware comparitors which can trap on any memory read, memory write, I/O read or I/O write operation. Breakpoint extensions, which can be logically ANDED with basic breakpoint parameters, include stack operation, M1 fetch state, or a user defined logic signal. When a breakpoint is encountered in the emulation mode, ICE-80 automatically reverts to the interrogation mode. At this time the memory address, data bus contents, and 8080 status byte from the last 44 machine cycles can be displayed along with the actual number of clock cycles which elapsed since program initiation. In the single-step mode, the user may select single-step or multiple single-step operation is executed, and upon completion, all relevant system status may be displayed. In multiple single-step operation is stored at the end of each machine cycle and the next instruction is executed. When multiple single-step operation is terminated upon a software breakpoint or user command, historical information may be retrieved for display or off line analysis.

The heart of ICE-80 is a microcomputer system utilizing Intel's 8080 microprocessor as its nucleus. This system communicates with the Intellec MDS host processor via I/O commands. Host processor commands and ICE-80 status are interchanged through registers on the ICE module. ICE-80 and the MDS also communicate through a control block resident in Intellec MDS main memory which contains detailed configuration and status information.

The ICE-80 microcomputer system consists of an Intel 8080 CPU, control memory and data storage memory. The system may be driven with either an internal 2 MHz clock or a user supplied clock. The basic ICE-80 system is augmented by several peripheral devices. An 8-bit command register receives Intellec MDS commands and an 8-bit status register provides ICE-80 systems status information to the Intellec MDS. Bus control logic allows the ICE-80 processor to assume control of the Intellec MDS bus as a bus master, when required. A comparitor contains two 24-bit hardware breakpoint registers which provide address and control information associated with breakpoint functions. Finally, buffer/driver circuitry, located in circuit board in the ICE-80 cable, insures that data transmission between the ICE-80 and user system meets the capacitive loading and input current requirements for the 8080.

**ICE-80 BLOCK DIAGRAM**

## **SPECIFICATIONS**

**WORD SIZE**

Instruction: 8, 16 or 24 bits

Data: 8 bits

CENTRAL PROCESSOR

8080 CPU, 2  $\mu\!S$  cycle time, 8-bit accumulator, six 8-bit registers, subroutine nesting to any level, multiple level

interrupt capability.

**INSTRUCTION SET**

78 instructions including conditional branching, binary arithmetic, logical operations, register-to-register transfers, and I/O.

MEMORY ADDRESSING

Intellec MDS RAM, ROM and PROM may be combined with user system ROM, PROM, and RAM combinations in 4K segments up to a maximum of 65, 536 bytes.

I/O ADDRESSING

Intellec MDS I/O ports may be combined with user system I/O ports in 16 port groups, up to a maximum of 256 8-bit input and 256 8-bit output ports.

**USER SYSTEM INTERFACE**

Cable carrying all 8080 address, data, and control signals terminated in a 40-pin plug.

SYSTEM CLOCK

Crystal controlled 2 MHz ±0.01%.

Removable by jumper selection when replaced by user clock.

CONNECTORS

Edge Connector: CDC VPB01E43A00A1

PHYSICAL CHARACTERISTICS

Width: 12.00 in. Height: 6.75 in. Depth: 0.50 in.

**ELECTRICAL CHARACTERISTICS**

DC Power:

$V_{CC} = +5 \pm 5\%$

$I_{CC} = 9.81A \text{ max.}; 6.90A \text{ typ.}$

$V_{DD} = +12 \pm 5\%$

$I_{DD}$  = 79 ma max.; 45 ma typ.

$V_{BB} = -9V \pm 5\%$

$I_{BB} = 1 \text{ ma max.}; 1 \mu \text{a typ.}$

**ENVIRONMENTAL CHARACTERISTICS**

Operating Temperature: 0 to 70°C

**EQUIPMENT SUPPLIED**

Printed Circuit Modules (2)

Interface Cables and Buffer Board

Reference Manual Schematic Diagram

## ORDERING INFORMATION

Part Number MDS-ICE-80

Description 8080 In-Circuit Emulator

Intel Corporation

3065 Bowers Avenue Santa Clara, California 95051

Tel: (408) 246-7501 TWX: 910-338-0026 Telex: 34-6372 WESTERN

1651 East 4th Street

Suite 228

Santa Ana, California 92701

Tel: (714) 835-9642 TWX: 910-595-1114

**MID-AMERICA**

6350 L. B. J. Freeway

Suite 178

Dallas, Texas 75240 Tel: (214) 661-8829 TWX: 910-860-5487

**GREAT LAKES REGION**

8312 North Main Street Dayton, Ohio 45415 Tel: (513) 890-5350 Telex: 288-004

**EASTERN**

187 Billerica Road

Chelmsford, Massachusetts 91824

Tel: (617) 861-1136 TWX: 710-321-0187 MID-ATLANTIC

520 Pennsylvania Avenue

Suite 102

Fort Washington, Pennsylvania 19034

Tel: (215) 542-9444 TWX: 510-661-3055

**EUROPE**

Belgium

Intel Office 216 Avenue Louise

Brussels B1050 Tel: 649-20-03 Telex: 24814

ORIENT

Japan

Intel Japan Corporation Kasahara Building 1-6-10, Uchikanda Chiyoda-Ku Tokyo 101

Tel: (03) 295-5441 Telex: 781-28426