# APPLICATION NOTE

**AP-274**

May 1986

# **Ethernet/Cheapernet LAN Design**

Kiyoshi Nishide APPLICATIONS ENGINEER Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i,  $\hat{\mathbf{1}}$ , ICE, iCEL, iCS, iDBP, iDIS, I²ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Insite, Intel, intel, intelBOS, Intelevision, inteligent Identifier, inteligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAP-NET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, PC-BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Pulse Programming Ripplemode, RMX/80, RUPI, Seamless, SLD, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, iSXM, MCS, or UPI and a numerical suffix 4-SITE.

Ethernet is a trademark of Xerox.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Literature Inquiries SC6-58 P.O. Box 58065 Santa Clara, CA 95052-8065

# ETHERNET/CHEAPERNET LAN DESIGN

| CONTENTS PAG                                          | Ε  |

|-------------------------------------------------------|----|

| PREFACE                                               | 1  |

| 1.0 INTRODUCTION                                      | 1  |

| 2.0 ETHERNET/CHEAPERNET OVERVIEW                      |    |

| 2.1 CSMA/CD                                           | 1  |

| 2.2 Ethernet/Cheapernet                               |    |

| 3.0 LANHIB HARDWARE DESCRIPTION                       | 6  |

| 3.1 82586 (Min Mode) Interface to the 80186           | 6  |

| 3.2 82586 Address Latch Interface                     | 6  |

| 3.3 80186 Address Latch Interface                     | 7  |

| 3.4 82586 Memory Interface                            | 7  |

| 3.5 80186 Memory Interface 1                          | 0  |

| 3.6 Memory Map 1                                      | 0  |

| 3.7 80186 I/O Interface 1                             | 0  |

| 3.7.1 82586 Channel Attention Generation              | 10 |

| 3.7.2 82586 Hardware Reset Port 1                     | 0  |

| 3.7.3 82530 Interface 1                               | 0  |

| 3.7.4 82501 Loopback Configuration Port               | 10 |

| 3.7.5 On-Board Individual Address Port 1              |    |

| 3.8 82586 Ready Signal Generation 1                   | 0  |

| 3.9 82501 Circuits 1                                  | 1  |

| 3.10 82502 Circuits 1                                 | 1  |

| 3.10.1 Isolation and Power Requirements               | 1  |

| 3.10.2 Other Passive and Active Devices for the 82502 | 1  |

| 3.10.3 Layout Consideration for the 82502             | 12 |

| CONTENTS                                                         | PAGE     |

|------------------------------------------------------------------|----------|

| 4.0 DEMONSTRATION SOFTWARE.                                      | 13       |

| 4.1 Programming PROMs to Run the TSMS Program                    | 13       |

| 4.2 Capabilities and Limits of the TSMS Program                  |          |

| 4.3 Example Executions of the TSMS Program                       | 15       |

| 4.3.1 Example 1: External Loopback Execution                     | 15       |

| 4.3.2 Example 2: Frame Reception in Promiscuous Mode             | 15       |

| 4.3.3 Example 3: 35.7% Network Traffi Load Generation            |          |

| 5.0 IN CASE OF DIFFICULTY                                        | 24       |

| 5.1 Troubleshooting 80186/82586<br>System                        | 24       |

| 5.2 Troubleshooting 82501/82502<br>Circuits                      | 24       |

| APPENDIX A                                                       |          |

| LANHIB Schematics and Parts List                                 | A-1      |

| APPENDIX B                                                       |          |

| Software Listings—TSMS Program and LANHIB Initialization Routine | j<br>B-1 |

| APPENDIX C                                                       |          |

| The 82530 SCC - 80186 Interface Ap                               | C-1      |

#### **PREFACE**

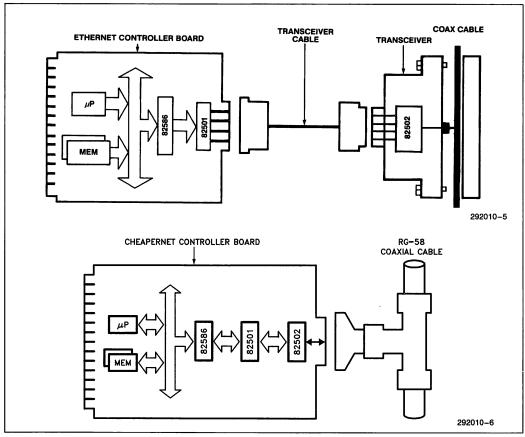

Intel's three VLSI chip set, the 82586, 82501, and 82502, is a complete solution for IEEE 802.3 10M bps LAN standards-10BASE5 (Ethernet) and 10BASE2 (Cheapernet). The 82586 is an intelligent peripheral which completely manages the processes of transmitting and receiving frames over a network under the CSMS/CD protocol. The 82586 with its on-chip four DMA channels offloads the host CPU of the tasks related to managing communication activities. The chip, for example, does not depend on the host CPU for time critical functions, such as transmissions/retransmissions and receptions of frames. The 82501 is a 10 MHz serial interface chip specially designed for the 82586. The primary function of the 82501 is to perform Manchester encoding/decoding, provide 10 MHz transmit and receive clocks to the 82586, and drive the transceiver (AUI) cable in Ethernet applications. In addition, the 82501 provides a loopback function and on-chip watchdog timer. The 82502 is a CMOS transceiver chip. The 82502 is the chip which actually drives the coaxial cable used for Ethernet or Cheapernet.

This Ap Note presents a design example of a simple but general Ethernet/Cheapernet board based on the three chip set. The board is called LANHIB (LAN High Integration Board) and uses an 80186 microprocessor as the host CPU. The LANHIB is an independent single board computer and requires only a power supply and ASCII terminal. Demo software, called TSMS (Traffic Simulator and Monitor Station) is also included in this Ap Note. The TSMS program is a network debugger and exercise tool used to exercise the 82586. In addition, flowcharts for troubleshooting are provided in order to minimize debugging time of the LANHIB board.

#### 1.0 INTRODUCTION

A brief overview of the CSMA/CD protocol is described in Section 2. Ethernet and Cheapernet are also compared in this section.

Section 3 discusses hardware of the LANHIB in detail. This section should be helpful not only to understand the LANHIB, but also to learn in general how a system based on the three chip set can be put together. Since the 82502 involves analog circuitry, an explanation on proper layout is provided.

Demo software is presented in Section 4.0. It covers EPROM programming procedures and three sample sessions. Step by step operations at a terminal are illustrated in the figures.

Section 5 describes LANHIB troubleshooting procedures. Flowcharts are used to guide troubleshooting.

Complete LANHIB schematics and parts list are found in Appendix A. If a LANHIB is to be built, the schematics and Section 5 can be submitted to an available wire wrap facility. In parallel to board construction, Sections 3 and 4 can be studied. A factory wire wrap board for the LANHIB is offered at a discount price by Augat Corporation. Please return the enclosed card for more information.

Listing of the TSMS program and LANHIB Initialization Routine are in Appendix B. The source codes and related files are available on a diskette by returning the card enclosed in this design kit or through Insite (Intel's Software Index and Technology Exchange Library).

## 2.0 ETHERNET/CHEAPERNET OVERVIEW

#### 2.1 CSMA/CD

Carrier Sense Multiple Access with Collision Detection (CSMA/CD) is a simple and efficient means of determining how a station transmits information over common medium that is shared with other stations. CSMA/CD is the access method defined by the IEEE 802.3 standard.

Carrier Sense (CS) means that any station wishing to transmit "listens" first. When the channel is busy (i.e., some other station is transmitting) the station waits (defers) until the channel is clear before transmitting ("listen before talk").

Multiple Access (MA) means that any stations wishing to transmit can do so. No central controller is needed to decide who is able to transmit and in what order.

Collision Detection (CD) means that when the channel is idle (no other station is transmitting) a station can start transmitting. It is, however, possible for two or more stations to start transmitting simultaneously causing a "collision". In the event of a collision, the transmitting stations will continue transmitting for a fixed time to ensure that all transmitting stations detect the collision. This is known as jamming. After the jam, the stations stop transmitting and wait a random period of time before retrying. The range of random wait times increases with the number of successive collisions such that collisions can be resolved even if a large number of stations are colliding.

There are three significant advantages to the CSMA/CD protocol. The first and foremost is that CSMA/CD is a proven technology. One CSMA/CD network, Ethernet, has been used by Xerox since 1975. Ethernet is so well understood and accepted that IEEE adopted

it (with minor changes) as the IEEE 802.3 10Base5 (10 Mbps, Baseband, 500 meters per segment) standard. Reliability is the second advantage to the 802.3 protocol. This media access method enables the network to operate without central control or switching. Thus, if a single station malfunctions, the rest of the network can continue operation. Finally, since CSMA/CD networks are passive and distributed in nature, they allow for easy expansion. New nodes can be added at any time without reinitializing the entire network.

#### 2.2 Ethernet and Cheapernet

The IEEE 802.3 Type 10BASE5 standard (Ethernet) has gained wide acceptance by both large and small corporations as a high speed (10 Mbps) Local Area Network. The Ethernet channel is a low noise, shielded  $50\Omega$  coaxial cable over which information is transmitted at 10 million bits per second. Each segment of cable can be up to 500 meters in length and can be connected to longer network lengths using repeaters. Repeaters regenerate the signal from one cable segment onto another. At each end of a cable segment a terminator is attached. This passive device provides the proper electrical termination to eliminate reflections. The transceiver transmits and receives signals on the coaxial cable. In addition, it isolates the node from the channel so that a failure within the node will not affect the rest of the network. The transceiver is also responsible for detecting collisions-simultaneous transmissions by two or more stations. Ethernet transceivers are connected to the network coaxial cable using a simple tap, and to the station it serves via the transceiver cable which can be

Figure 1. Different Implementations of IEEE 802.3 (Note: "10BASE5", for example, implies 10 Mbps, Baseband, and 500 meters span.)

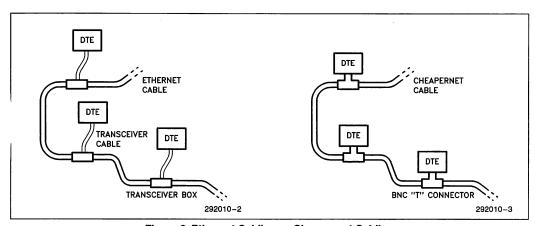

up to 50 meters in length. The transceiver cable is made of four individually shielded twisted pairs of wires. An Ethernet interface at a computer (DTE), which includes a serial interface and data link controller, provides the connection to the user or server station. It also performs frame manipulation, addressing, detecting transmission errors, network link management, and encoding and decoding of the data to and from the transceiver.

The IEEE 802.3 Type 10BASE2 (Cheapernet) has the same functional and electrical specifications as Type 10BASE5 (Ethernet) with only two exceptions in physical (or rather mechanical) characteristics. Cheapernet is as shown in Figure 1 just a different implementation of the IEEE standard. Ethernet and Cheapernet are both 10 million bits/second CSMA/CD LANs and use the identical network parameters, such as slot time = 51.2 µs. Ethernet and Cheapernet can, therefore, be built by the same VLSI components with the same software (Figure 2).

The two physical differences attribute to the cost reduction purpose of Cheapernet—cheaper implementation of Ethernet. First, the cable used in Cheapernet may be a lower cost  $50\Omega$  coaxial cable than the one for Ethernet. The most common coaxial cable for Cheapernet is RG58 which cost about \$0.15/ft. A typical Ethernet cable costs about \$0.83/ft.

Second, the transceiver is integrated into the DTE in Cheapernet. The coaxial cable physically comes to the DTE, connects to the transceiver within the DTE, and goes to the next DTE (see Figure 3). The kind of connector used at the DTE is an off-shelf BNC "T" connector. Topology is, therefore, a simple daisy chaining. This cabling scheme contributes to further cost reduction due to omission of the Transceiver (AUI) Cable, cheaper connectors, and easier installation. The Ethernet transceiver cable costs about \$1.49/ft. More flexible thin coaxial cables and familiar BNC "T" connectors are making Cheapernet a user installable Ethernet compatible network.

Figure 2. 82586/82501/82502 in Ethernet and Cheapernet

Figure 3. Ethernet Cabling vs Cheapernet Cabling

| Table 1. Differences | between Etherne | t and Cheapernet |

|----------------------|-----------------|------------------|

|----------------------|-----------------|------------------|

|                             | Ethernet<br>(10BASE5)                              | Cheapernet<br>(10BASE2)                          |

|-----------------------------|----------------------------------------------------|--------------------------------------------------|

| Data Rate                   | 10 M bits/sec.                                     | 10 M bits/sec.                                   |

| Baseband or<br>Broadband    | Baseband<br>(Manchester)                           | Baseband<br>(Manchester)                         |

| Cable Length<br>per Segment | 500m                                               | 185m                                             |

| Nodes per Segment           | 100                                                | 30                                               |

| Node Spacing                | 2.5m                                               | 0.5m                                             |

| Cable Type                  | $0.4$ in diameter $50\Omega$<br>Double Shielded    | 0.2 in diameter 50Ω<br>Single or Double Shielded |

|                             | example:<br>Ethernet Coax.                         | example:<br>RG 58 A/U or<br>RG 58 C/U            |

| Transceiver Cable           | Yes, up to 50m                                     | No, not needed                                   |

| Capacitance per node        | 4 pF                                               | . 8 pF                                           |

| Typical<br>Connector        | Clamp-on Tap Connector or<br>Type N Plug Connector | BNC Female<br>Connector                          |

Because of the lower quality cables and connectors used in Cheapernet, there are some drawbacks. The maximum distance for one Cheapernet cable segment is only 185m (600 feet), whereas 500m (1640 feet) for Ethernet. The maximum number of nodes allowed for one Cheapernet cable segment is 30. Ethernet on the other hand allows the maximum of 100 nodes per segment. A BNC "T" connector used in Cheapernet introduces more electrical discontinuity on the transmission line than the clamp-on tap connector widely used for Ethernet. The maximum capacitance load allowed at a

Cheapernet connection is 8 pF, while it is 4 pF for Ethernet. The differences are summerized in Table 1.0.

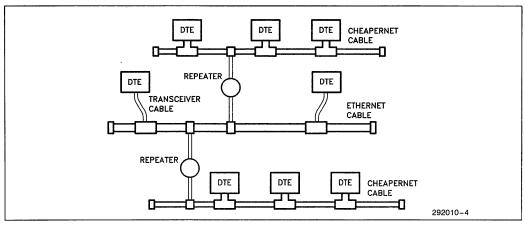

Since Ethernet and Cheapernet share the same functional and electrical characteristics, both may be mixed in a network as shown in Figure 4. In this hybrid Ethernet/Cheapernet network, it is important to keep the network propagation delay within 46.4  $\mu$ s. The network may be expanded as required within this round trip propagation delay limit. Ethernet, for example, may serve as a backbone for Cheapernet in a hybrid Ethernet/Cheapernet network.

Figure 4. Ethernet/Cheapernet Hybrid Network

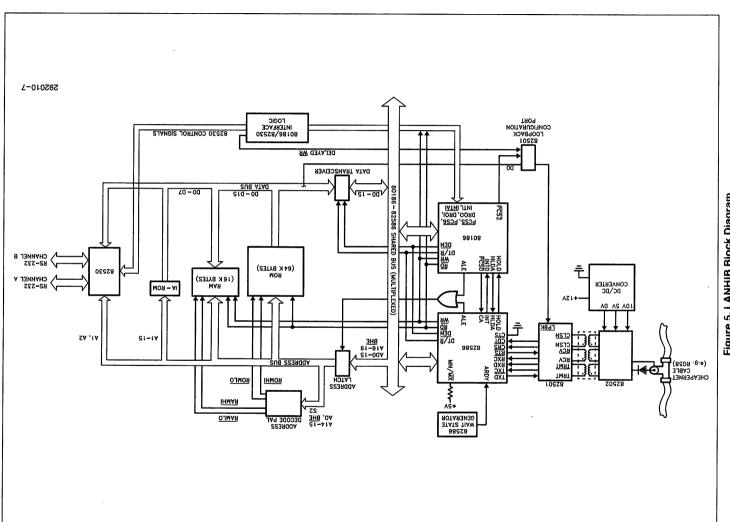

Figure 5. LANHIB Block Diagram

# 3.0 ETHERNET/CHEAPERNET NODE DESIGN

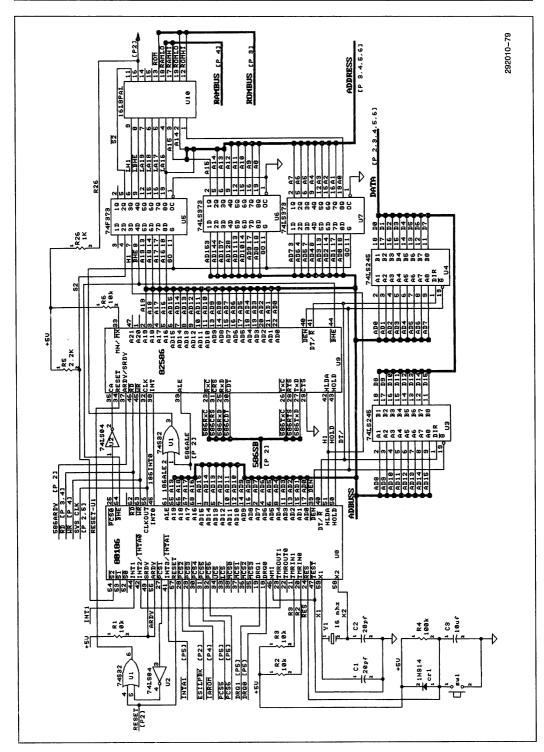

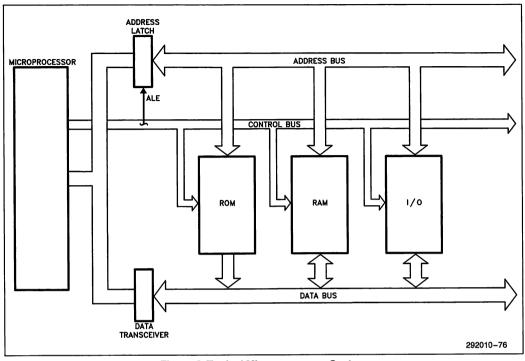

Details on LAN High Integration Board (LANHIB) design are presented in this section. The LANHIB is an 82586/80186 shared bus board and can be configured to Ethernet or Cheapernet. The 82586 is used in minimum mode to reduce chip count.

The reader is advised to refer to the 80186, 82586, 82501, and 82502 data sheets. Basic understanding of the 80186 microprocessor is assumed. Figure 5 shows the block diagram of the LANHIB. Schematics are in Appendix A.

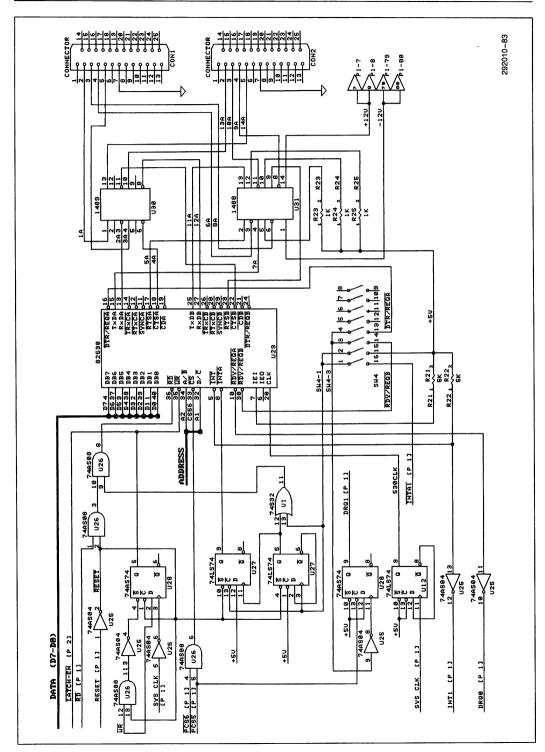

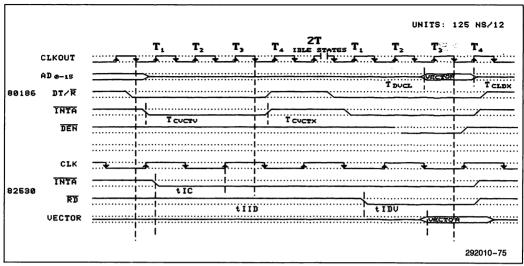

# 3.1 82586 (Min Mode) Interface to the 80186

The 82586 can be placed in minimum mode by strapping the MN/MX pin to V<sub>CC</sub>. In the minimum mode, the chip directly provides all bus control signals—ALE, RD, WR, DT/R, and DEN, saving the 8288 Bus Controller. The 80186, which is the only other bus master on the shared bus, also generates these bus control signals directly. The HOLDs and HLDAs of these two chips are connected together so that only one of the two bus masters can exclusively drive the bus at a time under the HOLD/HLDA protocol. Except for the ALE, all bus signals including address and data lines float when the chip does not have control of the bus. In this design example, RDs, WRs, DT/R and DEN from the two chips are connected together respectively. ALEs

from the two chips are connected to an OR-gate to generate a system ALE. Multiplexed address data lines AD0-AD15 and address lines A15-A19 of the two chips are also connected line by line correspondingly.

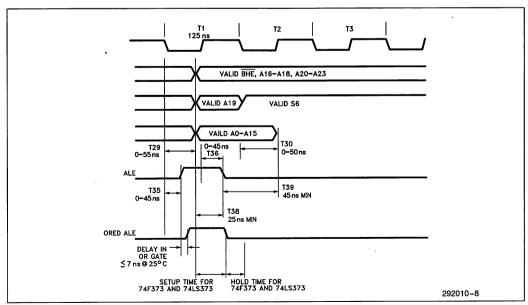

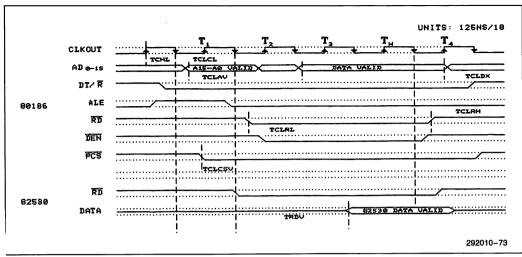

#### 3.2 82586 Address Latch Interface

Figure 6 shows the timing of the address signals with respect to the ALE signal. The ALE of the 82586 is OR-ed with the ALE of the 80186 and the result is connected to the latch enable inputs of Octal Transceiver Latches. The latches transfer the input data to the output as long as the latch enable is high, and captures the input data into the latch when the latch enable goes low. In this timing diagram, the setup and hold times of the input data (82586 address) required by the address latch can be verified. Estimating 7 ns of propagation delay in the 74S32, the setup time is T38 + 7, which is 32 ns at 8 MHz. The hold time for A19 is shorter than the other address lines because it is valid only during T1. The hold time for the A19 is T4 - T36 - 7, which is 3 ns. The hold time for the other address lines is T39 - 7, which is 38 ns. In this design, a 74F373 was chosen to latch address lines A16-A19 and two 74LS373s were used to latch address lines AD0-AD15. Required setup and hold times of the 74F and 74LS 373s are summerized in Table 2.

Note that address lines A16-A18 and  $\overline{BHE}$  of the 82586 are not really needed to be latched. These lines stay valid for an entire memory cycle.

Figure 6. 82586 Address Timing

|                 |     | 74F373 |     |     | 74LS373 |     | Unit |

|-----------------|-----|--------|-----|-----|---------|-----|------|

|                 | Min | Nom    | Max | Min | Nom     | Max |      |

| Data Setup Time | 2↓  |        |     | 5↓  |         |     | ns   |

| Data Hold Time  | 3↓  |        |     | 20↓ |         |     | ns   |

Table 2. 74F and 74LS Data Setup and Hold Time Specifications at 25°C

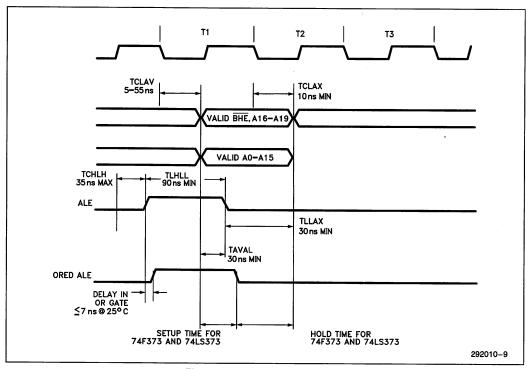

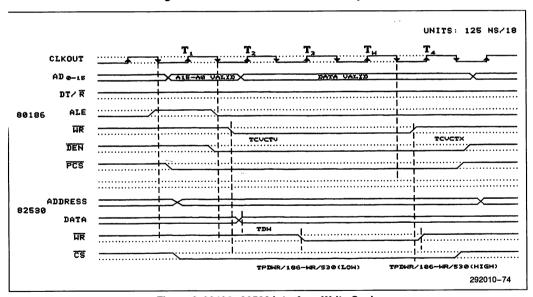

#### 3.3 80186 Address Latch Interface

The address latch used by the 82586 is shared by the 80186. Figure 7 shows the 80186 address line timing with respect to the ALE. Again estimating 7 ns delay in the 74S32, the setup time for the latch is TAVAL + 7 and the hold time is TLLAX - 7. These are 37 ns and 23 ns respectively at 8 MHz. Comparing to the required values shown in Table 2, it is quite obvious that the setup and hold times of the latch are met by wide margins. Note that the 80186's address lines A16-A18 and BHE are not valid for an entire memory cycle; therefore, they have to be latched.

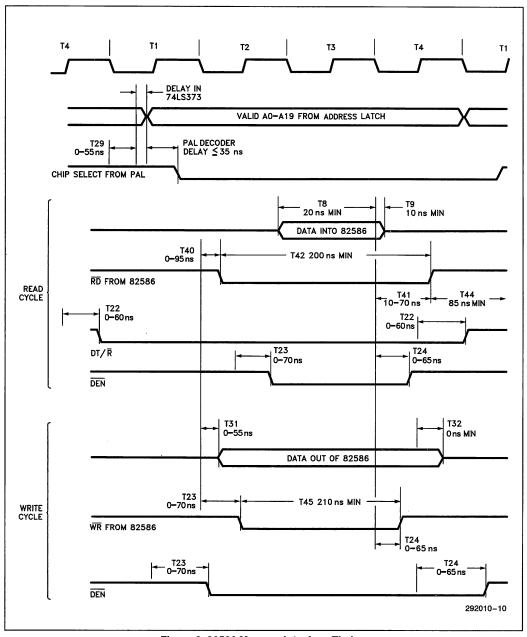

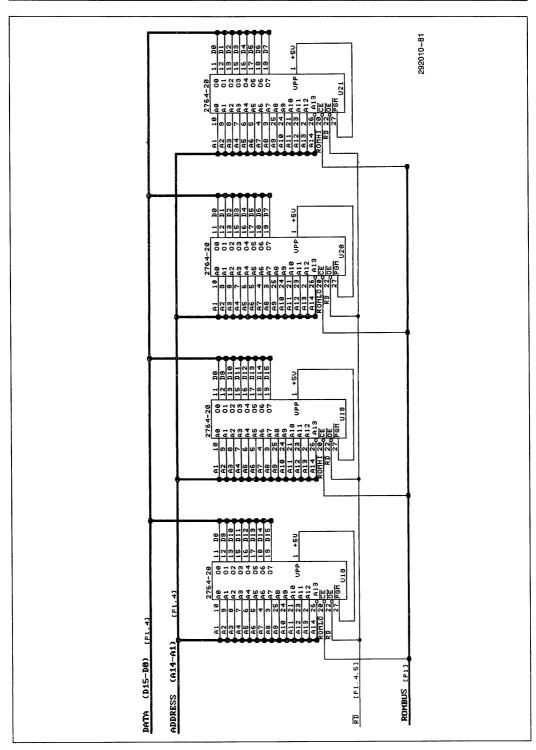

#### 3.4 82586 Memory Interface

The 74LS373 has a delay of 18 ns for input data to reach the output assuming the latch enable is high. A

demultiplexed valid address (output of the address latch), therefore, becomes available after T29 + 18 measuring from the beginning of T1 (Figure 8). The demultiplexed address remains valid until the ALE of the next memory access becomes active. Upper address lines, A14 through A20, are connected to a 16L8 PAL, which provides address decode logic for all memory devices. The PAL truth table is in Appendix A. The PAL has a maximum of 35 ns propagation delay, so chip selects will become active after 55 + 18 + 35 ns (max.) from the beginning of T1 as indicated in Figure 8. Since address decode logic is implemented by a PAL, any memory expansion would only require a reprogramming of this PAL.

Two 74LS245 bus transceiver chips are controlled by the  $DT/\overline{R}$  and  $\overline{DEN}$ . Output enable and disable times of the 74LS245 are 40 and 25 ns respectively. The maximum propagation delay when the output enable is active is 12 ns.

Figure 7. 80186 Address Timing

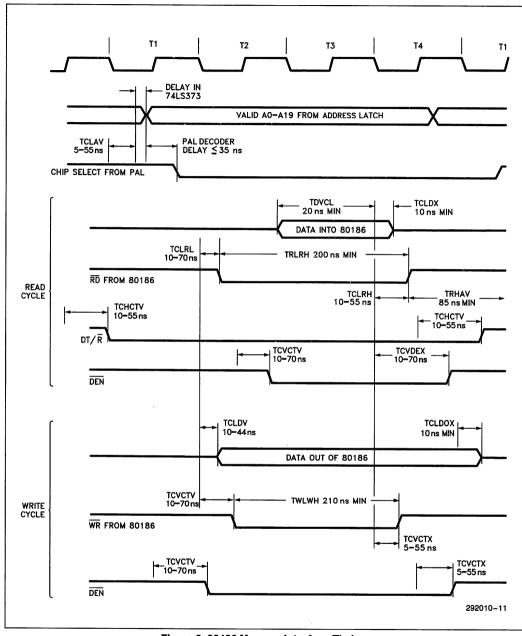

Figure 8. 82586 Memory Interface Timing

Figure 9. 80186 Memory Interface Timing

Address access time is  $3 \times T1 - T29 - 18 - T8 - 12 + n \times T1$ , where n is the number of wait states. For 0 wait states operation at 8 MHz, it is 270 ns minimum. Chip select access time is  $3 \times T1 - T29 - 18 - T8 - 12 + n \times T1 - 35$ , which is 235 ns for 0 wait state operation. Command access time for a read cycle is  $2 \times T1 - T40 - T8 - 12 + n \times T1$ , which is 123 ns. Address setup time for a write cycle is T1 - T29 - 18 + T23, which is 52 ns minimum.

To meet these timing requirements, 2764-20s must be used for ROM. Static RAM chips, HM6264P-15, offer very wide timing margins and were selected for this design.

#### 3.5 80186 Memory Interface

Figure 9 shows the timing of the 80186 memory interface. By comparing this figure to Figure 7, it is easy to notice that the 80186 offers a little faster bus interface. For example, TCLRL which is equivalent to T40 (0 to 95 ns) of the 82586 is specified as 10 to 70 ns. Since the memory choice satisfies the 82586 memory timing parameters, it also satisfies the 80186 memory timing parameters.

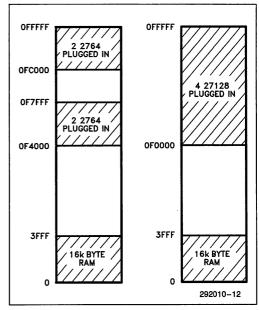

#### 3.6 Memory Map

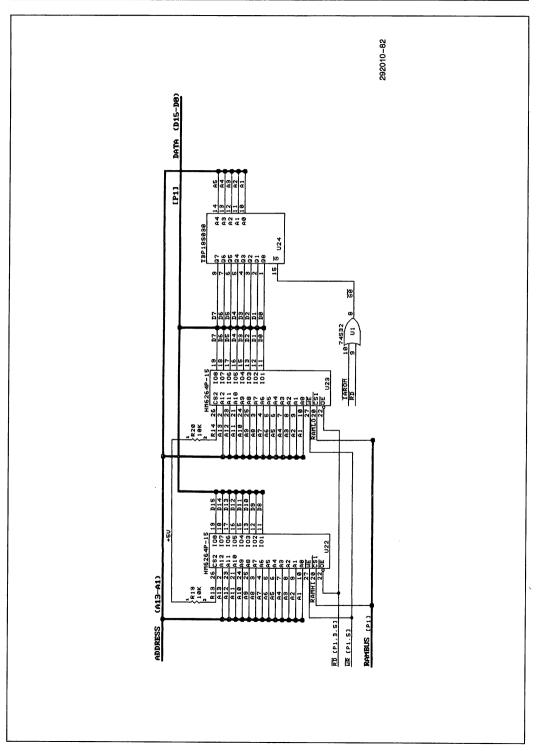

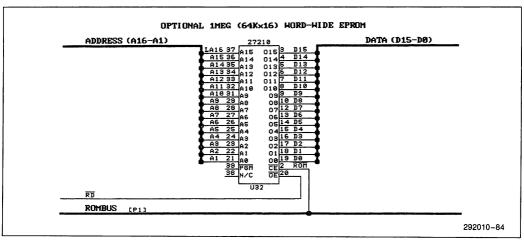

With 2764-20 EPROMs and 6264P-15 SRAMs, this board has 32 K bytes of ROM space and 16 K bytes of RAM space. Memory map is given in Figure 10. If 27128-20 EPROMs are used, the ROM space becomes 64 K bytes.

#### 3.7 80186 I/O Interface

### 3.7.1 82586 CHANNEL ATTENTION GENERATION

The active low Peripheral Chip Select 0 (PCSO) was used to generate a channel attention (CA) signal to the 82586. This way of CA generation satisfies the requirement that the width of a CA which must be wider than a clock period of the system clock.

#### 3.7.2 82586 HARDWARE RESET PORT

PCSI of the 80186 will reset the 82586 if any I/O command is executed using this I/O chip select.

#### 3.7.3 82530 INTERFACE

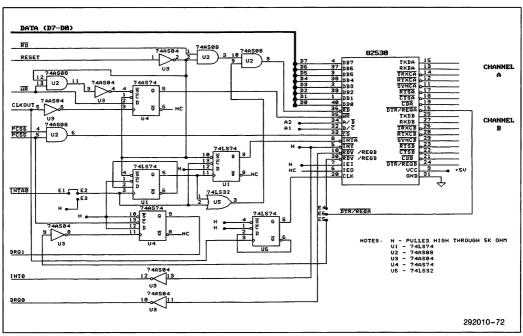

82530 interface to the 80186 was derived from the design example presented in the 82530 SCC-80186 Interface Ap Brief. This document is attached to this Ap Note as Appendix C.

Figure 10. LANHIB Memory Map

### 3.7.4 82501 LOOPBACK CONFIGURATION PORT

A 74LS74 D-type flip flop was used for this port. On power up, it configures the 82501 to Non-Loopback mode by providing a high level to pin 3 (LOOPBACK). The chip select is generated from the 80186's PCS2 and the sychronized WR command of the 82530 interface. The least significant bit of I/O output data becomes the state of the 82501's pin 3.

#### 3.7.5 ON-BOARD INDIVIDUAL ADDRESS PORT

To provide the 82586 a hardware configured host address, a 32x8 ROM is connected to the bus. The chip select for this ROM is generated from the 80186's PCS3, so that the address for the ROM is mapped into the I/O space. Six or two (IEEE 802.3 specified address lengths) consecutive I/O reads starting from the lowest address of ROM will transfer the board address stored in the ROM to an IA-Setup command block of the 82586.

#### 3.8 82586 Ready Signal Generation

82586 asynchronous ready (ARDY) signal is generated from a shift register. The shift register provides the 82586 a "normally ready" signal. When a wait state is needed, the ready signal is dropped to the low state. As shown in Table 3, the 82586 can be programmed to have 0 to 8 wait states by setting the DIP switch properly. Even though the on-board memory devices are

| Table 3. DIP | <b>Switch</b> | <b>Settings</b> | for Various |

|--------------|---------------|-----------------|-------------|

| Numbe        | rs of 82      | 586 Wait        | States      |

|   | Dip | Sw | itc | h Se | etti | ng |   | Number of Wait States |

|---|-----|----|-----|------|------|----|---|-----------------------|

| 7 | 6   | 5  | 4   | 3    | 2    | 1  | 0 | the 82586 Inserts     |

| 1 | 1   | 1  | 1   | 1    | 1    | 1  | 1 | 0                     |

| 1 | 1   | 1  | 1   | 1    | 1    | 1  | 0 | 1                     |

| 1 | 1   | 1  | 1   | 1    | 1    | 0  | 0 | 2                     |

| 1 | 1   | 1  | 1   | 1    | 0    | 0  | 0 | 3                     |

| 1 | 1   | 1  | 1   | 0    | 0    | 0  | 0 | 4                     |

| 1 | 1   | 1  | 0   | 0    | 0    | 0  | 0 | 5                     |

| 1 | 1   | 0  | 0   | 0    | 0    | 0  | 0 | 6                     |

| 1 | 0   | 0  | 0   | 0    | 0    | 0  | 0 | 7                     |

| 0 | 0   | 0  | 0   | 0    | 0    | 0  | 0 | 8                     |

1 = Switch Open

0 = Switch Closed

fast enough for 0 wait states operation, this programmable wait state capability was added so that the effect of wait states on the 82586 performance could be evaluated.

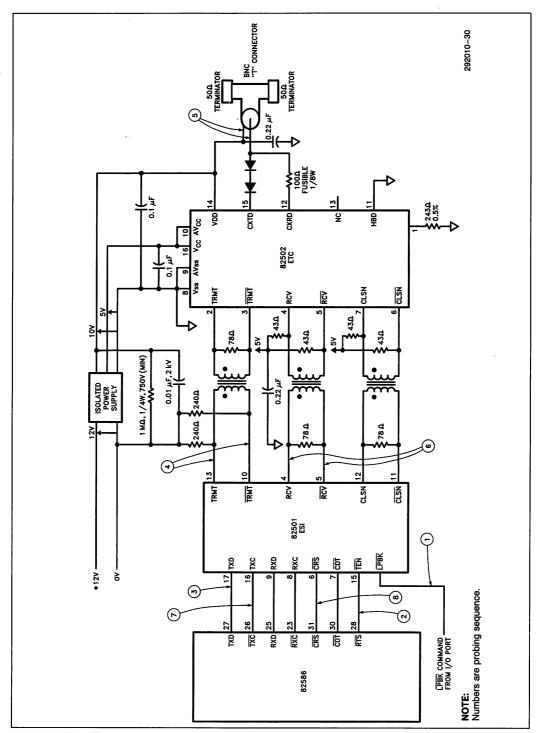

#### 3.9 82501 Circuits

Since the 82501 is designed to work with the 82586, no interfacing circuits are required.

The transceiver cable side of the 82501 requires some passive components. The receive and collision differential inputs must be terminated by  $78\Omega \pm 5\%$  resistors. Common mode voltages on these differential inputs are established internally.  $240\Omega \pm 5\%$  pull down resistors must be connected on the TRMT and TRMT output pins.

A 0.022  $\mu$ F  $\pm$  10% capacitor connected between pin 1 and 2 of the 82501 is for the analog phase-locked loop.

Connected between the X1 and X2 pins is a 20 MHz parallel resonant quartz crystal (antiresonant with 20 pF load fundamental mode). An internal divide-by-two counter generates the 10 MHz clock. Since both Ethernet and Cheapernet tolerate an error of only ±0.01% in bit rate, a high quality crystal is recommended. The accuracy of a crystal should be equal to or better than ±0.002% @ 25°C and ±0.005% for 0-70°C. A 30-35 pF capacitor is connected from each crystal pin (X1 and X2) to ground in order to adjust effective capacitance load for the crystal, which should be about 20 pF including stray capacitance.

#### 3.10 82502 Circuits

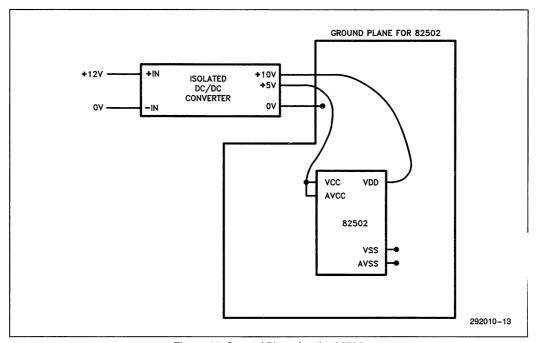

### 3.10.1 ISOLATION AND POWER REQUIREMENTS

The IEEE 802.3 standard requires an electrical isolation within the transceiver (MAU). Cheapernet

(10BASE2) requires the isolation means to withstand 500V ac, rms for one minute. Ethernet (10BASE5) requires 250 Vrms. This electrical isolation is normally accomplished by transformer coupling of each signal pair. The kind of transformers recommended for the 82502 are the pulse transformers which have a 1:1 turn ratio and at least 50 microhenry inductance. PE64102 and PE64107 manufactured by Pulse Engineering are found to be good selections for this purpose. The PE 64102 offers 500 Vrms isolation. The PE64107 offers 2000 Vrms isolation. Both products provide three transformers in one package. Even though the current Type 10BASE5 specification requires only 250 Vrms, it is very common to have a higher isolation, at least 500 Vrms, in transceivers.

The standard specifies the voltage input level and maximum current allowed on the power pair of the transceiver cable. The voltage level may be between +11.28V dc and +15.75V dc. The maximum current is limited to 500 mA. Since the 82502 requires +10V  $\pm 10\%$  and  $\pm 5V$   $\pm 10\%$  as power, there has to be a DC/DC converter. In addition the DC/DC converter must be isolated due to the requirement described above. The DC/DC converter should be able to supply about 100 mA on the + 10V line and 60 mA on the 5V line. The efficiency required in the converter is, therefore,  $((11V \times 100 \text{ mA} + 5.5V \times 60 \text{ mA}) / ((11.28V))$  $-0.5A \times 4\Omega$ ) × 500 mA)) × 100 = 31% worst case.  $4\Omega$  is the maximum round trip resistance the power pair may have. 82502's CMOS process is the major contributor to this low DC/DC efficiency requirement.

Since the DC/DC converter has an isolation transformer inside, the output voltages are all floating voltages. The 0V output of the converter, for example, has no voltage relationship with the DTE's ground. The  $V_{SS}$  and  $AV_{SS}$  pins of the 82502 should be connected to the 0V output of the DC/DC converter which is the 82502's ground (reference voltage).

Both Pulse Engineering and Reliability Incorporated produce DC/DC converters that meet the 82502's requirements. The Pulse Engineering's part number is PE64369 (enclosed in this design kit). The device measures about 1.5" x 1.5" x 0.5" and provides 2000 Vrms breakdown. The Reliability's part number is 2E12R10-5. Preliminary data sheets are available from Reliability.

### 3.10.2 OTHER PASSIVE AND ACTIVE DEVICES FOR THE 82502

A  $78\Omega$   $\pm 5\%$  resistor is required to terminate the transmit pair of the Transceiver cable. The chip has an internal circuit that establishes a common mode voltage, thus no voltage divider is required. The receive and collision pair drivers need pull up resistors. A 43.2  $\pm 1\%$  resistor must be connected from each output pin to +5V.

A 243 $\Omega$   $\pm 0.5\%$  precision resistor is required on the REXT pin to the ground. The accuracy of this resistor is very important since this resistor is a part of current and voltage reference circuits in the analog sections of the 82502.

Grounding the HBD (Heartbeat Disable) pin will allow the chip to perform Signal Quality Error check (Heartbeat) as required by the IEEE 802.3. The chip will transmit the collision presence signal after each transmission during Interframe Spacing (IFS) time. In a repeater application, this feature is disabled (HBD = +5V).

Diodes connected on the CXTD pin are to reduce the capacitive loading onto the coaxial cable. One diode is sufficient, but two will provide a protection in case one burns out (Short Circuit). The diode should have about 2 pF shunt capacitance at Vd = 0V and be able to handle at least 100 mA when biased in forward direction. A few candidates are 1N5282, 1N3600, and 1N4150.

A  $100\Omega$  fusible resistor connected on the CXRD pin is purely for protection. It is there as a fuse, not as a resistor. The 82502 works without this resistor. The IEEE 802.3, however, states that "component failures within the MAU (Media Attachment Unit or Transceiver) electronics should not prevent communication

among other MAUs on the coaxial cable." It is recommending a transceiver design that minimizes the probability of total network failure. The fusible resistor will provide an open circuit in an event of excess current. A short circuit from the CXRD pin to ground will not bring down the network due to the blown fuse.

An 8  $M\Omega$  resistor connected between the coaxial cable shield and the Transceiver cable shield will provide a static discharge path. The Ethernet coaxial cable should also have an effective earth ground at one point in a network as required by the standard. A 0.01  $\mu F$  in parallel to the 8  $M\Omega$  resistor provides ground for RF signals.

### 3.10.3 LAYOUT CONSIDERATION FOR THE 82502 CIRCUITS

It is strongly recommended that the board have a special ground plane for the 82502 (see Figure 11). The 0V (reference) output of the isolated DC/DC converter should be connected to the ground plane. The V<sub>SS</sub> and AV<sub>SS</sub> pins of the 82502 should be connected to the ground plane with minimum lead wires.

There should be a 0.22  $\mu$ F capacitor connected between the coaxial cable shield and ground. The signal path from the coax. shield through the 0.22  $\mu$ F capacitor to

Figure 11. Ground Plane for the 82502

the ground should be kept as short as possible—leads of the 0.22  $\mu$ F capacitor should be as short as possible.

The path length from the CXTD pin through two diodes to the center conductor of the coax should also be minimized.

These are recommendations which will produce a more reliable circuit if followed carefully. Remember that the 82502 has analog circuits in it.

#### 4.0 DEMONSTRATION SOFTWARE

The demonstration software included in this Ap Note is called "Traffic Simulator and Monitor Station" (TSMS) program. The TSMS program is written in PL/M and has the following features:

- 1. Programmable network load generation

- 2. Network statistical monitoring capabilities

- Interactive command execution of all 82586 commands

- 4. Interactive buffer monitoring

The environment created with the TSMS program was found to be very useful for network debugging and other individual station's hardware and software debugging. The TSMS software listing is found in Appendix B.

The 82586 Data Link Driver presented in Application Note 235 (Chapter 4 of the LAN Components User's Manual) currently runs only on the iSBC 186/51. The software will be modified to run on the LANHIB and made available as another demonstration software.

# 4.1 Programming PROMs to Run the TSMS Program

By returning the card enclosed in this kit or by contacting Insite, the TSMS program and related submit files can be obtained on a diskette. Files that are on the diskette are:

TSMS.PLM

IO.PLM

IN1186.PLM

LANHIB.CSD

SBC.CSD

IUPHIB.CSD

IUPSBC.CSD

HI.BYT

LO.BYT

ROM.CSD

HI.BYT and LO.BYT are the files which can be downloaded to PROMs directly. These files are already configured for the LANHIB. The submit file ROM.CSD invokes the Intel PROM Programming Software (iPPS) under the ISIS-II operation system and programs two 2764 EPROMs. The Intel Universal Programmer must be placed in ON-LINE mode.

Other files contained in the diskette are for compiling and locating the original TSMS program. Using these files, the original TSMS program can be changed or can be compiled for an iSBC 186/51. "TSMS.PLM" is the original TSMS source program. 'IO.PLM' contains the IO driver needed when the TSMS program is run on the iSBC 186/51. INI186.PLM is the LANHIB initialization routine. LANHIB.CSD is the submit file that compiles, links, and locates the TSMS program and the LANHIB initialization routine. SBC.CSD compiles, links, and locates the TSMS program and the IO driver for the iSBC 186/51. IUPHIB.CSD programs two 2764s for the LANHIB. IUPSBC.CSD programs two 2764s for the iSBC 186/51.

Therefore, if the TSMS program is to be run on the LANHIB (Demo board), steps required are:

- 1. submit LANHIB

- 2. submit IUPHIB

If the TSMS program is to be run on the iSBC 186/51, steps required are:

- 1. submit SBC

- 2. submit IUPSBC

# 4.2 Capabilities and Limits of the TSMS Program

The TSMS program initializes the LANHIB Ethernet/Cheapernet station by executing 82586's Diagnose, Configure, IA-Setup, and MC-Setup commands. The program asks a series of questions in order to set up a linked list of these 82586 commands. After initialization is completed, the program automatically starts the 82586's Receive Unit (monitoring capability). Transmissions are optional (traffic simulation capability).

The TSMS program has two modes of operation: Continuous mode and Interactive Command Execution mode. The program automatically gets into the Continuous mode after initialization. The Interactive Command Execution mode can be entered from the Continuous mode. Once entered in the Continuous mode, the software uses the format shown in Figure 12 to display information. Detailed description of each of these fields is as follows:

Host Address: host (station) address used in the most recently prepared IA-Setup command. The software simply writes the address stored in the IA-Setup command block with its least significant bit being in the most right position. Note that if the IA-Setup com-

#### Host Address: 00 AA 00 00 18 Multicast Address(es): No Multicast Addresses Defined Destination Address: FF FF FF FF FF FF Frame Length: 118 bytes Time Interval between Transmit Frames: 159.4 microseconds Network Percent Load generated by this station: 35.7 % Transmit Frame Terminal Count: Not Defined 82586 Configuration Block: 08 00 60 00 F2 00 \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* Station Activities \*\*\*\*\*\*\* # of Good # of Good CRC Alignment No Receive Frames Errors Errors Resource Overrun Frames Transmitted Received Errors Errors 10130 292010-14

Figure 12. Continuous Mode Display

mand was just set up and not executed, the address displayed in this field may not be the address stored in the 82586.

Multicast Address(es): multicast addresses used in the most recently prepared MC-Setup command. As in the case of host address, the software simply writes the addresses stored in the MC-Setup command block. Note that if the MC-Setup command was just set up and not executed, the addresses displayed in this field may not be the addresses stored in the 82586.

Destination Address: destination address stored in the transmit command block if AL-LOC=0. If AL-LOC=1, destination address is picked up from the transmit buffer. The least significant bit is in the most right position.

Frame Length: transmit frame byte count including destination address, source address, length, data, and CRC field.

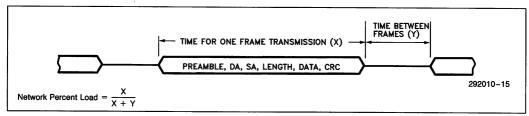

Time Interval Between Transmit Frames: approximate time interval obtainable between transmit frames (Figure 13). The number is correct if there are no other stations transmitting on the network.

Network Percent Load Generated by This Station: approximate network percent load that is generated by this station (Figure 13). The number is correct if there are no other stations transmitting on the network.

Transmit Frame Terminal Count: number of frames this station will transmit before it stops network traffic load generation. If this station is transmitting indefinitely, this field will be 'Not Defined'.

82586 Configuration Block: configuration parameters used in the most recently prepared Configure command. As in the case of IA-Setup command, the soft-

ware simply writes the parameters from the Configure command block. The least significant byte (FIFO Limit) of the configuration parameters is printed in the most left position.

- # of Good Frames Transmitted: number of good frames transmitted. This is a snap shot of the 32-bit transmit frame counter. It is incremented only when both C and OK bits of the transmit command status are set after an execution. The counter is 32-bit wide.

- # of Good Frames Received: number of good frames received. This is a snap shot of the 32-bit receive frame counter. It is incremented only when both C and OK bits of a receive frame descriptor status are set after a reception. The counter is 32-bit wide.

CRC Errors: number of frames that had a CRC error. This is a snap shot of the 16-bit CRC counter maintained by the 82586 in the SCB.

Alignment Errors: number of frames that had an alignment error. This is a snap shot of the 16-bit alignment counter maintained by the 82586 in the SCB.

No Resource Errors: number of frames that had a no resource error. This is a snap shot of the 16-bit no resource counter maintained by the 82586 in the SCB.

Receive Overrun Errors: number of frames that had a receive overrun error. This is a snap shot of the 16-bit receive overrun error counter maintained by the 82586 in the SCB.

If the station is actively transmitting, # of good frames transmitted should be incrementing. If the station is actively receiving frames, # of good frames received should be incrementing. In this continuous mode, a user can see the activities of the network.

Figure 13. Network Percent Load

Hitting any key on the keyboard while the program is running in the Continuous mode will exit the mode. The program will respond with a message 'Enter Command (H for Help)  $\rightarrow$  '. In this Interactive Command Execution mode, a user can set up any one of the 82586 action commands and/or execute any one of the 82586 SCB control commands. Setting up a Dump command and executing a SCB Command Unit Start command will, for example, execute the Dump command. Display commands are also available to see the contents of the 82586's data structure blocks. A display command will enable a user to see the contents of the 82586's dump (see Section 6.3).

Typing 'E' after 'Enter command (H for help)  $\rightarrow$  ', executing a SCB Command Unit Start command with a transmit command, or executing a SCB Receive Unit Start command will exit the Interactive Command Execution mode. The program will be back in the Continuous mode. Using this Interactive Command Execution mode, one can, for example, reconfigure the station and come back to the Continuous mode. Section 6 lists actual example executions of the TSMS program.

The TSMS program should be run in an 8 MHz system. The software running at 8 MHz with a maximum of 2 wait states has been tested and verified to be able to receive back-to-back frames separated by 9.6 microseconds and still keep track of the correct number of frames received. This capability, for example, can be used to find out exactly how many frames a new station in the network had transmitted.

The software does not perform extensive loopback tests and hardware diagnostics during the initialization. A loopback operation can be performed interactively in the Interactive Command Execution mode.

The software allows a user to set up only 8 multicast addresses maximum. It is not possible with this program to set up more than 8 multicast addresses.

The command chaining feature of the 82586 is not used in the Interactive Command Execution mode. Each command setup performed by a 'S' command after 'Enter command (H for help)  $\rightarrow$  ' sets up a command with its EL bit set, I bit reset, and S bit reset. Diagnose, Configure, IA-Setup, and MC-Setup commands are chained together during the initialization routine and executed at once with only one CA.

The software sets up 5 Receive Frame Descriptors linked in a circular list. Therefore, a user can see only the last 5 frames the station has received. It also sets up 5 receive buffers, each being 1514 bytes long, linked in circle. Therefore, the 82586 never goes into the NO RESOURCES state.

# 4.3 Example Executions of the TSMS Program

This section presents three example executions of the TSMS program. When the TSMS program needs a command to be typed, it asks a question with ' $\rightarrow$ '. Anything after ' $\rightarrow$ ' is what a user needs to type in on the keyboard. To switch from the continuous mode to the interactive command execution mode, type any key on the keyboard.

### 4.3.1 EXAMPLE 1: EXTERNAL LOOPBACK EXECUTION

In this example, 500 external loopback transmissions and receptions are executed (Figure 14). In order for the software to process each loopback properly, a large delay was given between transmissions.

### 4.3.2 EXAMPLE 2: FRAME RECEPTION IN PROMISCUOUS MODE

The 82586 is configured to receive any frame that exists in the network (Figure 15). In this example, the station received 100 frames.

### 4.3.3 EXAMPLE 3: 35.7% NETWORK TRAFFIC LOAD GENERATION

The station is programmed to transmit 118 byte long frames with a time interval of 159.4 microseconds in between (Figure 16). The network load is about 35.7 percent if no other stations are transmitting in the network.

A key was hit to enter the Interactive Command Execution mode. In that mode, a Dump command was executed and the result was displayed. After the Dump execution, a transmit command was set up again and the station was put in the Continuous mode.

```

Initialization begun

Configure command is set up for default values.

Do you want to change any bytes? (Y or N) ==> Y

Enter byte number (1 - 11) = 4

Enter byte 4 (4H) ==> A6H

Any more bytes? (Y or N) ==> Y

Enter byte number (1 - 11) ==> 11

Enter byte 11 (BH) ==> 6

Any more bytes? (Y or N) ==> N

Configure the 586 with the prewired board address ==> N

Enter this station's address in Hex ==> 000000002200

You can enter up to 8 Multicast Addresses.

Would you like to enter a Multicast Address? (Y or N) ==> N

You entered 0 Multicast Address(es).

Would you like to transmit?

Enter a Y or N ==> Y

Enter a destination address in Hex ==> 000000002200

Enter TYPE ==> 0

How many bytes of transmit data?

Enter a number ==> 2

Transmit Data is continuous numbers (0, 1, 2, 3, ...)

Change any data bytes? (Y or N) ==> N

Enter a delay count ==> 10000000000

The number is too big.

It has to be less than or equal to 65535 (FFFFH).

Enter a number ==> 60000

Setup a transmit terminal count? (Y or N) ==> Y

Enter a transmit terminal count ==> 500

Destination Address: 00 00 00 00 22 00

Frame Length: 20 bytes

Time Interval between Transmit Frames: 30.18 miliseconds

Network Percent Load generated by this station:

Transmit Frame Terminal Count: 500

Good enough? (Y or N) ==> Y

Receive Unit is active.

292010-16

```

Figure 14. External Loopback Execution

```

---Transmit Command Block---

0000 at 033E

8004

FFFF

034E

2200

0000

0000

0000

Hit <CR> to countinue

transmission started!

Host Address: 00 00 00 00 22 00

Multicast Address(es): No Multicast Addresses Defined

Destination Address: 00 00 00 00 22 00

Frame Length: 20 bytes

Time Interval between Transmit Frames: 30.18 miliseconds

Network Percent Load generated by this station:

Transmit Frame Terminal Count: 500

82586 Configuration Block: 08 00 A6 00 60 00 F2 00 00 06

# of Good

# of Good

CRC

Alignment

No

Receive

Frames

Frames

Errors

Errors

Resource

Overrun

Transmitted Received

Errors

Errors

500

500

0

0

292010-17

```

Figure 14. External Loopback Execution (Continued)

```

Initialization begun

Configure command is set up for default values.

Do you want to change any bytes? (Y or N) ==> Y

Enter byte number (1 - 11) ==> 9

Enter byte 9 (9H) ==> 1

Any more bytes? (Y or N) ==> N

Configure the 586 with the prewired board address ==> Y

You can enter up to 8 Multicast Addresses.

Would you like to enter a Multicast Address? (Y or N) ==> N

You entered 0 Multicast Address(es).

Would you like to transmit?

Enter a Y or N ==> N

Receive Unit is active.

Host Address: 00 AA 00 00 18 6D

Multicast Address(es): No Multicast Addresses Defined

82586 Configuration Block: 08 00 26 00 60 00 F2 01 00 40

************************* Station Activities ****************

# of Good

# of Good

CRC

Alignment

No

Receive

Frames

Frames

Errors

Errors

Resource

Overrun

Transmitted Received

Errors

Errors

100

Enter command (H for help) ==> D

Command Block or Receive Area? (R or C) ==> R

Frame Descriptors:

4000 at 036C A000 at 0382 A000 at 0398 A000 at 03AE A000 at 03C4

0000

0000

0000

0000

0000

0382

0398

03AE

03C4

036C

03DA

03E4

03EE

03F8

0402

2200

2200

2200

2200

2200

2200

2200

2200

2200

2200

0000

0000

0000

0000

0000

292010-18

```

Figure 15. Frame Reception in Promiscuous Mode

| · · · · · · · · · · · · · · · · · · · |                      |       |                |          |          |          |          |            |          |          |          |          |            |

|---------------------------------------|----------------------|-------|----------------|----------|----------|----------|----------|------------|----------|----------|----------|----------|------------|

| 0000                                  | 0000                 |       | 0000           |          |          | 0000     | )        |            | 0        | 000      |          |          |            |

| 0000                                  | 0000                 |       | 0000           |          |          | 0000     |          |            |          | 000      |          |          |            |

| 0000                                  | 0000                 |       | 0000           |          |          | 0000     | )        |            | 0        | 000      |          |          |            |

| 0000                                  | 0000                 |       | 0000           |          |          | 0000     | כ        |            | 0        | 000      |          |          |            |

|                                       |                      |       |                |          |          |          |          |            |          |          |          |          |            |

| Deseine Buff                          | Docom                |       |                |          |          |          |          |            |          |          |          |          |            |

| Receive Buff                          | er Descri<br>C064 at |       |                | at 0     | 255      | COS      | 4 a+     | 03F        | 3 C      | 164      | at O     | 402      |            |

| C064 at 03DA                          | 03EE                 | U3E4  | 03F8           | at 0     | 366      | 040      |          | 031        |          | 3DA      | ac o     | 102      |            |

| 03E4                                  | 03EE                 |       | OFEO           |          |          | 15C      | -        |            |          | BB4      |          |          |            |

| 040C<br>0000                          | 0000                 |       | 0000           |          |          | 000      |          |            |          | 000      |          |          |            |

| 05DC                                  | 05DC                 |       | 05DC           |          |          | 05D      |          |            |          | 5DC      |          |          |            |

| USDC                                  | USDC                 |       | UJDC           |          |          |          | _        |            |          |          |          |          |            |

| Display the<br>Receive Buff           |                      | buffe | rs? (Y         | or N     | ) ==:    | > Y      |          |            |          |          |          |          |            |

| Receive Buff                          | er 0 :               |       |                |          |          |          |          |            |          |          |          |          |            |

| 002C:014C 00                          | 01 02                | 03    | 04 05          | 06       | 07       | 08       | 09       | 0A         | 0B       | 0C       | 0D       | 0E       | OF         |

| 002C:014C 00                          | 11 12                |       | 14 15          | 16       | 17       | 18       | 19       | 1A         | 1B       | ic       | 1D       | 1E       | 1F         |

| 002C:015C 10                          | 21 22                |       | 24 25          | 26       | 27       | 28       | 29       | 2A         | 2B       | 2C       | 2D       | 2E       | 2F         |

| 002C:017C 30                          | 31 32                |       | 34 35          | 36       | 37       | 38       | 39       | 3A         | 3B       | 3C       | 3D       | 3E       | 3F -       |

| 002C:018C 40                          | 41 42                | 43    | 44 45          | 46       | 47       | 48       | 49       | 4A         | 4B       | 4C       | 4D       | 4E       | 4 F        |

| 002C:019C 50                          | 51 52                | 53    | 54 55          | 56       | 57       | 58       | 59       | 5A         | 5B       | 5C       | 5D       | 5E       | 5F         |

| 002C:01AC 60                          | 61 62                | 63    |                |          |          |          |          |            |          |          |          |          |            |

|                                       |                      |       |                |          |          |          |          |            |          |          |          |          |            |

| Hit <cr> to c</cr>                    | countinue            |       |                |          |          |          |          |            |          |          |          |          |            |

|                                       |                      |       |                |          |          |          |          |            |          |          |          |          |            |

| Receive Buff                          |                      |       | <u></u>        |          |          |          |          |            |          |          |          |          |            |

| 002C:0736 00                          | 01 02                |       | 04 05          | 06       | 07       | 08       | 09       | 0A         | OB       | OC.      | 0D       | 0E       | OF         |

| 002C:0746 10                          | 11 12                |       | 14 15          | 16<br>26 | 17<br>27 | 18<br>28 | 19<br>29 | 1A<br>2A   | 1B<br>2B | 1C<br>2C | 1D<br>2D | 1E<br>2E | 1F<br>2F   |

| 002C:0756 20                          | 21 22<br>31 32       |       | 24 25<br>34 35 | 36       | 37       | 38       | 39       | 3A         | 3B       | 3C       | 3D       | 3E       | 2F<br>3F   |

| 002C:0766 30<br>002C:0776 40          | 41 42                |       | 44 45          | 46       | 47       | 48       | 49       | 4A         | 4B       | 4C       | 4D       | 4E       | 4F         |

| 002C:0786 50                          | 51 52                |       | 54 55          | 56       | 57       | 58       | 59       | 5A         | 5B       | 5C       | 5D       | 5E       | 5F         |

| 002C:0796 60                          | 61 62                | 63    |                |          | ٠.       | ••       |          |            |          | -        | -        |          |            |

| 0020.0730 00                          | 01 02                | 03    |                |          |          |          |          |            |          |          |          |          |            |

| Hit <cr> to c</cr>                    | ountinue             |       |                |          |          |          |          |            |          |          |          |          |            |

|                                       |                      |       |                |          |          |          |          |            |          |          |          |          |            |

| Receive Buff                          | er 2 :               |       |                |          |          |          |          |            |          |          |          |          |            |

| 002C:0D20 00                          | 01 02                | 03    | 04 05          | 06       | 07       | 80       | 09       | OA         | ов       | 0C       | OD       | 0E       | OF         |

| 002C:0D30 10                          | 11 12                |       | 14 15          |          | 17       | 18       | 19       | 1 <b>A</b> | 1B       | 1C       | 1D       | 1E       | 1F         |

| 002C:0D40 20                          | 21 22                |       | 24 25          |          | 27       | 28       | 29       | 2A         | 2B       | 2C       | 2D       | 2E       | 2F         |

| 002C:0D50 30                          | 31 32                |       | 34 35          |          | 37       | 38       | 39       | 3A         | 3B       | 3C       | 3D       | 3E       | 3F         |

| 002C:0D60 40                          | 41 42                |       | 44 45          |          | 47       | 48       | 49       | 4A         | 4B       | 4C       | 4D       | 4E       | 4F         |

| 002C:0D70 50                          | 51 52                |       | 54 55          | 56       | 57       | 58       | 59       | 5A         | 5B       | 5C       | 5D       | 5E       | 5F         |

| 002C:0D80 60                          | 61 62                | 63    |                |          |          |          |          |            |          |          |          |          |            |

| Hit <cr> to c</cr>                    | ountinue             |       |                |          |          |          |          |            |          |          |          |          |            |

| Receive Buff                          | er 3 :               |       |                |          |          |          |          |            |          |          |          |          |            |

| 002C:130A 00                          | 01 02                | 03    | 04 05          | 06       | 07       | 08       | 09       | OA         | 0B       | oc       | OD       | 0E       | OF         |

| 002C:130A 00                          | 11 12                |       | 14 15          |          | 17       | 18       | 19       | 1A         | 1B       | 10       | 10       | 1E       | 1F         |

| 002C:131A 10                          | 21 22                |       | 24 25          |          | 27       | 28       | 29       | 2A         | 2B       | 2C       | 2D       | 2E       | 2F         |

| 002C:133A 30                          | 31 32                |       | 34 35          |          | 37       | 38       | 39       | 3A         | 3B       | 3C       | 3 D      | 3 E      | 3F         |

| 002C:134A 40                          | 41 42                | 43    | 44 45          | 46       | 47       | 48       | 49       | 4A         | 4B       | 4C       | 4D       | 4E       | 4F         |

| 002C:135A 50                          | 51 52                | 53    | 54 55          | 56       | 57       | 58       | 59       | 5A         | 5B       | 5C       | 5D       | 5E       | 5 <b>F</b> |

| 002C:136A 60                          | 61 62                | 63    |                |          |          |          |          |            |          |          |          |          |            |

|                                       |                      |       |                |          |          |          |          |            |          |          |          |          |            |

| Hit <cr> to c</cr>                    | countinue            |       |                |          |          |          |          |            |          |          |          |          |            |

|                                       |                      |       |                |          |          |          |          |            |          |          |          |          | 292010-19  |

|                                       |                      |       |                |          |          |          |          |            |          |          |          |          |            |

Figure 15. Frame Reception in Promiscuous Mode (Continued)

```

Receive Buffer 4:

002C:18F4 00 01

02

03

04

05

06

07

80

09

0A

0B

0C

0D

0E

OF

002C:1904 10

11

12

13

14

15

16

17

18

19

1A

18

10

1D

1E

1F

002C:1914 20

21

22

23

24

25

26

27

28

29

2A

2B

2C

2D

2E

2F

002C:1924 30

31

32

33

34

35

36

37

38

39

3A

3B

3C

3D

3E

3F

002C:1934 40

42

43

46

4C

41

44

45

47

48

49

4A

4B

4D

4E

4 F

002C:1944 50

51

52

53

54

55

56

57

58

59

5A

5B

5C

5D

5F

002C:1954 60

61

62

63

Hit <CR> to countinue

Enter command (H for help) ==> E

************************ Station Cofiguration *******************

Host Address: 00 AA 00 00 18 6D

Multicast Address(es): No Multicast Addresses Defined

82586 Configuration Block: 08 00 26 00 60 00 F2 01 00 40

************************* Station Activities *******************

# of Good

# of Good

CRC

Alignment

No

Receive

Frames

Frames

Errors

Errors

Resource

Overrun

Transmitted

Received

Errors

Errors

100

0

0

O

292010-20

```

Figure 15. Frame Reception in Promiscuous Mode (Continued)

```

Initialization begun

Configure command is set up for default values.

Do you want to change any bytes? (Y or N) ==> N

Configure the 586 with the prewired board address ==> Y

You can enter up to 8 Multicast Addresses.

Would you like to enter a Multicast Address? (Y or N) ==> N

You entered 0 Multicast Address(es).

Would you like to transmit?

Enter a Y or N ==> Y

Enter TYPE ==> 0

How many bytes of transmit data?

Enter a number ==> 100

Transmit Data is continuous numbers (0, 1, 2, 3, ...)

Change any data bytes? (Y or N) ==> \hat{N}

Enter a delay count ==> 0

Setup a transmit terminal count? (Y or N) ==> N

Destination Address: FF FF FF FF FF

Frame Length: 118 bytes

Time Interval between Transmit Frames: 159.4 microseconds

Network Percent Load generated by this station: 35.7 %

Transmit Frame Terminal Count: Not Defined

Good enough? (Y or N) ==> Y

Receive Unit is active.

---Transmit Command Block---

0000 at 033E

8004

FFFF

034E

FFFF

FFFF

FFFF

0000

Hit <CR> to countinue

292010-21

```

Figure 16. 35.7% Network Load Generation

```

transmission started!

************************** Station Configuration ****************

Host Address: 00 AA 00 00 18 6D

Multicast Address(es): No Multicast Addresses Defined

Destination Address: FF FF FF FF FF

Frame Length: 118 bytes

Time Interval between Transmit Frames: 159.4 microseconds

Network Percent Load generated by this station: 35.7 %

Transmit Frame Terminal Count: Not Defined

82586 Configuration Block: 08 00 26 00

60 00 F2 00

00 40

# of Good

CRC

Alignment

No

Receive

# of Good

Errors

Errors

Resource

Overrun

Frames

Frames

Errors

Transmitted Received

Errors

0

0

10459

Enter command (H for help) ==> H

Commands are:

S - Setup CB

D - Display RFD/CB

P - Print SCB

C - SCB Control CMD

L - ESI Loopback On

N - ESI Loopback Off

A - Toggle Number Base

Z - Clear Tx Frame Counter

Y - Clear Rx Frame Counter

E - Exit to Continuous Mode

Enter command (H for help) ==> S

Enter command block type (H for help) ==> H

Command block type:

qoN - N

I - IA Setup

C - Configure

M - MA Setup

T - Transmit

R - TDR

D - Diagnose

S - Dump Status

H - Print this message

Enter command block type (H for help) ==> S

Enter command (H for help) ==> C

Do you want to enter any SCB commands? (Y or N) ==> Y

Enter CUC ==> 1

Enter RES bit ==> 0

Enter RUC ==> 0

Issued Channel Attention

Enter command (H for help) ==> D

292010-22

```

Figure 16. 35.7% Network Load Generation (Continued)

```

Command Block or Receive Area? (R or C) ==> C

--- Dump Status Command Block---

A000 at 0364

8006

FFFF

27D6

Dump Status Results

at 27D6

00 E8

3F

26

80

60

00

FA

00

00

40

FF

6D

18

00

00

AA

00

40

20

00

00

00

00

FF

FF

FF

FF

9E

B5

EΕ

CF

3F

B0

00

00

62

63

00

00

00

00

00

0.0

FF

FC

85

08

00

00

00

00

00

00

00

00

00

00

00

00

70

06

03

00

00

05

0C

DC

00

04

DC

05

E4

03

DA

03

DA

03

78

05

82

03

6C

03

F8

03

64

80

D6

27

E8

21

FF

FF

4E

03

06

80

FF

FF

64

03

00

00

D2

0.2

00

00

00

00

00

00

00

00

D6

27

00

01

00

28

00

00

00

0.0

30

26

00

00

20

00

40

06

30

01

00

00

90

00

10

01

00

00

6C

03

00

00

6A

03

0E

00

6C

28

00

00

74

0.3

00

00

00

00

00

00

00

00

00

CO

00

00

00

00

Enter command (H for help) ==> S

Enter command block type (H for help) ==> T

Enter TYPE ==> 0

How many bytes of transmit data?

Enter a number ==> 100

Transmit Data is continuous numbers (0, 1, 2, 3, ...)

Change any data bytes? (Y or N) ==> \dot{N}

Enter a delay count ==> 0

Setup a transmit terminal count? (Y or N) ==> N

Destination Address: FF FF FF FF FF

Frame Length: 118 bytes

Time Interval between Transmit Frames: 159.4 microseconds

Network Percent Load generated by this station: 35.7 %

Transmit Frame Terminal Count: Not Defined

Good enough? (Y or N) ==> Y

Enter command (H for help) ==> C

Do you want to enter any SCB commands? (Y or N) ==> Y

Enter CUC ==> 1

Enter RES bit ==> 0

Enter RUC ==> 0

Issued Channel Attention

292010-23

```

Figure 16. 35.7% Network Load Generation (Continued)

```

************************** Station Configuration *********

Host Address: 00 AA 00

00

18

Multicast Address(es): No Multicast Addresses Defined

FF

Destination Address: FF

FF FF FF

FF

Frame Length: 118 bytes

Time Interval between Transmit Frames:

159.4 microseconds

Network Percent Load generated by this station: 35.7 %

Transmit Frame Terminal Count: Not Defined

82586 Configuration Block: 08 00 26 00

60

00

F2

00

*************************** Station Activities ****************

Receive

# of Good

# of Good

CRC

Alignment

No

Resource

Overrun

Frames

Errors

Errors

Frames

Errors

Errors

Transmitted

Received

0

106020

292010-24

```

Figure 16. 35.7% Network Load Generation (Continued)

#### 5.0 IN CASE OF DIFFICULTY

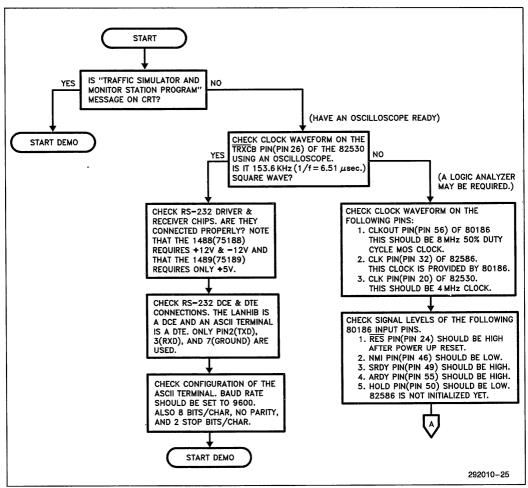

This section presents methods of troubleshooting ("debugging") a LANHIB board. When a LANHIB board is powered up with the TSMS program stored in EPROMs, it should display "TRAFFIC SIMULATOR AND MONITOR STATION PROGRAM" message on a terminal screen. If the message is not displayed, the board has to be debugged. Section 5.1 describes basic 80186/82586 system troubleshooting procedures. Section 5.2 is for troubleshooting 82501 and 82502 circuits. After the 80186/82586 system is debugged, the 82501/82502 circuits have to be tested.

#### 5.1 Troubleshooting 80186/82586 System

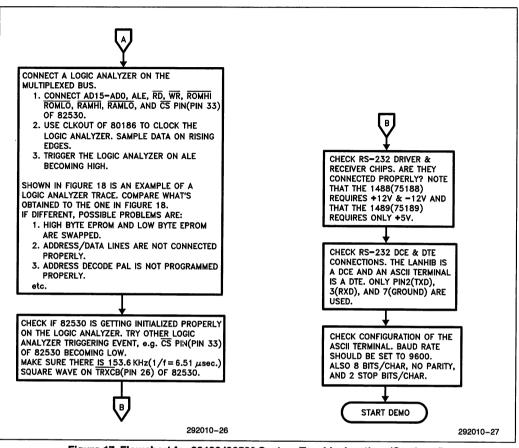

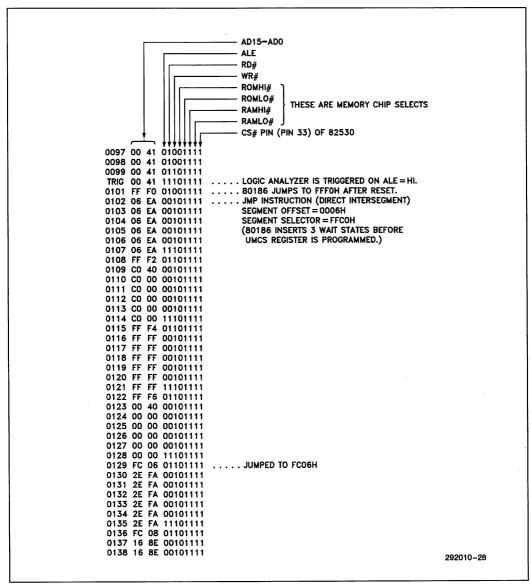

Shown in Figure 17 is a flow chart for troubleshooting 80186/82586 system. The procedure requires an oscilloscope. A logic analyzer is needed if problems appear to be serious. The procedures will debug the board to the point where the 82530 is initialized properly. If the 82530 can be initialized properly, ROM and RAM interfaces must be functioning. Board initialization routines (INI186.PLM) linked to the TSMS program requires ROM and RAM accesses. Since the 82586 shares most of the system with the 80186, no special debugging is required for the 82586. Wiring of all 82586 parallel signal pins should, however, be checked.

The flow chart branches to two major paths after the first decision box. One path debugs the RS-232 channel

and the other debugs the 80186/82586 system. The waveform of the  $\overline{TRXCB}$  output of the 82530 determines which path to be taken. If the 82530 is getting programmed properly, there should be 153.6 KHz  $(1/f = 6.51 \ \mu s)$  clock on this output pin. If there is a clock, the problem is probably in the RS-232 interface. If there is no clock, then the system has to be debugged using a logic analyzer.

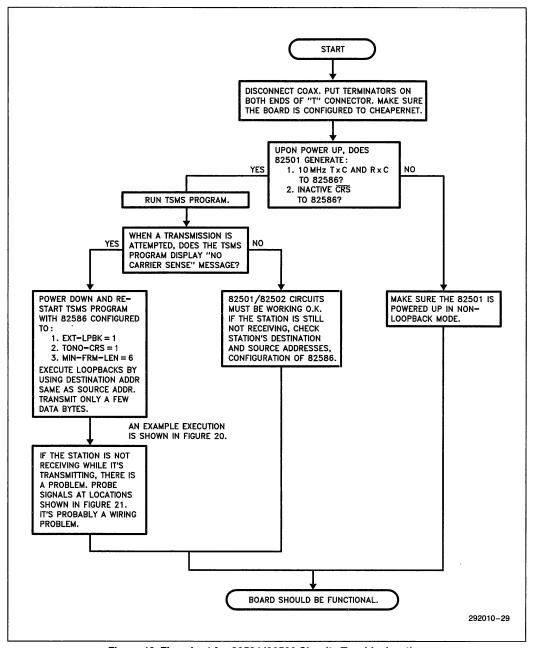

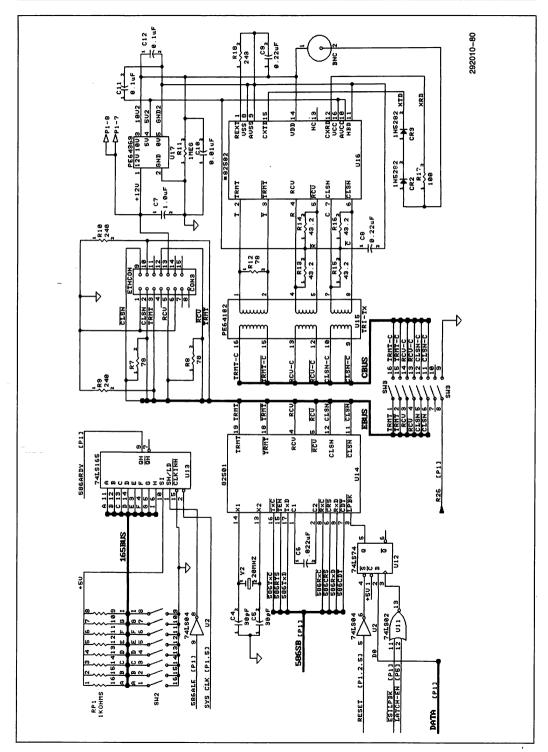

# 5.2 Troubleshooting 82501/82502 Circuits

If the TSMS program runs on the LANHIB but the 82586 is not able to transmit or receive, there must be a problem in 82501/82502 circuits. The flow chart in Figure 19 will guide troubleshooting in these circuits. An oscilloscope is required.

The board should be configured to Cheapernet and disconnected from the network. Two terminators will be required to terminate a "T" BNC connector providing an effective load resistance of  $25\Omega$  to the 82502.

The 82586 must have the system and transmit clocks running upon reset. Since the transmit clock is generated by the 82501, the 82501 transmit clock output pin (pin 16) should be checked. The TSMS program executes 82586's Diagnose, Configure, IA-Setup, and MC-Setup commands during initialization. If the 82586 has active  $\overline{CRS}$  (Carrier Sense) signal, it cannot complete execution of these commands. The 82501 should, therefore, be checked if it is generating inactive  $\overline{CRS}$  signal to the 82586 after power up. The LANHIB powers up the 82501 in non-loopback mode.

After making sure that the 82501 is generating proper signals to the 82586, the TSMS program is restarted with an initialization shown in Figure 20. The 82586 is configured to EXT-LPBK=1, TONO-CRS=1, and MIN-FRM-LEN=6. The chip is also loaded with a destination address identical to the source address. If there are no problems in the 82501/82502 circuits, the station will be receiving its own transmitted frames. If problems exist, the station will only be transmitting. Since the 82586 is configured to TONO-CRS (Transmission On NO Carrier Sense), the chip will keep trans-

mitting regardless of the state of carrier sense. The 82501/82502 circuits can then be probed with an oscilloscope at the locations indicated in Figure 21. Probing will catch problems like wiring mistakes, missing load resistors, etc.

Once the station is debugged, it can be connected to the network. If there is a problem in the network, the 82586's TDR command can be used to find the location and nature of the problem.

Figure 17. Flowchart for 80186/82586 System Troubleshooting

Figure 17. Flowchart for 80186/82586 System Troubleshooting (Continued)

Figure 18. Example of Logic Analyzer Trace

Figure 19. Flowchart for 82501/82502 Circuits Troubleshooting

```

Initialization begun

Configure command is set up for default values.

Do you want to change any bytes? (Y or N) ==> Y

Enter byte number (1 - 11) ==> 4

Enter byte 4 (4H) ==> A6H

Any more bytes? (Y or N) ==> Y

Enter byte number (1 - 11) ==> 9

Enter byte 9 (9H) ==> 08H

Any more bytes? (Y or N) ==> Y

Enter byte number (1 - 11) ==> 11

Enter byte 11 (BH) ==> 6

Any more bytes? (Y or N) ==> N

Configure the 586 with the prewired board address ==> N

Enter this station's address in Hex ==> 000000002200

You can enter up to 8 Multicast Addresses.

Would you like to enter a Multicast Address? (Y or N) ==> N

You entered 0 Multicast Address(es).

Would you like to transmit?

Enter a Y or N ==> Y

Enter a destination address in Hex ==> 000000002200

Enter TYPE ==> 0

How many bytes of transmit data?

Enter a number ==> 2

Transmit Data is continuous numbers (0, 1, 2, 3, ...)

Change any data bytes? (Y or N) ==> N

Enter a delay count ==> 0

Setup a transmit terminal count? (Y or N) ==> N

Destination Address: 00 00 00 00 22 00

Frame Length: 20 bytes

Time Interval between Transmit Frames: 159.4 seconds

Network Percent Load generated by this station: 11.0 % Transmit Frame Terminal Count: Not Defined

Good enough? (Y or N) ==> Y

292010-77

```

Figure 20. TSMS Initialization for 82501/82502 Circuits Troubleshooting

Figure 21. Probing 82501/82502 Circuits

APPENDIX A

LANHIB SCHEMATICS

PARTS LIST

PAL EQUATIONS

DIP SWITCH SETTINGS

WIRE WRAP SERVICES

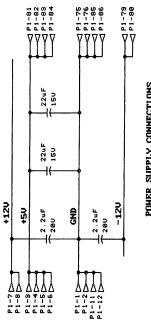

POWER SUPPLY CONNECTIONS

THE BOARD REQUIRES +50, +120, AND -120. HULTIBUS POWER PINS FOR THESE UOLTAGES AND GROUND ARE SHOWN ABOUE.

EACH IC SHOULD HAVE A 0.1 LF CAPACITOR BETHEEN POWER PIN AND GROUND PIN. PARTS LIST DOES NOT INCLUDE DECOUPLING CAPACITORS. 'n

8 αΞ 292010-78

| REFERENCES<br>U1<br>U2 |                              | MFR       |      |      |

|------------------------|------------------------------|-----------|------|------|

|                        | 20100000                     |           | Ę.   | į    |

| U1<br>U2               |                              | PART NO.  | CODE | QTV. |

| UZ                     | 10                           | 74532     | OBD  | -    |

|                        | IC                           | 74LS84    | OBD  | 1    |

| U3. U4                 | 10                           | 74LS245   | OBD  | 2    |

| - 1                    | IC                           | 74F373    | OBD  | . 1  |

| U6. U7                 | IC                           | 74LS373   | OBD  | 2    |

| 80                     | IC                           | 80186     | LNI  | -    |

| 60                     | 10                           | 82586     | HNI  | -    |

| 010                    | IC                           | 1618      | OBD  | -    |

|                        | 10                           | 74LS02    | OBD  | -    |

| U12, U27               | 10                           | 74LS74    | OBD  | ~    |

| U28                    | 01                           | 749574    | CEO  | -    |

| 013                    | 10                           | 747 5165  | L BU | -    |

| 014                    | 1.0                          | 82581     | 12   | -    |

| 1115                   | Dules Transformer Dack       | 00000     |      | -    |

| 116                    | 10 10 10 10                  | 02502     | 12   | -    |

| 1113                   | 20,000                       | 20070     |      |      |

| 110                    | TO CAL BLA FRAGE             | PE04303   | 1    | -    |

|                        | 10. 84h Bit Erkun            | 27000     | Z    | 7    |

| 2011                   | 7080                         | 74HS88    | 080  | -    |

| 134                    | TO SERIE                     | HT5254-15 |      | 1    |

| 135                    | 3 7 0 - 0                    | 127183838 |      | -    |

| 670                    | 14                           | 74RS04    | OBD  | -    |

| 023                    | 10                           | 82530     | INT  | -    |

| 038                    | IC                           | 1489      | OBD  | -    |

| U31                    |                              | 1488      | OBD  | -    |

| 1                      | it EPROM (Optiona            | 27210     | HNI  | -    |

| K1-K3, K6              | Resistor, 10K ohm, 1/4W, 5%  | COMI      | 080  | ဖ    |

| -                      | 1000                         |           |      |      |

| 1                      | TOOK ONE. 174M.              | CONT      | OBD  | -    |

| 00 00                  | RESISTOF, Z.ZR ODM, 1/4W, 5% | CONT      | OBD  | -    |

|                        | CO. C Chim. I/BM.            | COUL      | ngo. |      |

| - 1                    | . 240 OUM.                   | COMI      | OBD  | ~    |

| 111                    | I ONE                        | COMI      | OBD  | -    |

| 219-619                | (min), 56                    |           |      |      |