int

APPLICATION NOTE

May 1986

# Implementing an EPLD Design Using Intel's Programmable Logic Development System

LAKSHMI JAYANTHI DSO APPLICATIONS

8-9

### **OVERVIEW**

Welcome to the fascinating world of ERASABLE PRO-GRAMMABLE LOGIC DEVICES (EPLDs) and Intel's Programmable Logic Development System (iPLDS). This application note has been written for the newcomer to Intel's devices and design tools. It has been designed as a step-by-step guide through the tools but should also prove useful as a reference document for the experienced logic designer.

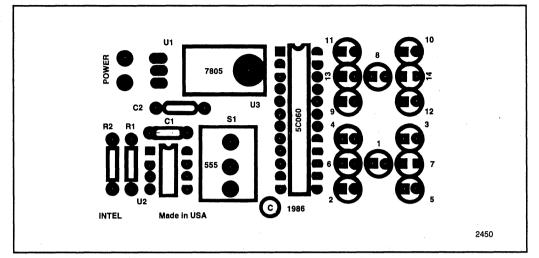

By the end of this application note you will have designed/solved multiple logic problems and be in a position to implement solutions to many of the digital design challenges you face today. It is anticipated that this application note will be used in conjunction with Intel's iPLS software. To increase the usefulness of this application note, Intel will supply a PCB card for you to experiment on and a sample diskette (see Appendix E for details).

This application note is divided into the following three sections:

- 1. An introduction to Erasable Programmable Logic Devices (EPLD)

- 2. An introduction to Intel's Programmable Logic Development System (iPLDS)

- 3. Implementation of EPLD and iPLDS using detailed examples to implement a logic design.

### INTRODUCTION

Programmable logic in the form of PALs have been available for some time. They have become more complex as Large Scale Integration (LSI) techniques have been applied to this technology.

The benefits of Large Scale Integration circuits are many fold. These circuits offer lower manufacturing costs, since the use of customized LSI circuits reduces required printed circuit board space, thereby significantly reducing board costs. These circuits also consume lower power so less expensive power supplies are required and cooling fans are also eliminated. LSI circuits also have higher reliability than equivalent systems comprised of many low density standard components.

As end users of semiconductors moved into higher and higher levels of integration, chip designers found it more and more difficult to define larger and larger blocks of logic. These difficulties led to the emergence of the user-defined Application Specific Integrated Circuit (ASIC).

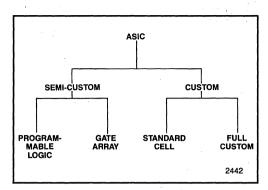

The options available for application specific logic are explained below and shown in Figure 1.

Figure 1. Logic Options

Full Custom: These circuits can be tailored to give the best functional performance with the highest level of integration, the smallest silicon area, the lowest power use, and be produced for the least cost at high production volumes.

Standard Cell Library: This approach represents an integrated circuit which is composed of predesigned and precharacterized cells chosen from a computer data base library of cells.

Gate Arrays: These are integrated circuits that contain a regular, usually square, matrix of predefined logic gates.

**User Programmable Logic:** The concept of user programmable logic is to provide the designer with the benefits of custom LSI chips from standard products.

A recent innovation in the programmable logic field has been Intel's introduction of an ERASABLE Programmable Logic Device. Using the same technology used in the manufacture of EPROMs, Intel now offers increased flexibility to the logic designer.

Intel has addressed the limitations of gate arrays and fuse programming logic with its EPLD products and development system support tools. The benefits to the system designer are:

- · Greatly reduced lead times

- Low design costs

- Ease of design changes

- Low power dissipation from CHMOS technology

- Multiple programming facility

- Maximum flexibility in each chip and the ability to erase and reprogram

- High density products that maximize function, integration, and quality

- A self-contained, low-cost sophisticated development system based upon the industry standard IBM PC XT or AT.

Table 1. Intels EPLDs

| EPLD  | Gates | Pins | Dedicated<br>Inputs | 1/0 |

|-------|-------|------|---------------------|-----|

| 5C031 | 300   | 20   | 10                  | 8   |

| 5C060 | 600   | 24   | 4                   | 16  |

| 5C090 | 900   | 40   | 12                  | 24  |

| 5C121 | 1200  | 40   | 13                  | 24  |

| 5C180 | 1800  | 68   | · 12                | 48  |

EPLDs are now a cost-effective solution to the problem of large scale logic integration. EPLDs are the simplest form of high density application-specific logic to implement. At present, the following logic devices are available from Intel as shown in Table 1.

Intel's EPLDs use the "Sum Of Products" architecture with programmable AND and fixed OR gates to drive a combinatorial or registered output. Each of the devices listed in Table 1 has different attributes and resources targeted at specific applications.

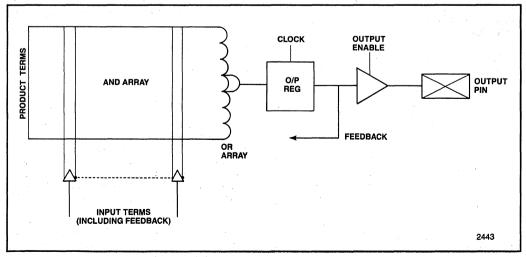

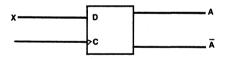

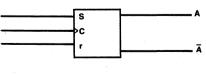

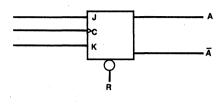

In general each device contains multiple sets of programmable MACROCELLS as shown in Figure 2.

Everything is programmable (and erasable if you need to make modifications). Product terms may be generated from any combination of input terms—any terms not used are considered a "don't-care" in the array. The output register is also programmable—you can choose D-type, Toggle, SR, or even JK FLIP-FLOPs; you can even choose no output register if you only require combinatorial outputs. The clock and output enables are also programmable. Intel EPLD devices are available in many configurations to fit most applications. A complete listing of data sheet availability is covered in Appendix E.

# DESIGN TECHNIQUES USING INTEL'S EPLDS

Designing with EPLDs is similar to designing with standard TTL logic circuits. The focus moves from "how can I configure this design with standard parts" to "what else could I replace using this EPLD". Remember, if you ever use all of an EPLDs resources you just move up the device chain to the next bigger component—all of the work you did is DIRECTLY PORTABLE to a larger device.

Any network, either combinatorial or registered, has an equivalent two level form. Any logic circuit consisting of AND, OR, NOR, NAND, XOR Logic can easily be converted into the corresponding truth table. Any Boolean expression, no matter how complex, may be written in Sum-Of-Products form. This Sum-Of-Products expression that has been derived from the truth table can be reduced until it has as few product terms as possible. This procedure can be repeated for any complex network.

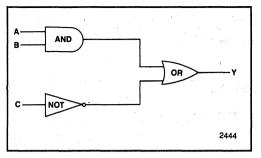

Let us consider a very simple network as shown in Figure 3. This logic circuit consists of an AND gate, an OR gate and a NOT gate. The inputs are A, B, C, and the output is Y.

For this simple network, the truth table is shown in Table 2:

A Boolean expression can easily be written from the truth table in a Sum-Of-Products form. This expression contains the relationship between the inputs and the output.

Figure 2. Macrocell Arch

Figure 3. Simple Network

Note that the output Y is true in five of these eight states (0,2,4,6, and 7) so expressing Y in the form "Sum-Of-Products" by writing the ones in terms of A, B, and C yields:

### Y = /A\*/B\*/C + /A\*B\*/C + A\*/B\*/C + A\*B\*/C + A\*B\*C

Hence, given any network, that network can be converted into its truth table. Next, a Sum-Of-Products expression that has the same truth table can be derived. If so desired, this Sum-Of-Products expression can be reduced using DeMorgan's theorem to simplify the circuit (you will see later that this will not be required).

### **DEVELOPMENT SUPPORT**

Development tools are critical to the use of new technologies because tools allow you to control and use a new technology. Good tools help you, the designer, to work in familiar methods, then translate the design to the device.

Good tools broaden the applications by making it easy to use new technology in designs. They are not a barrier to using the technology, but encourage its use and applications.

Advanced and innovative technologies need similar advancements and innovations in the corresponding tools.

| STATE |   | INPUT |   | OUTPUT |

|-------|---|-------|---|--------|

|       | A | В     | С | Y      |

| 0     | 0 | 0     | 0 | 1      |

| 1     | 0 | 0     | 1 | 0      |

| 2     | 0 | 1     | 0 | 1      |

| 3     | 0 | 1     | 1 | 0      |

| 4     | 1 | 0     | 0 | 1      |

| 5     | 1 | 0     | 1 | 0      |

| 6     | 1 | 1     | 0 | · 1    |

| 7     | 1 | 1     | 1 | 1      |

Table 2.

iPLDS, Intel's Programmable Logic Development System, provides a full spectrum of ways to design and use a variety of design tools with fast, easy-to-use entry software.

The iPLDS contains all the software, hardware, documentation and devices needed to program EPLDs. iPLDS are the most advanced PLD design tools available. It provides better utilization of device resources (more gates per chip) than any other development software. These versatile tools are for users with different skill levels and applications. iPLDS tools handle the details of converting your design to working silicon on the personal computer.

The iPLDS contains the three fundamental modules

- Logic Builder (LB)

- Logic Optimizing Compiler (LOC)

- Logic Programmer Software (LPS)

To implement the logic design we will use the iPLDS modules in the order listed above.

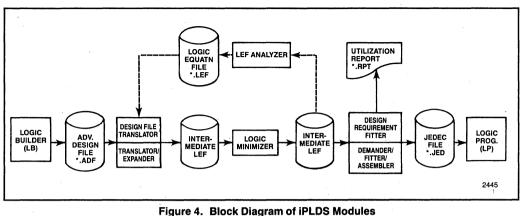

The modules are essentially independent modules that use special data files to pass information as shown in Figure 4. These data files are the ADF, RPT, LEF, and JED files.

The Advanced Design File (\*.ADF) is generated from the Logic Builder and contains the Inputs/outputs and all the primitive equations.

The Logic Equation File (**\***.LEF) contains the primitive equations that have been minimized by the Logic Optimizing Compiler.

The Utilization Report File (\*.RPT) contains information on the macrocell and pin assignments.

The JEDEC File (\*.JED) is the file generated by the Logic Optimizing Compiler used to program the device using the Logic Programmer.

Before implementing the logic design using the iPLDS, let us briefly discuss the iPLDS family of parts to be familiar with the iPLDS modules.

### Logic Builder (LB)

The Logic Builder module guides you through the entire process of design entry by prompting for necessary information and showing a screen display (one primitive at a time) with input signals on the left side and output signals on the right side. The Logic Builder is used to generate an Advanced Design File (or ADF) by inputting the data in netlists or Boolean equations.

After all required data are entered, the Logic Builder module indicates whether the circuit is complete and properly connected. If any changes need to be made, the module enables you to edit the circuit design either by

Figure 4. Block Diagram of IFLDS Modul

systematically scanning through the primitives in the Advanced Design File (ADF) or by directly finding a primitive by the name of a node connected to it.

Any circuit may be edited. The Logic Builder reads in the ADF and prompts you for changes. The Logic Builder also allows two or more partially complete ADF files to be MELDED together to form a more complex function. This concept is not discussed in this application note but will be a topic of a future application note.

## Logic Optimizing Compiler (LOC)

The Logic Optimizing Compiler provides an easy-to-use interface to the Logic User System software. Regardless of the type of design entry method used, the LOC first translates an Advanced Design File (ADF) into internal logic equations; then it performs a Boolean reduction on the translated design, and finally produces a JEDEC Standard File, which is then used to program an Intel EPLD. In addition, you have the option of requesting an analysis of the Logic Equation File (LEF) as output by the Minimizer module.

The LOC performs the following functions:

- The TRANSLATOR translates the ADF into an intermediate Logic Equation File (LEF). (Most errors are detected and corrected).

- The EXPANDER expands the Boolean equations into Sum-Of-Products form, removes redundant factors from product terms, and produces another LEF.

- The MINIMIZER performs a sophisticated Boolean reduction on the translated design to maximize utilization of the EPLD.

- The LEF Analyzer converts the LEF output by the MINIMIZER into a human readable file to allow you to see your design. (\*.LEF)

- The DEMANDER organizes the file output by the MINIMIZER.

- The FITTER matches your design requirements with the known resources of the Intel device.

- The ASSEMBLER converts the fitted requests into JEDEC file.

## Logic Programmer Software (LPS)

The Logic Programmer Software provides a user interface to the JEDEC Standard File output of the Logic Optimizing Compiler and to the Logic Programmer Interface. You can use the Logic Programmer Software to view JEDEC files and to program your designs into EPLDs.

The Logic Programmer Software is used

- · to program your designs into EPLDs

- to verify the validity of data in the device

- · to read data from the device

- · to display JEDEC data graphically

- · to edit JEDEC data

### HARDWARE REQUIREMENTS

The iPLDS requires an IBM PC XT, PC AT, or other compatible computer. A color monitor is preferred. The computer must have at least one 360K double-sided double-density disk drive, a second 360K floppy disk or hard disk, and at least 512K bytes of RAM memory.

The iPLDS consists of the Logic Programmer Interface card, and the programming unit needed to program and verify EPLDs. The Intel iUP 201 with a GUPI adapter may be used as an alternate system to program the EPLD devices.

## SOFTWARE REQUIREMENTS

The personal computer should be capable of running DOS V3.0 or a higher version. The Intel Programmable Logic

Software (iPLS) that contains the software controlling the logic programmer interface and assisting in the design of Intel applications is shipped on floppy diskettes.

## PROBLEM DEFINITION

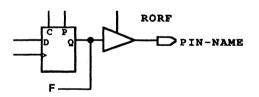

We are going to use iPLDS to implement a medium complexity logic function. As a vehicle to show the usage of the tools and design techniques we will design a circuit that will roll and spin a pair of dice. The design has been split into multiple stages for illustration purposes.

This example has been chosen since it incorporates many of a typical logic design tradeoffs and also solves many of the typical problems a hardware logic designer will encounter.

Appendix A contains some basic definitions that may be useful when reading through the design and its implementation.

### DESIGN SAMPLE

### **Problem Set-up**

The circuit is designed to set both of the dice spinning when you push a switch and display a random set of numbers when you release the switch. The dice will spin at a rate that is visually pleasing and roll at the highest possible rate to ensure randomness.

You will implement the design in the following steps:

A. One dice that will roll out a number.

B. Add a switch that will control the roll/not roll action.

C. Add a second dice to roll a number.

D. Add a spinning option to both dice.

E. Retro-fit a power save feature to extend battery life.

Hence, at the end of the five design steps you will have a pair of dice spinning and showing a pair of numbers between 1 and 6 in a very random manner. At the end of the five design steps, you will have added a very realistic and practical feature to your design and that is extending the battery life by a power saving option. It is important to note that the five steps mentioned above are sequential steps in that step C can be achieved only after steps A and B etc. Let us describe the sample circuit for the dice rolling example. It is a very simple circuit allowing you to concentrate upon the design process. It illustrates the possible design stages and considerations in detail.

### PART A

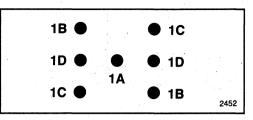

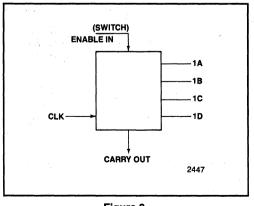

Four Outputs—1A, 1B, 1C, 1D are required to drive the LEDs arranged in a DICE pattern as shown in Figure 5.

Figure 5. Dice Configuration

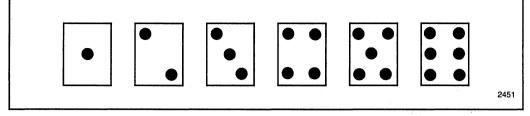

Operating sequence—Rolling dice from 1 to 6 and the block diagram of the circuit, both shown in Figure 6.

The total number of states that are possible is 16 since the four LED pairs generate a permutation of (2\*\*4) = 16. The LEDs should be lit up such that any number between 1 and 6 inclusive is shown. Hence, out of the 16 possible states, only six states are valid. This leaves ten invalid states.

If the LEDs come up in a valid state upon power up, then a number between 1 and 6 will be displayed.

However, if the LEDs come up in an invalid state upon power up, then you have to design the circuit such that any one of the ten invalid states will fall into a valid state.

If the LEDs fall into any one of the ten invalid states, then you have designed the circuit to move into a state where 1A, 1B, 1C, 1D have zero logic values respectively on the next clock edge. Every time a zero logic value appears in the invalid states, then at the next clock edge, LED 1A gets lit up generating a valid state. Since 1 is a valid state, the numbers between 1 and 6 inclusive will be displayed at all subsequent clock edges.

Listed below are the steps involved in designing the logic circuit.

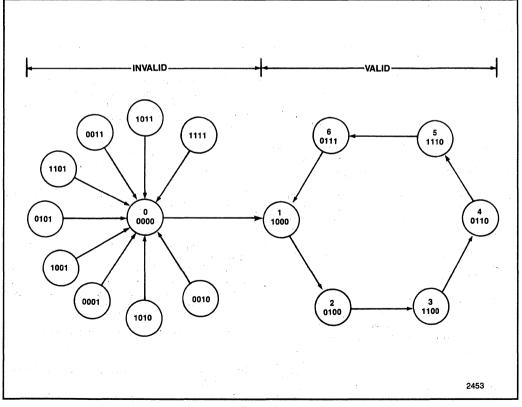

STEP 1. Generate the state diagram to clearly show the operating sequence including the status of the outputs for each state and the influence of the inputs on the next state transitions as shown in Figure 7. We have arbitrarily chosen that the states should count 1,2,3,4,5,6, and repeat. You could have implemented the design using any sequence but we chose the most obvious. Note how most of the invalid states move you to state 0 which then puts us into a valid state which then repeats forever.

STEP 2. Generate a truth table with entries for all available states and combinations of inputs, and use the next states resulting from these as shown in Table 3. The bracketed numbers, (3) etc., show the number being

intല്

Figure 6. Rolling Sequence

displayed on the dice and the 0, 1 values of 1D, 1C, 1B, and 1A indicate which LEDs should be OFF/ON to display the required dice pattern.

STEP 3. Convert the truth table directly into Sum-Of-Products equations as shown below:

DICE1A has four entries; 3 from the valid states and one to control the invalid states

DICE1A = (/1A\*1B\*/1C\*/1D + /1A\*1B\*/1C\*/1D + /1A\*1B\*1C\*1D + /1A\*/1B\*/1C\*/1D) DICE1B has five entries from valid states

DICE1B = (1A\*/1B\*/1C\*/1D + /1A\*1B\*/1C\*/1D + 1A\*1B\*/1C\*/1D + /1A\*1B\*1C\*/1D + 1A\*1B\*1C\*/1D)

DICE1C has three entries from valid states

DICE1C = (1A\*1B\*/1C\*/1D + /1A\*1B\*1C\*/1D + 1A\*1B\*1C\*/1D)

Table 3 Truth Table for DICE1

|     |       |              |      |       |   | 101 | pie 3. | muun       | lable   |        | /E I       |     |        |         |          |

|-----|-------|--------------|------|-------|---|-----|--------|------------|---------|--------|------------|-----|--------|---------|----------|

|     | Input | t State      |      |       |   |     |        |            |         |        | Output Sta | ate | • •    |         |          |

| 1A  | 1B    | 1C           | 1D   |       |   |     | 1A     | 1 <b>B</b> | 1C      | 1D     |            | 1A  | 1B     | 10      | 1D       |

|     |       |              |      |       |   |     |        | Valio      | l state |        |            |     | Invali | d state | Э        |

|     |       |              |      | 1.1.1 | С | HAN | GE TO  | THE        | NEXT    | VALID. | STATE      |     |        |         |          |

| 1   | 0     | 0            | 0(1) |       |   |     | 0      | · • 1      | 0       | 0(2)   |            |     |        |         |          |

| 0   | 1     | 0            | 0(2) |       |   |     | ~ °1   | 1          | 0       | 0(3)   |            |     |        |         |          |

| 1 - | 1     | 0            | 0(3) |       |   |     | 0      | . 1        | 1       | 0(4)   |            |     |        |         |          |

| 0   | 1     | 1            | 0(4) | •     |   |     | 1 1 °  | 1          | 1       | 0(5)   |            |     |        |         |          |

| 1   | 1     | · 1          | 0(5) |       |   |     | 0.     | 1          | ່ 1     | 1(6)   |            |     |        |         |          |

| 0   | 1     | - <b>1</b> - | 1(6) |       |   |     | 1      | 0          | 0       | 0(1)   |            |     |        | • •     |          |

|     |       |              |      |       |   | CON | NTRO   | LTHE       | INVAL   | ID STA | TES        |     |        |         | <b>-</b> |

| 0   | 0     | 1            | 0    |       |   |     |        |            |         |        |            | 0   | 0      | 0       | 0        |

| 1   | 0     | 1            | 0    |       |   |     |        |            |         |        |            | Ő   | Ō      | ō       | Ō.       |

| 0   | 0     | 0            | 1    |       |   |     |        |            |         |        |            | Ő   | Ō      | ō       | 0        |

| 1   | Ō     | 0            | 1    |       |   |     |        |            |         |        |            | 0   | Ō      | Ō       | 0        |

| Ó   | 1     | Õ            | 1    |       |   |     |        |            |         |        |            | 0   | Ō      | Ō       | 0.0      |

| 1   | 1     | 0            | 1    | χ.    |   |     |        |            |         |        |            | · 0 | 0      | 0       | 0        |

| 0   | 0     | 1            | 1    |       |   |     |        |            |         |        |            | 0   | 0      | 0       | 0        |

| 1   | 0     | 1            | 1    |       |   |     |        |            |         |        | · ·        | 0   | 0      | 0       | 0        |

| 1   | 1     | 1            | 1    |       |   |     |        |            |         |        |            | 0   | 0      | 0       | 0        |

| 0   | 0     | 0            | 0    |       |   |     |        |            |         |        |            | 1   | 0      | 0       | 0(1)     |

DICE1D has one valid entry

DICE1D = (/1A\*1B\*1C\*1D)

Note that no attempt has been made to minimize these equations - the iPLS software that you will use later contains reducing algorithms and other techniques to optimize the design. This allows you to focus upon the problem and not on tasks such as Karnaugh map reduction which a computer can often do better anyway.

Having designed part A of the circuit, you can now move on to tool usage to implement the design. Refer to the Intel Programmable Logic Software Manual if you have not installed the iPLS software.

In order to invoke iPLS type the following command

C:\IPLS>IPLS <Enter>

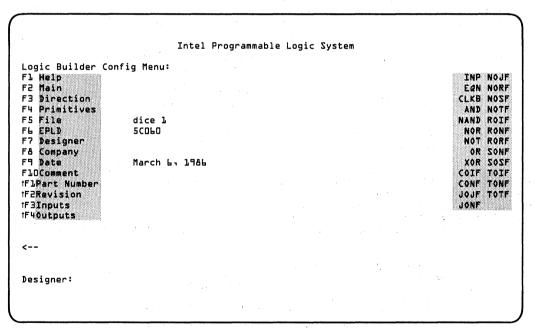

The iPLS menu will appear as shown in Screen 1.

The number to the left of each function allows you to select a function with a function key. Two kinds of function keys are available: toggle keys and field keys.  $\langle F3 \rangle$  and  $\langle F4 \rangle$  are toggle keys. All other keys are field keys. Functions beyond  $\langle F10 \rangle$  are executed by pressing the  $\langle Shift \rangle$  key together with the function key. Press  $\langle F3 \rangle$  to invoke the Logic Builder and observe the Logic Builder menu as shown in Screen 2. The first prompt asks for the file name. If the file already exists, its header information and primary inputs and outputs are displayed. If you enter a new file name, the Logic Builder module prompts for all the functions remaining on the screen.

### Enter: DICEL <Enter> CreateNewNetlist(Y/N):Y

In this sample session, user entries are all in uppercase letters. Note: IPLS is case sensitive.

When initially invoked, the Logic Builder module displays its configuration menu. The Logic Builder configuration menu shows "5C121" as the default Intel part and, on the right side of the menu, displays those primitives that are legal for use with the 5C121. As soon as you enter another part (e.g. 5C060) the list of primitives changes to display the primitives applicable to that specific part.

Press  $\langle F6 \rangle$  and enter 5C060 when prompted for user entry.

Screen 2 shows the Logic Builder Configuration Menu for the 5C060.

• The left side of the screen shows a menu of functions, each preceded by a function key number.

| PLS Menu                |                |               |       |  |

|-------------------------|----------------|---------------|-------|--|

| 'L Help                 |                |               |       |  |

| 2 Exit                  |                |               |       |  |

| 3 Logic Builder         |                |               |       |  |

| '4 LOC                  |                |               |       |  |

| 5 Logic Programmer      |                |               |       |  |

| 6 Directory             |                |               |       |  |

| 7 Rename File           |                |               |       |  |

| A Copy File             |                |               |       |  |

| 9 Delete File           | <i>*</i>       |               |       |  |

| 10D0S command           |                |               |       |  |

|                         |                |               |       |  |

| PLS Version 3.0, Copyr: | ight (C) 1985. | Intel Corpora | ation |  |

|                         |                | Altera Corpor |       |  |

| Sc | re | er | ז ו | ۱. |

|----|----|----|-----|----|

|    |    |    |     |    |

Screen 2.

|      | Prompt      | User Entry                           |

|------|-------------|--------------------------------------|

| FЬ   | EPLD        | 50060                                |

| F7   | Designer    | Your Name                            |

| Fð   | Company     | Your Company                         |

| F٩   | Date        | Present Date                         |

| F10  | Comment     | 0ur first design                     |

| tFl  | Part Number | 0.1                                  |

| tF2  | Revision    | 1-0 (                                |

| tF 3 | Inputs      | CLOCKOJ                              |

| tF4  | Outputs     | DICELA@L0,DICELB@9,DICELC@8,DICELD@7 |

Table 4.

- The right side of the screen shows the list of available primitives (these are discussed in detail later).

- The two lines at the bottom of the screen are designated for comments (first line) and prompts (second line).

- The center of the screen is used to show a representation of the primitive; name and pictorial representation are in the middle, input signals are to the left, and output signals are to the right of the primitive.

- The direction of the arrow located on the left side of the screen below the list of functions determines the starting point and direction of design entry. If the arrow points to the left, entry is from output pins to input pins. If the arrow points to the right, entry is from input pins to output pins.

#### NOTE

We have assigned pin numbers to pin names by using the "@" symbol within the name of the logic variable. Specific pin numbers need not be assigned if not desired. In that case, the Logic Builder will assign its pin numbers for you.

Type in the information as given in Table 4 in the Logic Builder Config Menu. The information is also shown in Screen 3. After entering all of this required information, iPLDS will automatically prompt you through defining the circuit, starting with a primitive to drive the last output specified.

Once in the Logic Builder main menu, you are guided with prompts to enter information as follows:

Enter the name of the primitive to connect to the first node. The name may be entered by typing the name of the primitive, which highlights the appropriate primitive on the right side of the menu, then pressing < Enter >.

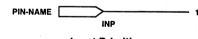

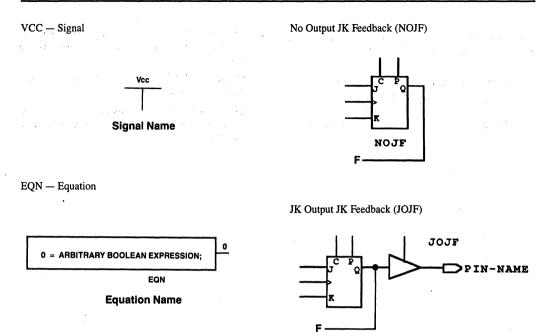

Subsequently, a representation of the primitive is displayed in the center of the screen surrounded by input and output signals. You are prompted for names of nodes to connect to each of the signals. The Design Primitives library contains approximately 80 basic functional blocks needed for designing circuits in programmable logic products. Design Primitives are divided into the following groups:

- Input Primitives (INP,LINP)

- Logic Primitives (AND,GND,CLKB,NOT,VCC,OR,NAND,NOR,XOR)

- Equation Primitives (EQN)

- I/O Primitives (JOJF, NOJF, NORF, RORF, etc)

Refer to Appendix A for an explanation of the Primitives used in this example.

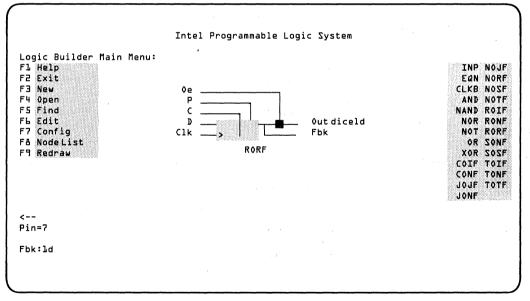

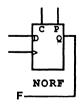

The logic is based on input clock transitions. At the rising edge of the clock we want the LEDs to generate a particular state depending on the input state. You want the output of the LEDs to follow the input, which is basically a D-TYPE FLIP-FLOP. You also require the feedback to generate the next state, which means that you should use a D-TYPE FLIP-FLOP with FEEDBACK or RORF as shown in Screen 4.

### NOTE

The Logic Builder module starts with the last output entered.

When you are prompted to select a primitive to drive DICE1D enter:

#### Select a primitive to drive DICELD07: RORF <Enter>

Now you are prompted for the remaining connections:

For FBK: 1D <Enter>

For 0E<sub>1</sub> P<sub>1</sub> C: Press <Enter> (VCC<sub>1</sub> GND are the defaults).

For D: INLD <Enter>

For CLK: CLOCK <Enter>

Select a primitive to drive CLOCK: INP <Enter>

|                                                                                                                  | Intel Programmable Logic System      |           |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------|

|                                                                                                                  |                                      |           |

| .ogic Builder Con<br><sup>-</sup> l Help                                                                         | fig Menu:                            |           |

| 2 Main                                                                                                           |                                      | INP NOJF  |

| 3 Direction                                                                                                      |                                      | EQN NORF  |

|                                                                                                                  |                                      | CLKB NOSF |

| 4 Primitives                                                                                                     |                                      | AND NOTP  |

| 5 File                                                                                                           | dice l                               | NAND ROIF |

| L EPLD                                                                                                           | 5C060                                | NOR RONF  |

| 7 Designer                                                                                                       | Your name                            | NOT RORF  |

| 8 Company                                                                                                        | Your company                         | OR SONF   |

| 9 Date                                                                                                           | March Ly 1986                        | XOR SOSF  |

| 10Comment                                                                                                        | Our first design                     | COIF TOIF |

| Fl Part Number                                                                                                   | 0.1                                  | CONF TONF |

| F2 Revision                                                                                                      | <b>J-O</b>                           | JOJF TOTF |

| F3 Inputs                                                                                                        | clock@l                              | JOJF      |

| F4 Outputs                                                                                                       | DICELAQIO,DICELBQ9,DICELCQ8,DICELDQ7 |           |

|                                                                                                                  |                                      |           |

|                                                                                                                  |                                      |           |

|                                                                                                                  |                                      |           |

| utputs:DICE14010                                                                                                 | "DICETB94"DICETC98"DICETD95          |           |

| and the second |                                      |           |

|                                                                                                                  |                                      |           |

Screen 3.

Screen 4.

# inteľ

In: CLOCK <Enter>

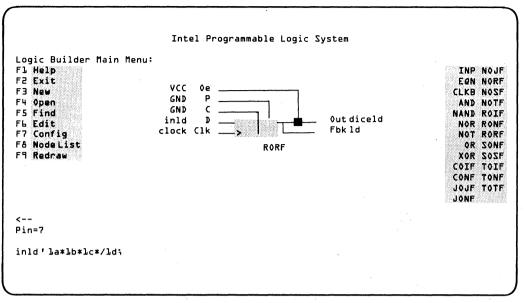

Select a primitive to drive INLD: EQN <Enter>

After you are prompted for the equation, type it in as derived in the Problem Set-up section. Please note that "/" indicates a logical "NOT", "**\***" indicates a logical "AND", and "+" indicates a logical "OR". The equation is terminated by a ";" as shown in Screen 5.

INLD = (LA \* LB \* LC \* /LD); <Enter>

The following prompts and design entries, as shown in Table 5, are needed to complete the design entries for DICE1C, DICE1B, and DICE1A respectively.

The Logic Builder will stop prompting for primitives once you have entered the complete design.

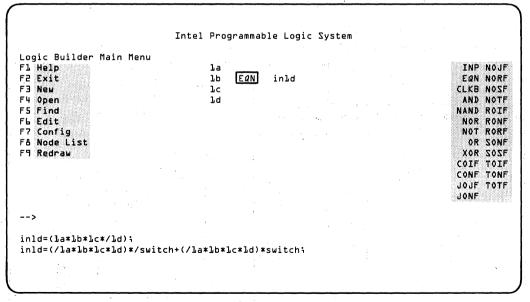

Press  $\langle F8 \rangle$  to show the design so far as shown in Screen 6.

Press < F2> to exit.

The Logic Builder main menu is cleared, replaced by the Logic Builder exit menu.

To save the configuration and return to iPLS menu you must press <F6> (Save-Exit).

Note that you are saving the Advanced Design File (ADF) that is generated by the Logic Builder.

You can print the ADF file that has been created at the end of this session if you so desire. You can use  $\langle F10 \rangle$ when in the iPLS main menu to print the ADF file for a listing. You can verify your file with the DICE1. ADF file given in Appendix D. If you desire a listing, while you are in the iPLS main menu, type the following:

<Flo> <Enter>

PRINT DICEL.ADF <Enter>

### Submitting the ADF to the LOC

This ADF file is now compiled using the Logic Optimizing Compiler. To enter the ADF created with the Logic Builder module into the Logic Optimizing Compiler (LOC), press < F4 > to access the LOC menu.

| PROMPT                                                                                                          | USER ENTRY                                        |

|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| Select a primitive to drive LC:                                                                                 | RORF <enter></enter>                              |

| Out:                                                                                                            | DICELC <enter></enter>                            |

| 0e:                                                                                                             | VCC <enter></enter>                               |

| P:                                                                                                              | GND <enter></enter>                               |

| C:                                                                                                              | GND <enter></enter>                               |

| D:                                                                                                              | INLC <enter></enter>                              |

| Select a primitive to drive INLC:                                                                               | EQN <enter></enter>                               |

| INLC:                                                                                                           | (lA*lB*/lC*/lD)+(/lA*lB*lC*/lD)+(lA*lB*lC*/lD);   |

|                                                                                                                 | <enter></enter>                                   |

| Select a primitive to drive LB:                                                                                 | RORF <enter></enter>                              |

| Out:                                                                                                            | DICE1B <enter></enter>                            |

| 0e:                                                                                                             | VCC <enter></enter>                               |

| P:                                                                                                              | GND <enter></enter>                               |

| C:                                                                                                              | GND <enter></enter>                               |

| D:                                                                                                              | IN1B <enter></enter>                              |

| Select a primitive to drive INLB:                                                                               | EQN <enter></enter>                               |

| IN1B:                                                                                                           | (lA*/lB*/lC*/lD)+(/lA*lB*/lC*/lD)+(lA*lB*/lC*/lD) |

|                                                                                                                 | +(/1A*1B*1C*/1D)+(1A*1B*1C*/1D); <enter></enter>  |

| Select a primitive to drive LA:                                                                                 | RORF <enter></enter>                              |

| Out:                                                                                                            | DICELA <enter></enter>                            |

| 0e:                                                                                                             | VCC <enter></enter>                               |

| P:                                                                                                              | GND <enter></enter>                               |

| C:                                                                                                              | GND <enter></enter>                               |

| D :                                                                                                             | INLA <enter></enter>                              |

| Select a primitive to drive INLA:                                                                               | EQN <enter></enter>                               |

| INLA:                                                                                                           | (/lA*lB*/lC*/lD)+(/lA*lB*lC*/lD)+(/lA*lB*lC*lD)   |

| All and the second s | +(/lA*/lB*/lC*/lD); <enter></enter>               |

Table 5.

Screen 5.

Once the LOC menu is displayed, you are prompted through the LOC menu functions as follows:

The Input Format prompts you to specify your form of input: If input is in the form of a pinlist as output by DASH-2, enter P, if input is an Advanced Design File, enter an ADF or press <Enter> (ADF is the default). If output is a component list from PCAD, enter C.

### INPUT FORMAT: A <Enter>

#### FILE NAME: DICE1 <Enter>

MINIMIZATION: <Enter to select default>

INVERSION CONTROL: <Enter to select default>

#### LEF ANALYSIS: <Enter to select default>

After you have answered all the prompts, you are asked if you wish to run under the above conditions as shown in Screen 7.

DO YOU WISH TO RUN UNDER THE ABOVE CONDI-TIONS EY/N]?

Enter: Y

Finally you are prompted with:

### WOULD YOU LIKE TO IMPLEMENT ANOTHER DE-SIGNEY/NJ?

Enter: N

Note that the LOC generates a synopsis of its progress as shown in Screen 8. You are returned to the iPLS menu.

At the end of the LOC a JEDEC Standard File has been created which we will use in the Logic Programmer, DICE1.JED.

Also at the end of the LOC a report file is created, DICE1.RPT, which gives the pin configuration menu of the device. The DICE1.RPT file is given in Appendix D.

### **Programming the EPLD**

Finally, you submit your design to the Logic Programmer. In order for you to use the Logic Programmer, you must have the programming card plugged in. Please refer to the Intel Programmable Logic Software User Manual for installation instructions.

Alternatively you can use Intel's GUPI (Generic Universal Programmer Interface) to program your device.

|                                                                                                                  |              | Intel | Progr | ammabl | e Logi | c Syst | em |   |     |      |      |

|------------------------------------------------------------------------------------------------------------------|--------------|-------|-------|--------|--------|--------|----|---|-----|------|------|

| ogic Builder                                                                                                     | Main Menu:   |       |       |        |        |        |    |   |     |      |      |

| 1 Help                                                                                                           | clockal      |       |       |        |        |        |    |   |     | INP  | NOJF |

| 2 Exit                                                                                                           | dicela@lO    |       |       |        |        |        |    |   |     | EQN  | NORF |

| 3 New                                                                                                            | dicelb09     |       |       |        |        |        |    |   |     | CLKB | NOSF |

| 4 Open                                                                                                           | dicelc@8     |       |       | 1.11   |        |        |    |   |     |      | NOTF |

| 5 Find                                                                                                           | diceld07     |       |       |        |        |        |    |   |     | NAND |      |

| 6 Edit                                                                                                           | VCC          |       |       |        |        |        |    |   |     |      | RONF |

| 7 Config                                                                                                         | GND          |       | • •   |        |        |        |    |   |     |      | RORF |

| 8 Node List                                                                                                      | ld           |       |       |        |        |        |    |   |     |      | SONF |

| 9 Redraw                                                                                                         | inld         |       |       |        |        |        |    |   |     |      | SOSF |

|                                                                                                                  | clock        |       |       |        |        |        |    | 1 | · · | COIF |      |

|                                                                                                                  | la           |       |       |        |        |        |    |   |     | CONF |      |

| and the second | lb           |       |       |        |        |        |    |   |     | JQJF | TOTE |

|                                                                                                                  | lc           |       | ,     |        |        |        |    |   |     | JONF |      |

|                                                                                                                  | inlc         |       |       |        |        |        |    |   |     |      |      |

|                                                                                                                  | inlb         |       |       |        |        |        |    |   |     |      |      |

|                                                                                                                  | inla         |       |       |        |        |        |    |   |     |      |      |

|                                                                                                                  |              |       |       |        |        |        |    |   |     |      |      |

|                                                                                                                  |              |       |       |        |        |        |    |   |     |      |      |

| nconnected no                                                                                                    | des are bold |       |       |        |        |        |    |   |     |      |      |

| ress a functio                                                                                                   |              |       |       |        |        |        |    |   |     |      |      |

Screen 6.

Intel Programmable Logic System LOC Menu F1 Help F2 iPLS Menu F3 Input Format ADF F4 File Name dicel F5 Minimization Yes F4 Inversion Control No F7 LEF Analysis Yes Do you wish to run under the above conditions EY/N]?

Screen 7.

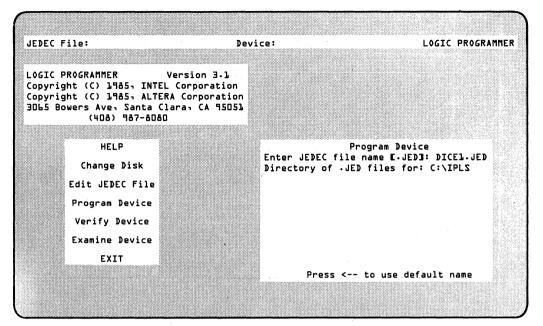

The iUP-GUPI and assorted GUPI LOGIC adaptors provide an alternative programming solution for Intel's H-series and EPLD devices, when purchased with the iPLS. This complete set of software is available without the Logic Programmer pod and the IBM interface card. While you are still in the iPLS menu, press  $\langle F5 \rangle$ . This function allows you to access the Logic Programmer Software. The Logic Programmer will now come up as shown in Screen 9.

| LOC Menu                        |                                                |  |  |

|---------------------------------|------------------------------------------------|--|--|

| Fl Help                         | ADF Minimization LEF-Analysis                  |  |  |

| F2 iPLS Nenu                    | dicel                                          |  |  |

| F3 Input Format<br>F4 File Name | ***INF0-L0C-Begin execution                    |  |  |

| F5 Minimization                 | ***INFO-LOC-ADF converted to LEF               |  |  |

| FL Inversion Control            | ***INF0-L0C-S.0.P. LEF produced                |  |  |

| 7 LEF Analysis                  | ***INF0-L0C-LEF reduced                        |  |  |

|                                 | ***INF0-L0C-LEF analyzed                       |  |  |

|                                 | ***INF0-L0C-Resource demand determined         |  |  |

|                                 | <pre>***INF0-L0C-Design fitting complete</pre> |  |  |

|                                 | ***INF0-L0C-JEDEC file output                  |  |  |

|                                 | LOC cycle successfully completed               |  |  |

|                                 |                                                |  |  |

| Would you like to imp           | lement another design [Y/N]?                   |  |  |

### Screen 8.

Use the cursor keys to select "Program Device" option.

When you are prompted

Enter JEDEC file name

Enter: DICEL.JED <Enter>

When you are prompted for:

Select Device For Programming

Enter: 5COLO <Enter>

When you are prompted for:

Do you wish to enable verify protection? **[Y/N]**?

Enter: N

When you are prompted for:

Do you wish to enable turbo-bit? **[Y/N]**?

Enter: N

Once you have answered all the prompts, the device is programmed and ready to be used in an actual circuit, as shown in Screen 10.

Exit from the Logic Programmer after saving the JEDEC file by using the "EXIT" option.

This completes part A of the design, which was to roll a single dice. The programmed device can be tested as described in Appendix C.

### PART B

Now that you have a good understanding of the manner in which a circuit is designed and also a good understanding of how the programming tools are used to program the device, you can proceed to the next step in the five stages of the dice design. According to the truth table generated in part A, the dice will roll a number between 1 and 6 inclusive as long as you supply a power source. When you disconnect the power source, all the LEDs will turn off. This will not be much help since you can only see the dice roll, but not actually see a number displayed.

Let us include an additional feature into the rolling dice. Let us include a switch to control the rolling and display of the dice.

You could choose to gate the clock of the dice or add the necessary inputs to the product terms to effect this design. If you were to stop after this step, then gating the clock would be a simpler choice, however, you will require the dice to roll during part D of the design; so we will choose to add product terms at this stage. This also results in a better engineering solution since gated clocks often cause problems in large systems, and it has been shown that synchronous systems are more reliable.

Screen 9.

| JEDEC File: | DICEL.JED          | Device: SCOLD                         | LOGIC PROGRAMMER |

|-------------|--------------------|---------------------------------------|------------------|

|             | LOGIC P            | JEDEC File Header Text                |                  |

|             | Copyrig            |                                       |                  |

|             | Copyrig<br>3065 Bo | Designer: Your Name                   |                  |

|             |                    | Company: Your Company                 |                  |

|             |                    | Part #:<br>Revision: 0.0              |                  |

|             | н                  | EPLD: 5COLO                           |                  |

|             |                    | Device code:                          |                  |

|             | Chang              | Comment: PART A: DICE ROLLING         |                  |

|             | Edit JE            | LB Version 3.0, Baseline 17x, 9/26/85 |                  |

|             |                    |                                       |                  |

|             | Progra             |                                       |                  |

|             | Verify             | Insert a 5COLO into the socket        |                  |

|             |                    | Strike any key when ready             |                  |

|             | Examin             |                                       |                  |

|             | E                  |                                       |                  |

|             |                    |                                       |                  |

Screen 10.

Since you already have a proven design of a rolling dice from part A, we shall use the Logic Builder and edit that design. You may wish to save the original design at this stage. You can do this by using the  $\langle F10 \rangle$  key in the Main Menu. Press  $\langle F10 \rangle$  and issue the following command before re-entering the iPLS menu:

COPY DICEL.\* DICELA.\*

The truth table is shown in Table 6.

Now you can use the iPLDS to design and program the device.

Go through the same steps to program the device as in Part A of the design example. Use the Logic builder, the Logic Optimizing Compiler, and the Logic Programmer respectively. The Logic Optimizing Compiler and the Logic Programmer steps are identical to the corresponding steps explained in part A of the design example. However, the Logic Builder will be used to edit the existing file, DICE1, to include the switch feature as follows:

Invoke the Logic Builder Menu from the iPLS main menu by pressing the  $\langle F3 \rangle$  key. Once you obtain the Logic Builder Configuration Menu, type in DICE1 as your input file name.

Use (Shift)(F3) to get the Inputs option and then add switch at pin #2 to it.

Inputs: CLOCK, SWITCH02 <Enter>

Now press  $\langle F2 \rangle$  to exit to the Logic Builder Main Menu and answer the prompts as given in Table 7.

All that is left to do now is to edit the four equations, IN1A, IN1B, IN1C, IN1D to add the SWITCH option to it. Edit the four equations as follows:

#### **Edit Function**

When you press the "Edit" function key,  $\langle F6 \rangle$ , while in the main menu, the edit menu is displayed on the left side of the screen as shown in Screen 11. If you wish to edit an EQN Primitive displayed on the screen, press  $\langle F6 \rangle$ . Then the equation is moved to the prompt line where it can be edited.

Hence, the Boolean expressions for this case would consider the situations of when the switch was ON as well as OFF. The Boolean equations would contain the expression for the switch as follows.

```

DICE1A = ((1A*/1B*/1C*/1D) + (1A**1B*/1C*/1D)

+ (1A*1B*1C*/1D)

+ (/1A*/1B*/1C*/1D))*/SWITCH

```

+((/1A\*1B\*/1C\*/1D)+(/1A\*1B\*1C\*/1D)

+ (/1A\*1B\*1C\*1D)

+ (/1A\*/1B\*/1C\*/1D))\*SWITCH

```

DICE1B = ((/1A*1B*/1C*/1D) + (1A*1B*/1C*/1D))

```

```

+(/1A*1B*1C*/1D)+(1A*1B*1C*/1D)

```

```

+ (/1A*1B*1C*1D))*/SWITCH

```

- +((1A\*/1B\*/1C\*/1D)

- +(/1A\*1B\*/1C\*/1D)+(1A\*1B\*/1C\*/1D)

+(/1A\*1B\*1C\*/1D)

+(1A\*1B\*1C\*/1D))\*SWITCH

DICE1C = ((/1A\*1B\*1C\*/1D) +(1A\*1B\*1C\*/1D) +(/1A\*1B\*1C\*1D))\*/SWITCH +((1A\*1B\*1C\*/1D)+(/1A\*1B\*1C\*/1D) +(1A\*1B\*1C\*/1D))\*SWITCH

DICE1D = (/1A\*1B\*1C\*1D)\*/SWITCH +(1A\*1B\*1C\*/1D)\*SWITCH

The equation primitive must be displayed on the screen in order to edit that equation. In order to display the equation on the screen, use the "Find" command,  $\langle F5 \rangle$ , to find it.

The "Find" command prompts for a node name: then searches the design for that node and displays it. If the direction arrow points to the left, the primitive on the output side of the node is shown. If the direction arrow points to the right, the first primitive on the input side is shown.

After you have modified all four equations to include the SWITCH feature, return to the iPLDS main menu using the  $\langle F5 \rangle$  key and save the design using the  $\langle F6 \rangle$  key. You can verify your ADF file with the ADF file for part B given in Appendix D.

The file is ready to be compiled using the LOC, and the device is ready to be programmed using the LP.

The steps required to use the LOC and the LP are identical to the steps in part A.

Now the device that has been programmed is ready to be tested. At this stage in the design, you have completed part B of the design which is to add a switch to give the roll/no-roll option.

The programmed device can be tested as described in Appendix C.

Let us summarize before moving on to the next part of the design.

| · · · · · · · · · · · · · · · · · · · | 14 J 2 1 4 |                                                                                                                 |              |            |             |            |                             |              |                    |         |                 | ·. ·       | 111                   | <u> </u>           |

|---------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------|--------------|------------|-------------|------------|-----------------------------|--------------|--------------------|---------|-----------------|------------|-----------------------|--------------------|

|                                       | Input Stat | e                                                                                                               | •            |            |             |            |                             | 0            | utput              | State   | Э. <sup>с</sup> | · •        |                       |                    |

| SWITCH                                | 1A 1B      | 1C                                                                                                              | 1D           |            | 1 <b>A</b>  | 1 <b>B</b> | 1C                          | 1D           |                    | 1       | 1A              | 1 <b>B</b> | 1C                    | 1D                 |

|                                       | 12.5       | 1. 1. 1. 1.                                                                                                     |              |            |             | Valid      | state                       |              |                    | ÷.      |                 | Invalio    | state                 |                    |

|                                       |            |                                                                                                                 | RE           | MAIN       | IN TH       |            | ME STA                      | TE           |                    |         |                 |            |                       |                    |

| 0                                     | 1 0        | 0                                                                                                               | 0            |            | 1           | 0          | 0                           |              |                    |         |                 |            | 2 - 19 <sup>-</sup> 4 | s i wi             |

| 0                                     | 1 0<br>0 1 | 0                                                                                                               | 0            | ·          | 0           | 1          | 0                           | 0(1)<br>0(2) |                    |         |                 |            |                       |                    |

| 0                                     | 1 1        | 0                                                                                                               | 0            |            | 1           | 1          | 0                           | 0(3)         |                    |         |                 |            |                       |                    |

| 0                                     | 0 1        | 1                                                                                                               | 0            |            | 0           | 1,         | 1                           | 0(4)         |                    |         |                 | an ar      | - 1 - A               | 14.00              |

| 0                                     | 1 1        | 1                                                                                                               | 0            |            | 1<br>0      | 1          | 1<br>1                      | 0(5)         |                    |         |                 |            |                       | 5.00               |

| 0                                     | UI         |                                                                                                                 | I .          |            | •           | •          | •                           | 1(6)         |                    |         |                 |            |                       |                    |

|                                       | 0 0        |                                                                                                                 |              | ITROL      | THE         | INVAL      | ID STA                      | TES          | A                  |         | •               |            | •                     |                    |

| 0                                     | 0 0        | 1                                                                                                               | 0            |            |             |            | 5. L                        |              |                    |         | 0               | 0          | 0                     | 0                  |

| 0                                     | 0 0        | 0                                                                                                               | 1            |            |             |            | anto da serie<br>Carecteria |              |                    | ÷       | 0               | ŏ          | Ŭ.                    | ŏ                  |

| 0                                     | 1 0        | 0                                                                                                               | 1            |            |             |            |                             |              |                    |         | 0               | . 0        | 0                     | 0                  |

| 0                                     | 0 1        | 0                                                                                                               | 1            |            |             |            | e ye to                     |              |                    |         | 0.0             | 0 - 1      | 0                     | 0                  |

| 0                                     | 1 1        | 0                                                                                                               | 1            |            |             |            |                             |              |                    |         | 0.0             | 0°3<br>0   | 0 0<br>0              | 0                  |

| 0                                     | 1 1        | 1 I I I I I I I I I I I I I I I I I I I                                                                         | 1            |            |             |            |                             |              |                    |         | 0               | 0          | 0.                    | 0.                 |

| 0                                     | 0 0        | 0                                                                                                               | ò            | 4          |             |            |                             |              |                    |         | 1               | 0          | 0.0                   | 0(1)               |

|                                       |            | an di Sarah<br>Sarah Sarah                                                                                      | CHANC        | F TO       |             | IFXT       | VALID                       | STATE        | * 1 <sup>1</sup> 2 |         |                 | * · ·      |                       |                    |

|                                       |            |                                                                                                                 |              |            |             |            |                             |              |                    |         |                 |            |                       |                    |

|                                       | 1 0<br>0 1 | 0 0                                                                                                             | )(1)<br>)(2) |            | 0           | 1<br>1 :   | 0                           | 0(2)<br>0(3) |                    |         |                 |            | • • • •               |                    |

| land in the second                    | 1 1        | 0 0                                                                                                             | )(3)         | <b>.</b> . | 0           | 1          | 1                           | 0(4)         |                    |         |                 |            | с.<br>1915 г. М.      | 2                  |

| 1                                     | 0 1        | 1 0                                                                                                             | (4)          |            | ່ 1         | 1          | 1                           | 0(5)         |                    |         |                 |            |                       |                    |

| 1                                     | 1 1        | 1 0                                                                                                             | (5)          |            | 0           | 1          | 1                           | 1(6)         |                    |         |                 |            | 1.12                  | 1. da 4            |

| 1                                     | 0 1        | 1                                                                                                               | (6)          | ey., e e   | 1           | 0          | 0                           | 0(1)         |                    |         |                 |            |                       |                    |

| a na set                              |            | a series de la composición de la compos | CON          | ITROL      | THE         | INVAL      | ID STA                      | TES          |                    |         | an an<br>Tha th |            | un inven<br>ante inte | tan ar<br>Statesta |

| 1                                     | 0 0        | 1. 1. <b>1</b> . 1. 1.                                                                                          | 0            |            | ч. <u>с</u> |            |                             | 0            |                    |         | 0               | 0          | 0                     |                    |

| 1                                     | 1 0        | 1                                                                                                               | 0            |            | *<br>* 12   |            |                             | 0            | 2 (9))<br>1        | r, i    | 0               | 0          | .0                    |                    |

|                                       | 0 0        | 0                                                                                                               | 1            |            |             |            |                             | 0            |                    | 103 M - | 0               | 0          | 0                     | A. A.              |

|                                       | 1 0        | 0                                                                                                               | 1            |            |             |            |                             | 0<br>0       |                    | •       | 0               | 0          | 0                     |                    |

|                                       | 1 1        | 0                                                                                                               | 1            |            | ÷           |            |                             | 0            |                    |         | 0               | 0          | 0                     |                    |

| 1                                     | 0 0        | 1                                                                                                               | 1            |            |             |            |                             | Ō            |                    |         | 0               | Ō          | 0                     |                    |

| 1                                     | 1 0        | - 24 <b>1</b> - 51                                                                                              | 1            |            |             |            |                             | 0            |                    |         | 0               | 0          | 0                     |                    |

|                                       | 1 1        | 1                                                                                                               | 1            |            |             |            | -<br>1944 - 1947            | 0            |                    |         | 0               | 0          | 0                     |                    |

|                                       | 0 0        | 0                                                                                                               | 0            |            |             |            |                             | 1            | - 1 A              | 14.5    | 0               | 0          | 0(1)                  |                    |

Table 6. Truth Table for DICE1

Note: This part of the truth table is identical to Table 3.

We have briefly discussed the EPLD and the IPLDS family of parts. We have also defined the design problem. We have implemented the design using the state equations and the truth table, edited an existing design to add features, and actually programmed a device using the Logic Builder, Logic Optimizing Compiler, and the Logic Programmer.

Our logic in implementing the dice example is to use the LED pairs in outputs 1A, 1B, 1C, and 1D respectively as

| Та | b | le | 7 |  |

|----|---|----|---|--|

|    |   |    |   |  |

| Prompts                                   | User Entry             |

|-------------------------------------------|------------------------|

| Select a primitive for switch@2 to drive: | INP <enter></enter>    |

| Out:                                      | SWITCH <enter></enter> |

| Select a primitive for switch to drive:   | EQN <enter></enter>    |

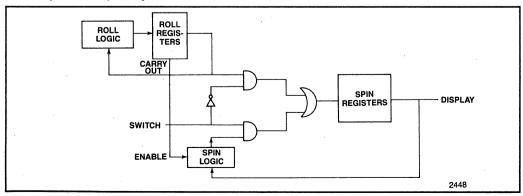

shown in Figure 8. These LEDs are lit up to generate numbers between 1 and 6 inclusive. We are using a D-TYPE FLIP-FLOP to implement the truth table. The clock is a free running clock. A push button switch is also supplied to give the roll/no-roll option. Whenever the switch is ON, the LEDs roll, and when the switch is OFF, the LEDs display a number between 1 and 6, as long as the clock is supplied to the device.

After seeing the dice roll and display a number, you can either quit or move onto parts C, D and E of the design process. The following three parts describe a versatile use of the EPLD concept.

### PART C

We are using an EPLD 5C060 which is a 24 pin, 600 gate device. It has four dedicated input pins and 16 input/output pins. Up to this point you have used only one input pin which is the switch and only four input/output pins for the four LEDs 1A, 1B, 1C, 1D.

Part C of the design is to include a second dice with the first dice. This is a step towards real-world application since dice are usually rolled in pairs. At the end of this section, you will have a pair of dice rolling and displaying a pair of numbers. All the conditions and truth tables and Boolean expressions that were designed for part B, hold good for DICE1. The equations for DICE2 would change slightly as explained below.

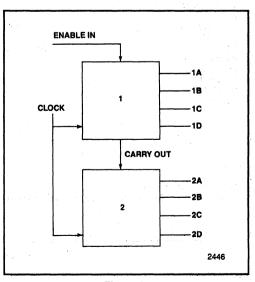

You have designed a 6 state counter and can define a carry out (fortunately you can use state 6 and do not require extra logic). You can use the carry out as an enable input to form two cascaded counters.

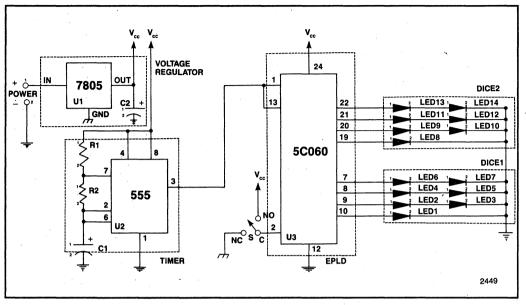

The carry out of 1D is used as an enable input to DICE2. Hence, 1D performs the same function as the push button switch performed in dice 1. Therefore, whenever 1D is enabled or logic high, DICE2 is enabled and rolls a number. DICE2 displays the number when 1D is disabled or logic is low. This configuration is shown in Figure 9.

#### Screen 11.

| Table | e 8. |

|-------|------|

|-------|------|

| PROMPTS                                                                  | USER ENTRY            |

|--------------------------------------------------------------------------|-----------------------|

| Find:                                                                    | IN1D <enter></enter>  |

| (Now use the <cursor left=""> key to obtain the EQN Primitive.)</cursor> |                       |

| Edit:                                                                    |                       |

| IN1D = (/1A*1B*1C*1D)*/SWITCH+(1A*1B*1C*/1D)*SWITCH; <enter></enter>     |                       |

| Find:                                                                    | INLC <enter></enter>  |

| (Now use the <cursor left=""> key to obtain the EQN Primitive.)</cursor> |                       |

| Edit:                                                                    |                       |

| INIC = ((/la*lB*lc*/ld)+(la*lB*lc*/ld)+(/la*lB*lc*ld))*/SWITCH           |                       |

| +((]TV*JB*\JC*\TD)+(\TV*JB*JC*\TD)+(]TV*JB*JC*\TD))*2M1LCH!              | and the second second |

| <pre><enter></enter></pre>                                               |                       |

| Find:                                                                    | IN18 <enter></enter>  |

| (Now use the <cursor left=""> key to obtain the EQN Primitive.)</cursor> | IN3B Chicer>          |

| Edit:                                                                    |                       |

| IN1B = ((/la*lB*/lC*/lD)+(la*lB*/lC*/lD)+(/la*lB*lC*lD)+(la*lB*lC*/lD)   | the second second     |

| +(/la*lB*lC*lD))*/SWITCH                                                 | the second second     |

| +((lA*/lB*/lC*/lD)+(/lA*lB*/lC*/lD)+(lA*lB*/lC*/lD)+                     |                       |

| (/lA*lB*lC*/lD)+(lA*lB*lC*/lD))*SWITCH; <enter></enter>                  | • • • • • • • • •     |

|                                                                          |                       |

| Find:                                                                    | INLA <enter></enter>  |

| (Now use the <cursor left=""> key to obtain the E@N Primitive.)</cursor> |                       |

| Edit:                                                                    |                       |

| IN1A=((lA*/lB*/lC*/l))+(lA*lB*/lC*/lD)+(lA*lB*lC*/lD)+                   | }                     |

| (/lA*/lB*/lC*/lD))*/2MILCH+((\lA*lB*\lC*/lD)+(\lA*lB*fC*\lD)             |                       |

| +(/lA*lB*lC*lD)+(/lA*/lB*/lC*/lD))*SWITCH; <enter></enter>               |                       |

The two conditions obtained are as follows:

When power is ON and 1D is enabled, DICE2 will roll.

When power is ON and 1D is disabled, DICE2 will display.

For DICE1, the logic conditions remain the same as in part A. Just as you used the switch to enable and disable

Figure 9.

DICE1, you will use the switch as well as the output of LED 1D to enable and disable DICE2; because the number on DICE2 is a function of both the switch and the present state of LED 1D, as explained above.

Now write down the truth table since the state diagrams can easily be inferred from the truth table. Please note that the truth table is identical to the one for DICE1 except for the switch input. For DICE2, you will have the combination of the switch and the 1D, as shown in Table 9.

The Boolean expressions for part C will consider the situation when the switch is ON as well as OFF and also 1D enabled or disabled respectively. The Boolean equations will contain the expression for the switch and LED 1D, as shown below.

- DICE2A = ((2A\*/2B\*/2C\*/2D) + (2A\*2B\*/2C\*/2D) +(2A\*2B\*2C\*/2D) + (/2A\*/2B\*/2C\*/2D)) \*(/SWITCH\*/1D) + ((/2A\*2B\*/2C\*/2D) + (/2A\*2B\*2C\*/2D) + (/2A\*2B\*2C\*2D) + (/2A\*2B\*2C\*/2D)) \*(SWITCH\*1D)

- DICE2C = ((/2A\*2B\*2C\*/2D) + (2A\*2B\*2C\*/2D) + (/2A\*2B\*2C\*2D))\*(/SWITCH\*/1D) + ((2A\*2B\*2C\*2D)) + (/2A\*2B\*2C\*/2D) + (/2A\*2B\*2C\*/2D) + (2A\*2B\*2C\*/2D)) \*(SWITCH\*1D)

DICE2D = (/2A\*2B\*2C\*2D)\*(/SWITCH\*/1D) +(2A\*2B\*2C\*/2D)\*(SWITCH\*1D)

Now you can use the iPLDS to program and test the device as explained in appendix C. At this stage in design, you have completed part C of the design which is to add a second DICE to the first one giving the the roll/no-roll option.

In part C of the design process, you have used one dedicated input which is the switch, and a total of eight output pins for the two pairs of LEDs, 1A, 1B, 1C, 1D and 2A, 2B, 2C, 2D respectively. You have also used the RORF primitive, since the design logic was the same for DICE2 as it was for DICE1. This leaves 3 dedicated inputs and 8 I/O pins on the 5C060 device.