# iSBC® 80/10B SINGLE BOARD COMPUTER

8080A CPU Used as Central Processing Unit

Intal

- One iSBX™ Bus Connector for iSBX™ MULTIMODULE™ Board Expansion

- IK Byte of Read/Write Memory with Sockets for Expansion up to 4K Bytes

- Sockets for up to 16K Bytes of Read Only Memory

- 48 Programmable Parallel I/O Lines with Sockets for Interchangeable Line Drivers and Terminators

- Programmable Synchronous/ Asynchronous Communications Interface with Selectable RS232C or Teletypewriter Compatibility

- Single Level Interrupt with 11 Interrupt. Sources

- Auxiliary Power Bus and Power-Fail Interrupt Control Logic for RAM Battery Backup

- 1.04 Millisecond Interval Timer

- Limited Master MULTIBUS® Interface

The Intel iSBC 80/10B board is a member of Intel's complete line of OEM microcomputer systems which take full advantage of Intel's LSI technology to provide economical, self-contained computer-based solutions for OEM applications. The iSBC 80/10B board is a complete computer system on a single 6.75 x 12.00-inch printed circuit card. The CPU, system clock, iSBX bus interface, read/write memory, read only memory sockets, I/O ports and drivers, serial communications interface, bus control logic, and drivers all reside on the board.

280217-1

# FUNCTIONAL DESCRIPTION

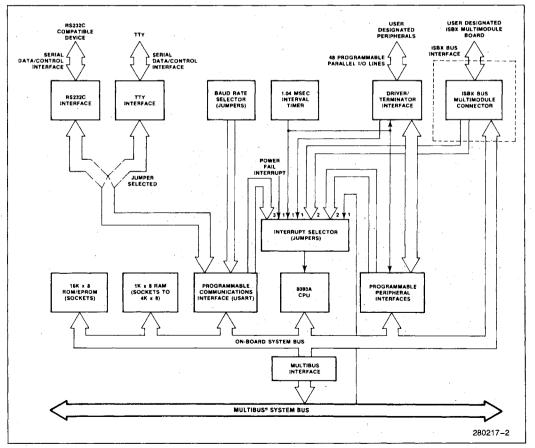

Intel's powerful 8-bit n-channel MOS 8080A CPU, fabricated on a single LSI chip, is the central processor for the iSBC 80/10B board. The 8080A contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs, providing both single and double precision operators. A block diagram of ISBC 80/10B board functional components is shown in Figure 1.

# **iSBX™** Bus MULTIMODULE™ Board Expansion

The new iSBX bus interface brings an entirely new dimension to system design offering incremental onboard expansion with small iSBX boards. One iSBX bus connector interface is provided to accomplish plug-in expansion with any iSBX MULTIMOD- ULE board. iSBX boards are available to provide expansion equivalent to the I/O available on the iSBC 80/10B board or the user may configure entirely new functionality such as math directly on-board. The iSBX 350 programmable I/O MULTIMODULE board provides 24 I/O lines using an 8255A programmable peripheral interface. Therefore, the iSBX 350 module together with the iSBC 80/10B board may offer 72 lines of programmable I/O. Alternately, a serial port may be added using the iSBX 351 serial I/O multimodule board or math may be configured on-board with the iSBX 332 floating point math MUL-TIMODULE board.

The iSBX board is a logical extension of the onboard programmable I/O and is accessed by the iSBC 80/10B single board computer as common I/O port locations. The iSBX board is coupled directly to the 8080A CPU and therefore becomes an integral element of the iSBC 80/10B single board computer providing optimum performance.

Figure 1. iSBC<sup>®</sup> 80/10B Single Board Computer Block Diagram

## Memory Addressing

The 8080A has a 16-bit program counter which allows direct addressing of up to 64K bytes of memory. An external stack, located within any portion of read/write memory, may be used as a last-in/firstout storage area for the contents of the program counter, flags, accumulator, and all of the six general purpose registers. A 16-bit stack pointer controls the addressing of this external stack. This stack provides subroutine nesting bounded only by memory size.

## **Memory Capacity**

The iSBC 80/10B board contains 1K bytes of read/ write static memory. In addition, sockets for up to 4K bytes of RAM memory are provided on board. Read/ write memory may be added in 1K byte increments using two 1K x 4 Intel 2114A-5 static RAMs. All onboard RAM read and write operations are performed at maximum processor speed. Sockets for up to 16K bytes of nonvolatile read-only-memory are provided on the board. Read-only-memory may be added in 1K byte increments up to 4K bytes (using Intel 2708 or 2758); in 2K byte increments up to 8K bytes (using Intel 2716); or in 4K byte increments up to 16K bytes (using Intel 2732). All on-board ROM or EPROM read operations are performed at maximum processor speed.

# **Parallel I/O Interface**

The iSBC 80/10B board contains 48 programmable parallel I/O lines implemented using two Intel 8255A programmable peripheral interfaces. The system software is used to configure the I/O lines in any combination of unidirectional input/output, and bidirectional ports indicated in Table 1. Therefore, the I/O interface may be customized to meet specific peripheral requirements. In order to take full advantage of the large number of possible I/O configurations, sockets are provided for interchangeable I/O line drivers and terminators. Hence, the flexibility of the I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the reguired sink current, polarity, and drive/termination characteristics for each application. The 48 programmable I/O lines and signal ground lines are brought out to two 50-pin edge connectors that mate with flat cable or round cable.

# Serial I/O Interface

A programmable communications interface using the Intel 8251A Universal Synchronous/Asynchronous Receiver/Transmitter (USART) is contained on the board. A jumper selectable baud rate generator provides the USART with all common communications frequencies. The USART can be programmed

|      |                | Mode of Operation |                      |               |                      |        |      |  |  |

|------|----------------|-------------------|----------------------|---------------|----------------------|--------|------|--|--|

|      | Lines<br>(Qty) |                   | Unidired             | Bidirectional | Control              |        |      |  |  |

| Port |                | Input             |                      |               |                      | Output |      |  |  |

|      |                | Unlatched         | Latched &<br>Strobed | Latched       | Latched &<br>Strobed |        |      |  |  |

| 1    | 8              | X                 | X                    | X             | Х                    | x      |      |  |  |

| 2    | 8              | x                 | x                    | х             | x                    |        |      |  |  |

| 3    | 8              | X                 |                      | X             |                      |        | χ(1) |  |  |

| 4    | 8              | X                 |                      | X             |                      |        |      |  |  |

| 5    | 8              | X                 |                      | х             |                      |        |      |  |  |

| 6    | 4              | X                 |                      | X             |                      |        |      |  |  |

|      | 4              | x                 |                      | х             |                      |        |      |  |  |

### Table 1. Input/Output Port Modes of Operation

#### NOTE:

1. Port 3 must be used as a control port when either port 1 or port 2 are used as a latched and strobed input or a latched and strobed output port or port 1 is used as a bidirectional port.

by the system software to select the desired synchronous or asynchronous serial data transmission technique (including IBM Bi-Sync). The mode of operation (i.e., synchronous or asynchronous), data format, control character format and parity are all under program control. The 8251A provides full duplex, double-buffered transmit and receive capability. Parity, overrun, and framing error detection are all incorporated in the USART. The inclusion of jumper selectable TTY or RS232C compatible interfaces on the board, in conjunction with the USART, provides a direct interface to teletypes, CRTs, RS232C compatible cassettes, and asynchronous and synchronous modems. The RS232C or TTY command lines, serial data lines, and signal ground lines are brought out to a 26-pin edge connector that mates with RS232C compatible flat or round cable.

### Interrupt Capability

Interrupt requests may originate from 11 sources. Two jumper selectable interrupt requests can be automatically generated by the programmable peripheral interface when a byte of information is ready to be transferred to the CPU (i.e., input buffer is full) or a byte of information has been transferred to a peripheral device (i.e., output buffer is empty). Three jumper selectable interrupt requests can be automatically generated by the USART when a character is ready to be transferred to the CPU (i.e., receive channel buffer is full), a character is ready to be transmitted (i.e., the USART is ready to accept a character from the CPU), or when the transmitter is empty (i.e., the USART has no character to transmit). These five interrupt request lines are all maskable under program control. Two interrupt request lines may be interfaced directly to user designated peripheral devices; one via the MULTIBUS system bus and the other via the I/O edge connector. One jumper selectable interrupt request may be interfaced to the power-fail interrupt control logic. One jumper selectable interrupt request may originate from the interval timer. Two general purpose interrupt requests are jumper selectable from the iSBX interface. These two signals permit a user installed MULTIMODULE board to interrupt to 8080A CPU. The eleven interrupt request lines share a single CPU interrupt level. When an interrupt request is recognized, a restart instruction (RESTART 7) is generated. The processor responds by suspending program execution and executing a user defined interrupt service routine originating at location 3816.

### Power-Fail Control

A power-fail interrupt may be detected through the AC-low signal generated by the power supply. This signal may be configured to interrupt the 8080A CPU to initiate an orderly power down instruction sequence.

### Interval Timer

A 1.04 millisecond timer is available for interval interrupts or as a clock output to the parallel I/O connector. The timer output is jumper selectable to the programmable parallel interface, the parallel I/O connector (J1), or directly to the 8080A CPU.

### MULTIBUS® System Expansion Capabilities

Memory and I/O capacity may be expanded and additional functions added using Intel MULTIBUS™ system compatible expansion boards. Memory may be expanded to 65,536 bytes by adding user specified combinations of RAM boards. EPROM boards. or combination boards. Input/output capacity may be increased by adding digital 1/O and analog I/O expansion boards. In addition, the iSBC 80/10B board performs as a limited bus master in that it must occupy the lowest priority when used with other MULTIBUS masters. The bus master may take control of the MULTIBUS system bus by halting the iSBC 80/10B board program execution. Mass storage capability may be achieved by adding single density diskette, double density diskette, or hard disk controllers. Modular expandable backplanes and cardcages are available to support multiboard systems.

### SPECIFICATIONS

### Word Size

Instruction: 8, 16, or 24 bits Data: 8 bits

### Cycle Time

Basic Instruction Cycle: 1.95 µs

#### NOTE:

Basic instruction cycle is defined as the fastest instruction (i.e., four clock cycles).

# **Memory Addressing**

### On-Board ROM/EPROM

0-0FFF using 2708, 2758 0-1FFF using 2716 0-3FFF using 2732

### **On-Board RAM**

3C00-3FFF with no RAM expansion 3000-3FFF with 2114A-5 expansion

NOTE:

All RAM configurations are automatically moved up to a base address of 4XXX when configuring EPROM for 2732.

# **Memory Capacity**

### **On-Board ROM/EPROM**

16K bytes (sockets only)

### On-Board RAM

1K byte with user expansion in 1K increments to 4K byte using Intel 2114A-5 RAMs.

### **Off-Board Expansion**

Up to 64K bytes using user specified combinations of RAM, ROM, and EPROM.

# I/O Addressing

### **On-Board Programmable I/O**

| Device           | I/O<br>Address |

|------------------|----------------|

| 8255 No. 1       |                |

| Port A           | E4             |

| Port B           | E5             |

| Port C           | E6             |

| Control          | E7             |

| 8255 No. 2       |                |

| Port A           | E8             |

| Port B           | E9             |

| Port C           | EA             |

| Control          | EB             |

| 8251A            |                |

| Data             | EC             |

| Control          | ED             |

| iSBX Multimodule | ş              |

| MCS0             | F0-F7          |

| MCS1             | F8-FF          |

|                                        | Baud Rate (Hz) |                                     |      |  |  |

|----------------------------------------|----------------|-------------------------------------|------|--|--|

| Frequency (kHz)<br>(Jumper Selectable) | Synchronous    | Asynchronous<br>(Program Selectable |      |  |  |

|                                        |                | ÷ 16                                | ÷64  |  |  |

| 307.2                                  | _              | 19200                               | 4800 |  |  |

| 153.6                                  |                | 9600                                | 2400 |  |  |

| 76.8                                   |                | 4800                                | 1200 |  |  |

| 38.4                                   | 38400          | 2400                                | 600  |  |  |

| 19.2                                   | 19200          | 1200                                | 300  |  |  |

| 9.6                                    | 9600           | 600                                 | 150  |  |  |

| 6.98                                   | 6980           |                                     | 110  |  |  |

| 4.8                                    | 4800           | 300                                 | 75   |  |  |

### Connectors

| Interface        | Double-Sided<br>Pins (Qty) | Centers<br>(in.) | Mating Connectors            |  |  |

|------------------|----------------------------|------------------|------------------------------|--|--|

| MULTIBUS System  | 86                         | 0.156            | Viking 2KH43/9AMK12 Wire-wra |  |  |

| iSBX Bus         | 36                         | 0.1              | iSBX 960-5                   |  |  |

| Parallel I/O (2) | 50                         | 0.1              | 3M 3415-000 Flat             |  |  |

| Serial I/O       | 26                         | 0,1              | AMP 87194-6 Flat             |  |  |

# I/O Capacity

| Parallel:    | 48              | progra  | mmab     | le lines    |

|--------------|-----------------|---------|----------|-------------|

| Serial:      | 11              | transmi | t, 1 ree | ceive       |

| MULTIMODULE: | 1 iSBX<br>Board |         | Bus      | MULTIMODULE |

# **Serial Communications Characteristics**

- Synchronous: 5–8 bit characters; internal or external character synchronization; automatic sync insertion

- Asynchronous: 5–8 bit characters; break character generation; 1, 1<sup>1</sup>/<sub>2</sub>, or 2 stop bits; false start bit detectors

### Interrupts

Single-level with on-board logic that automatically vectors the processor to location 38H using a restart instruction (RESTART 7). Interrupt requests may originate from user specified I/O (2); the programmable peripheral interface (2); the iSBX MULTIMOD-ULE board (2); the programmable communications interface (3); the power fail interrupt (1); or the interval timer (1).

# Interfaces

| MULTIBUS:           | All signals TTL compatible                                                |

|---------------------|---------------------------------------------------------------------------|

| iSBX Bus:           | All signals TTL compatible                                                |

| Parallel I/O:       | All signals TTL compatible                                                |

| Serial I/O:         | RS232C or a 20 mil current<br>loop TTY interface (jumper se-<br>lectable) |

| Interrupt Requests: | All TTL compatible (active-low)                                           |

# Clocks

System Clock: 2.048 MHz  $\pm$  0.1% Interval Timer: 1.042 ms  $\pm$  0.1% (959.5 Hz)

# **Physical Characteristics**

| Width:  | 12.00 in (30.48 cm) |

|---------|---------------------|

| Height: | 6.75 in. (17.15 cm) |

| Depth:  | 0.05 in. (1.27 cm)  |

| Weight: | 14 oz. (397.3 gm)   |

### **Electrical Characteristics**

### **DC Power Requirements**

| Voltage                                                                                          | Without                   | With 2708            | With 2758, 2716,             | Power Down Requirements    |

|--------------------------------------------------------------------------------------------------|---------------------------|----------------------|------------------------------|----------------------------|

|                                                                                                  | EPROM <sup>(1)</sup>      | EPROM <sup>(2)</sup> | or 2732 EPROM <sup>(3)</sup> | (RAM and Support Circuit)  |

| $V_{CC} = +5V \pm 5\% \\ V_{DD} = +12V \pm 5\% \\ V_{BB} = -5V \pm 5\% \\ V_{AA} = -12V \pm 5\%$ | $I_{CC} = 2.0A(4)$        | 3.1A                 | 3.46A                        | 84 mA + 140 mA/K (2114A-5) |

|                                                                                                  | $I_{DD} = 150 \text{ mA}$ | 400 mA               | 150 mA                       | Not Required               |

|                                                                                                  | $I_{BB} = 2 \text{ mA}$   | 200 mA               | 2 mA                         | Not Required               |

|                                                                                                  | $I_{AA} = 175 \text{ mA}$ | 175 mA               | 175 mA                       | Not Required               |

### NOTES:

1. Does not include power required for optional ROM/EPROM, I/O drivers, or I/O terminators.

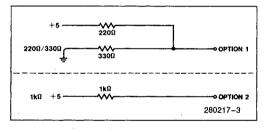

With four Intel 2708 EPROMS and 220Ω/330Ω for terminators, installed for 48 input lines. All terminator inputs low.

Same as #2 except with four 2758s, 2716s, or 2732s installed.

4. I<sub>CC</sub> shown without RAM supply current. For 2114-5 add 140 mA per K byte to a maximum of 560 mA.

# intel

# **Line Drivers and Terminators**

I/O Drivers: The following line drivers and terminators are all compatible with the I/O driver sockets on the iSBC 80/10B Board:

| Driver | Characteristic | Sink Current (mA) |

|--------|----------------|-------------------|

| 7438   | I, OC          | 48                |

| 7437   | 1              | 48                |

| 7432   | NI             | 16                |

| 7426   | I, OC          | 16                |

| 7409   | NI, OC         | 16                |

| 7408   | NI             | 16                |

| 7403   | I, OC          | 16                |

| 7400   | I              | 16                |

### NOTE:

I-inverting, NI-non-inverting, OC-open collector.

Port 1 has 25 nA totem pole drivers and 1  $k\Omega$  terminators.

I/O Terminators: 220 $\Omega$ /330 $\Omega$  divider or 1 k $\Omega$  pull up.

# **MULTIBUS®** Drivers

| Function | Characteristic | Sink Current (mA) |

|----------|----------------|-------------------|

| Data     | Tri-State      | 25                |

| Address  | Tri-State      | 25                |

| Commands | Tri-State      | 25                |

# **Environmental Characteristics**

Operating Temperature: 0°C to 55°C

# Equipment Supplied

iSBC 80/10B Single Board Computer iSBC 80/10B Schematics

# **Reference Manual**

9803119-01— iSBC 80/10B Single Board Computer Hardware Reference Manual (NOT SUPPLIED).

Manuals may be ordered from any Intel sales representative, distributor office or from Intel Literature Department, 3065 Bowers Avenue, Santa Clara, California 95051.

# **ORDERING INFORMATION**

Part Number Description

iSBC80/10B Single Board Computer