# 82786 Graphics Coprocessor User's Manual

Order Number: 231933-003

### **LITERATURE**

To order Intel Literature write or call:

INTEL LITERATURE SALES P.O. BOX 58130 SANTA CLARA, CA 95052-8130 TOLL FREE NUMBER: (800) 548-4725'

### 1988 HANDBOOKS

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| TITLE                                                                                                                             | LITERATURE<br>ORDER NUMBER |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| COMPLETE SET OF 8 HANDBOOKS Save \$50.00 off the retail price of \$175.00. (Price applicable to U.S. and Canadian shipments only) | 231003                     |

| AUTOMOTIVE HANDBOOK, 1200 pages (Not included in handbook set)                                                                    | 231792                     |

| COMPONENTS QUALITY/RELIABILITY HANDBOOK, 288 pages (Available in July)                                                            | 210997                     |

| EMBEDDED CONTROLLER HANDBOOK, 2016 pages (2 volume set)                                                                           | 210918                     |

| MEMORY COMPONENT'S HANDBOOK, 528 pages                                                                                            | 210830                     |

| MEMORY COMPONENTS HANDBOOK SUPPLEMENT, 256 pages (Available in July)                                                              | 230663                     |

| MICROCOMMUNICATIONS HANDBOOK, 1648 pages                                                                                          | 231658                     |

| MICROPROCESSOR AND PERIPHERAL HANDBOOK, 2224 pages (2 volume set)                                                                 | 230843                     |

| MILITARY HANDBOOK, 1776 pages<br>(Not included in handbook set)                                                                   | 210461                     |

| OEM BOARDS AND SYSTEMS HANDBOOK, 880 pages                                                                                        | 280407                     |

| PROGRAMMABLE LOGIC HANDBOOK, 448 pages                                                                                            | 296083                     |

| SYSTEMS QUALITY/RELIABILITY HANDBOOK, 160 pages                                                                                   | 231762                     |

| PRODUCT GUIDE (No charge) Overview of Intel's complete product lines                                                              | 210846                     |

| DEVELOPMENT TOOLS CATALOG (No charge)                                                                                             | 280199                     |

| INTEL PACKAGING OUTLINES AND DIMENSIONS (No charge) Packaging types, number of leads, etc.                                        | 231369                     |

| LITERATURE PRICE LIST (No charge) List of Intel Literature                                                                        | 210620                     |

For U.S. and Canadian literature pricing, call or write Intel Literature Sales. In Europe and other international locations, please contact your local Intel Sales Office or Distributor for literature prices.

<sup>\*</sup>Good in the U.S. and Canada.

## Get Intel's Latest Technical Literature, Automatically!

### **Exclusive, Intel Literature Update Service**

Take advantage of Intel's year-long, low cost Literature Update Service and you will receive your first package of information followed by automatic quarterly updates on all the latest product and service news from Intel.

### Choose one or all five product categories update

Each product category update listed below covers in depth, all the latest Handbooks, Data Sheets, Application Notes, Reliability Reports, Errata Reports, Article Reprints, Promotional Offers, Brochures, Benchmark Reports, Technical Papers and much more.

### 1. Microprocessors =

Product line handbooks on Microprocessors, Embedded Controllers and Component Quality/Reliability, *Plus*, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$70.00 Order Number: **555110**

### 2. Peripherals

Product line handbooks on Peripherals, Microcommunications, Embedded Controllers, and Component Quality/Reliability, *Plus*, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$50.00 Order Number: **555111**

#### 3. Memories

Product line handbooks on Memory Components, Programmable Logic and Components Quality/Reliability, *Plus*, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$50.00 Order Number: **555112**

### 4. OEM Boards and Systems

Product line handbooks on OEM Boards & Systems, Systems Quality/Reliability, *Plus*, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$50.00 Order Number: **555113**

#### 5. Software

Product line handbooks on Systems Quality/Reliability, Development Tools Catalog, Plus, the Product Guide, Literature Guide, Packaging Information and 3 quarterly updates. \$35.00 Order Number: **555114**

To subscribe, rush the Literature Order Form in this handbook, or call today, toll free (800) 548-4725.\*

Subscribe by March 31, 1988 and receive a valuable free gift.

The charge for this service covers our printing, postage and handling cost only.

Please note: Product manuals are not included in this offer.

Customers outside the U.S. and Canada should order directly from the U.S.

Offer expires 12/31/88.

\*Good in the U.S. and Canada.

### LITERATURE SALES ORDER FORM

| NAME:                                                                                                                    |                                       |                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------|

| COMPANY:                                                                                                                 |                                       | · · · · · · · · · · · · · · · · · · ·                                                  |

| ADDRESS:                                                                                                                 |                                       |                                                                                        |

| CITY:                                                                                                                    | STATE: _                              | ZIP:                                                                                   |

| COUNTRY:                                                                                                                 |                                       |                                                                                        |

| PHONE NO.: ( )                                                                                                           |                                       |                                                                                        |

| ORDER NO.                                                                                                                | TITLE                                 | QTY. PRICE TOTAL                                                                       |

|                                                                                                                          |                                       | ×=                                                                                     |

|                                                                                                                          |                                       | X=                                                                                     |

|                                                                                                                          |                                       | ×=                                                                                     |

|                                                                                                                          | · · · · · · · · · · · · · · · · · · · | ×=                                                                                     |

|                                                                                                                          |                                       | ×=_                                                                                    |

|                                                                                                                          |                                       | =                                                                                      |

|                                                                                                                          |                                       | =                                                                                      |

|                                                                                                                          |                                       | X=                                                                                     |

|                                                                                                                          |                                       | ×=                                                                                     |

|                                                                                                                          |                                       | X=                                                                                     |

|                                                                                                                          |                                       | Subtotal                                                                               |

|                                                                                                                          |                                       | Must Add Your<br>Local Sales Tax                                                       |

| Must add appropriate postage to subto (10% U.S. and Canada, 20% all other).                                              |                                       | Postage                                                                                |

|                                                                                                                          |                                       | Total                                                                                  |

| Pay by Visa, MasterCard, American Exp<br>Intel Literature Sales. Allow 2-4 weeks fo<br>□ Visa □ MasterCard □ American Ex | or delivery.                          |                                                                                        |

| Account No.                                                                                                              |                                       |                                                                                        |

| Signature                                                                                                                |                                       |                                                                                        |

| Mail To: Intel Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130                                                |                                       | s outside the U.S. and Canada<br>Intel Sales Office or Distributor<br>ntel literature. |

Call Toll Free: (800) 548-4725 for phone orders

Prices good until 12/31/88.

Source HB

### **CUSTOMER SUPPORT**

### CUSTOMER SUPPORT

Customer Support is Intel's complete support service that provides Intel customers with hardware support, software support, customer training, and consulting services. For more information contact your local sales offices.

After a customer purchases any system hardware or software product, service and support become major factors in determining whether that product will continue to meet a customer's expectations. Such support requires an international support organization and a breadth of programs to meet a variety of customer needs. As you might expect, Intel's customer support is quite extensive. It includes factory repair services and worldwide field service offices providing hardware repair services, software support services, customer training classes, and consulting services.

#### HARDWARE SUPPORT SERVICES

Intel is committed to providing an international service support package through a wide variety of service offerings available from Intel Hardware Support.

### SOFTWARE SUPPORT SERVICES

Intel's software support consists of two levels of contracts. Standard support includes TIPS (Technical Information Phone Service), updates and subscription service (product-specific troubleshooting guides and COMMENTS Magazine). Basic support includes updates and the subscription service. Contracts are sold in environments which represent product groupings (i.e., iRMX® environment).

### CONSULTING SERVICES

Intel provides field systems engineering services for any phase of your development or support effort. You can use our systems engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training, and customizing or tailoring an Intel product to providing technical and management consulting. Systems Engineers are well versed in technical areas such as microcommunications, real-time applications, embedded microcontrollers, and network services. You know your application needs; we know our products. Working together we can help you get a successful product to market in the least possible time.

#### CUSTOMER TRAINING

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to ten days a limited number of individuals learn more in a single workshop than in weeks of self-study. For optimum convenience, workshops are scheduled regularly at Training Centers worldwide or we can take our workshops to you for on-site instruction. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, BITBUS<sup>TM</sup> and LAN applications.

82786 GRAPHICS COPROCESSOR USER'S MANUAL Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, ETOX, FASTPATH, Genius, i, Î, ICE, ICEL, ICS, IDBP, IDIS, I²ICE, ILBX, i<sub>m</sub>, iMDDX, iMMX, Inboard, Insite, Intel, Intel, Intel376, Intel386, Intel486, intelBOS, Intel Certified, Intelevision, inteligent Identifier, inteligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMK, iRMX, ISBC, ISBX, ISDM, ISXM, KEPROM, Library Manager, MAPNET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, OTP, PC BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Erase, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, ISBC, ISBX, ISXM, MCS, or UPI and a numerical suffix, 4-SITE, 376, 386, 486.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130

**©INTEL CORPORATION 1988**

| CHAPTER 1                                            | Page |

|------------------------------------------------------|------|

| 82786 OVERVIEW                                       |      |

| 1.0 Revision Information                             | 1-2  |

| 1.1 Architecture                                     | 1-3  |

| 1.1.1 Graphics Processor (GP)                        | 1-3  |

| 1.1.2 Display Processor/CRT Controller (DP)          | 1-3  |

| 1.1.3 Display Processor (DP) Master and Slave Modes  | 1-4  |

| 1.1.4 Bus Interface Unit (BIU)                       | 1-4  |

| 1.1.5 Memory Structure                               | 1-5  |

| 1.1.6 Memory Access and Arbitration                  | 1-5  |

| 1.1.7 Master and Slave Memory Access Interfaces      | 1-5  |

| 1.1.7.1 Master Mode Interface                        | 1-6  |

| 1.1.7.2 Slave Interface                              | 1-6  |

| 1.1.8 Internal Registers                             | 1-6  |

| 1.2 System Configurations                            | 1-6  |

|                                                      |      |

| CHAPTER 2                                            |      |

| GRAPHICS PROCESSOR OVERVIEW                          |      |

| 2.1 Graphics Concepts                                | 2-1  |

| 2.1.1 Bitmaps                                        | 2-1  |

| 2.1.2 Bitmap Coordinates                             | 2-2  |

| 2.1.3 Pixels                                         | 2-2  |

| 2.1.4 Calculating the Effective Address (EA)         | 2-3  |

| 2.1.5 Windows                                        | 2-4  |

| 2.2 Graphics Processor (GP) Registers                | 2-4  |

| 2.2.1 Internal Graphics Processor (GP) Registers     | 2-4  |

| 2.2.1.1 Graphics Processor Status Register (GSTAT)   | 2-5  |

| 2.2.1.2 Graphics Processor Instruction Pointer       | 2-5  |

| 2.2.2 Graphics Processor (GP) Control Registers      | 2-6  |

| 2.2.3 Graphics Processor (GP) Context Registers      | 2-7  |

| 2.3 Command Execution and Format                     | 2-8  |

| 2.3.1 Graphics Processor Command Block (GCMB) Format | 2-9  |

| 2.3.2 Poll State                                     | 2-10 |

| 2.3.3 RESET and Initialization                       | 2-10 |

| 2.3.4 Exception Handling                             |      |

| 2.4 Graphics Processor (GP) Commands                 |      |

| 2.5 Nondrawing Commands                              |      |

| 2.6 Drawing Control Commands                         |      |

| 2.6.1 Attributes Associated with Drawing Commands    |      |

| 2.6.2 Color Bit Mask                                 |      |

| 2.6.3 Logical Operations                             |      |

| 2.6.4 Clipping Rectangle                             |      |

| 2.6.5 Pick Mode                                      |      |

|                                                             | Page |

|-------------------------------------------------------------|------|

| 2.6.6 Foreground and Background Colors                      | 2-17 |

| 2.6.7 Transparent or Opaque Mode                            | 2-17 |

| 2.6.8 Pattern Mask                                          | 2-17 |

| 2.7 Geometric Commands                                      | 2-18 |

| 2.8 Bit Block Transfer (Bitblt) Commands                    | 2-18 |

| 2.9 Character Command                                       | 2-18 |

| 2.9.1 Character Font Support                                | 2-18 |

| 2.9.2 Character Storage                                     | 2-19 |

| 2.10 Command Descriptions                                   | 2-23 |

| 2.10.1 ABS_MOV - Move                                       | 2-24 |

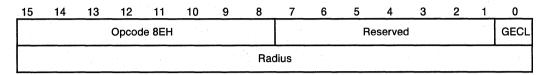

| 2.10.2 ARC – Draw Arc                                       | 2-25 |

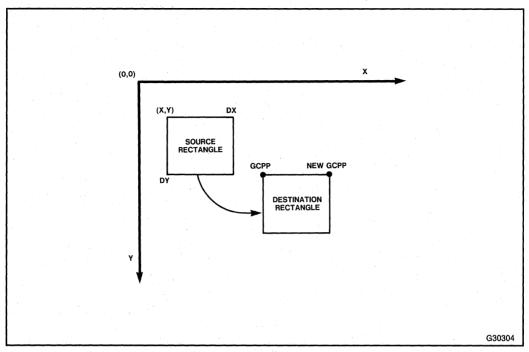

| 2.10.3 BIT_BLT – Bit Block Transfer                         | 2-27 |

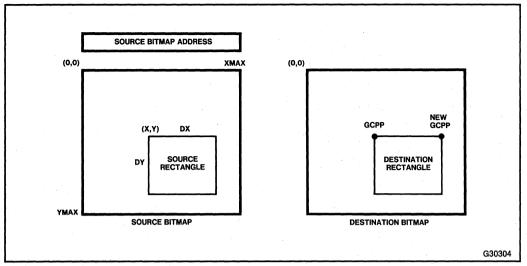

| 2.10.4 BIT_BLT_M - Bit Block Transfer Between Bitmaps       | 2-29 |

| 2.10.5 CALL – Call Subroutine                               |      |

| 2.10.6 CHAR – Draw Character String                         |      |

| 2.10.7 CIRCLE – Draw Circle                                 |      |

| 2.10.8 DEF_BITMAP – Define Bitmap                           |      |

| 2.10.9 DEF_CHAR_ORIENT - Define Character Orientation       |      |

| 2.10.10 DEF_CHAR_SET – Define Character Set                 | 2-43 |

| 2.10.11 DEF_SPACE - Define Space                            |      |

| 2.10.12 DEF_CLIP_RECT - Define Clipping Rectangle           |      |

| 2.10.13 DEF_COLORS – Define Colors                          |      |

| 2.10.14 DEF_LOGICAL_OP – Define Logical Operation           |      |

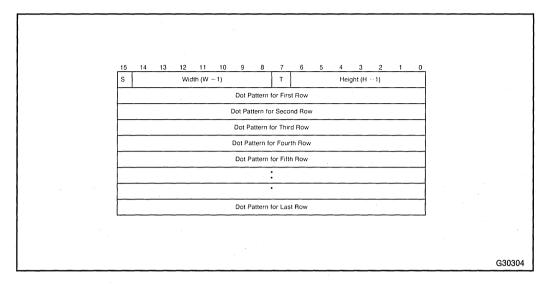

| 2.10.15 DEF_TEXTURE – Define Texture                        | 2-55 |

| 2.10.16 DUMP_REG – Dump Register                            |      |

| 2.10.17 EBITBLT—Expand 1bpp Source to Currently Defined Bpp |      |

| 2.10.18 ENTER_PICK – Enter PICK Mode                        |      |

| 2.10.19 EXIT_PICK – Exit PICK Mode                          |      |

| 2.10.20 HALT – Stops Command Execution                      | 2-62 |

| 2.10.21 INCR_POINT - Draw Series of Incremental Points      |      |

| 2.10.22 INTR_GEN - Generate Interrupt                       |      |

| 2.10.23 LINE – Draw Line                                    |      |

| 2.10.24 LINK - Link Next Command                            |      |

| 2.10.25 LOAD_REG – Load Register                            |      |

| 2.10.26 NOP – No Operation                                  |      |

| 2.10.27 POINT – Draw Point                                  |      |

| 2.10.28 POLYGON – Draw Polygon                              |      |

| 2.10.29 POLYLINE – Draw Polyline                            |      |

| 2.10.30 RECT – Draw Rectangle                               |      |

| 2.10.31 REL_MOV - Relative Move                             |      |

| 2.10.32 RETURN – Return from Subroutine                     |      |

| 2.10.33 SCAN_LINES – Draw Series of Horizontal Lines        | 2-82 |

| CHAPTER 3                                                   | Page |

|-------------------------------------------------------------|------|

| DISPLAY PROCESSOR OVERVIEW                                  |      |

| 3.1 Display Processor Operation                             | 3-1  |

| 3.1.1 Bitmap Organization                                   | 3-1  |

| 3.1.2 IBM PC Bitmap Format Support                          | 3-2  |

| 3.1.3 Window Display Format                                 | 3-4  |

| 3.1.3.1 Strip Descriptors                                   | 3-4  |

| 3.1.3.2 Strip Descriptor Format                             | 3-5  |

| 3.1.4 Cursor                                                | 3-9  |

| 3.1.5 Bus Bandwidth Requirements                            |      |

| 3.2 Video Interface                                         | 3-10 |

| 3.2.1 CRT Controller                                        |      |

| 3.2.2 Video Rates                                           | 3-12 |

| 3.2.3 HSync and VSync Multiplex Window Status               |      |

| 3.2.4 Zoom Support                                          |      |

| 3.2.5 VRAM Support                                          |      |

| 3.2.5.1 Sample VRAM Design                                  |      |

| 3.2.5.2 Hardware Overlays                                   |      |

| 3.2.5.3 Initiating VRAM Mode and Functions                  |      |

| 3.2.6 Extended 82786 System Configurations                  |      |

| 3.3 Display Processor Registers                             |      |

| 3.3.1 Display Processor Internal Registers                  |      |

| 3.3.1.1 DPStatus Register and Exception Handling            |      |

| 3.3.1.2 Interrupts                                          |      |

| 3.3.2 Display Control Block Registers                       |      |

| 3.3.3 Pad Registers                                         | 3-21 |

| 3.4 Display Command Synchronization                         |      |

| 3.5 Command Execution                                       |      |

| 3.6 Display Processor Register Commands                     |      |

| 3.6.1 Load Register (LD RG)                                 |      |

| 3.6.2 Load All (LD ALL)                                     | 3-29 |

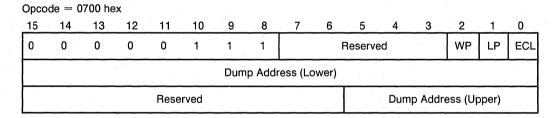

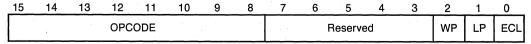

| 3.6.3 Dump Register (DMP RG)                                |      |

| 3.6.4 Dump All (DMP ALL)                                    |      |

| 3.6.5 Loop Command                                          |      |

| 3.6.5.1 Updating Display Processor Registers with Loop Mode |      |

| 3.6.5.2 Suggested Mode of Operation                         |      |

| 3.6.6 Write Protect Bit                                     |      |

| 3.7 Initialization                                          |      |

| 3.8 Video Data Signature Analyzer                           |      |

| 3.8.1 Invoking Test Mode                                    |      |

| 3.8.2 Operation of the Signature Analyzer                   | 3-34 |

### intel®

| CHAPTER 4                                              | Page |

|--------------------------------------------------------|------|

| BUS INTERFACE UNIT OVERVIEW                            |      |

| 4.1 Memory Structure and Internal Registers            | 4-2  |

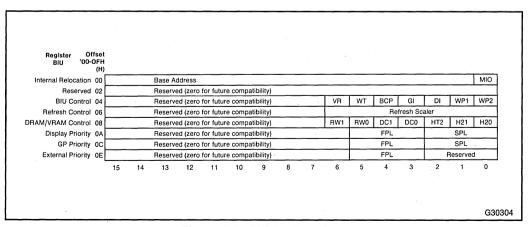

| 4.2 Internal Registers                                 | 4-2  |

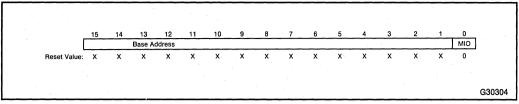

| 4.2.1 Relocation Register                              | 4-3  |

| 4.2.2 Control Register                                 | 4-5  |

| 4.2.3 DRAM/VRAM Refresh Control Register               | 4-6  |

| 4.2.4 DRAM/VRAM Control Register                       | 4-8  |

| 4.2.5 Display Priority Register                        | 4-9  |

| 4.2.6 Graphics Priority Register                       | 4-9  |

| 4.2.7 External Priority Register                       | 4-10 |

| 4.3 Bus Cycle Arbitration                              |      |

| 4.3.1 Priority Levels                                  |      |

| 4.3.2 Priority Exceptions                              | 4-12 |

| 4.4 Master and Slave Interfaces                        | 4-13 |

| 4.4.1 Master Mode Interface                            |      |

| 4.4.1.1 Initiating Master Mode Interface               |      |

| 4.4.1.2 Retaining Control of the System Bus            |      |

| 4.4.2 Slave Interface                                  |      |

| 4.4.2.1 Initiating a Slave Request                     |      |

| 4.4.2.2 8-Bit and 16-Bit Interfaces                    |      |

| 4.4.2.3 Slave Interface Byte Access to Memory          |      |

| 4.4.2.4 Slave Enable (SEN) as Ready Indication         |      |

| 4.4.2.5 Accessing Internal Registers & Graphics Memory | 4-17 |

| 4.4.2.6 Command Lockout                                | 4-18 |

| 4.5 System Bus Interface                               | 4-18 |

| 4.5.1 Synchronous 80286 Interface                      |      |

| 4.5.2 80186 Synchronous Interface                      | 4-22 |

| 4.5.3 Asynchronous Interface                           | 4-23 |

| 4.6 Performance                                        | 4-25 |

| 4.7 RESET Conditions                                   | 4-25 |

| 4.7.1 Special Pins                                     |      |

| 4.7.2 Initialization                                   | 4-25 |

|                                                        |      |

| CHAPTER 5                                              |      |

| GRAPHICS MEMORY                                        |      |

| 5.1 DRAM/VRAM Configurations                           |      |

| 5.1.1 VRAM Considerations                              |      |

| 5.1.2 Considerations for $\times 1$ Memory Devices     | 5-5  |

| 5.1.3 Illegal DRAM/VRAM Control Register Values        | 5-7  |

| 5.1.4 Data Line Connection                             | 5-8  |

| 5.2 DRAM/VRAM Cycle Types                              | 5-8  |

| 5.3 Graphics Memory Refresh                            | 5-10 |

| 5.3.1 Refresh Latency                                  | 5-10 |

| 5.3.2 Refresh after RESET                              | 5-12 |

|                                                                    | Page |

|--------------------------------------------------------------------|------|

| 5.4 Configuring and Accessing Graphics Memory                      | 5-12 |

| 5.5 Memory Map                                                     |      |

| 5.5.1 Mapping the Internal Registers                               | 5-14 |

| 5.5.2 Alternatives for Graphics Memory Mapping                     |      |

| CHAPTER 6                                                          |      |

| VIDEO INTERFACE                                                    |      |

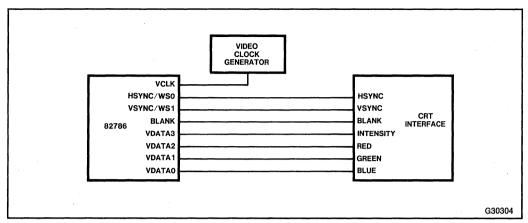

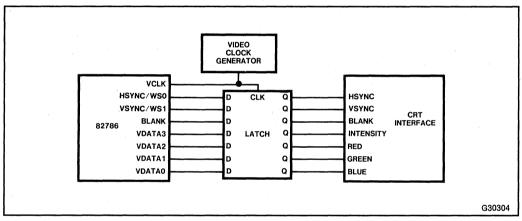

| 6.1 CRT Interfaces                                                 | 6-2  |

| 6.1.1 CRTs with TTL-Level Inputs                                   | 6-2  |

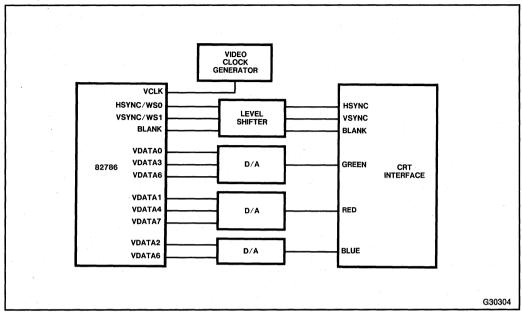

| 6.1.2 CRTs with Analog Inputs                                      | 6-3  |

| 6.2 Using a Color Lookup Table/Video Palette Ram                   | 6-5  |

| 6.3 Window Status Signals                                          | 6-7  |

| 6.3.1 Controlling the Cursor                                       | 6-7  |

| 6.3.2 Window Status Bits Segment Lookup Table for Multiple Windows | 6-9  |

| 6.4 High Resolutions with Standard DRAMs                           |      |

| 6.4.1 External Logic Requirements                                  |      |

| 6.4.2 Software Changes Required for High Resolution                | 6-11 |

| 6.4.3 Cursor Control                                               | 6-12 |

| 6.4.4 Zoom in Accelerated Modes                                    |      |

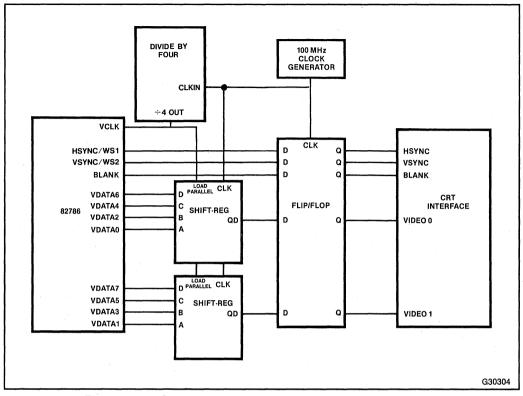

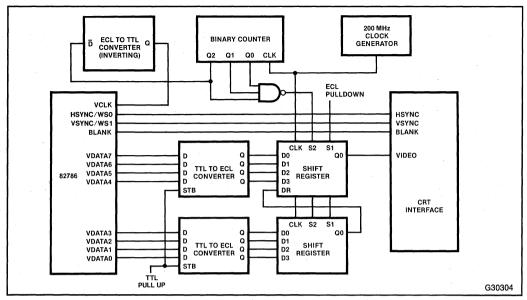

| 6.4.5 Examples of High Resolution Configurations                   | 6-12 |

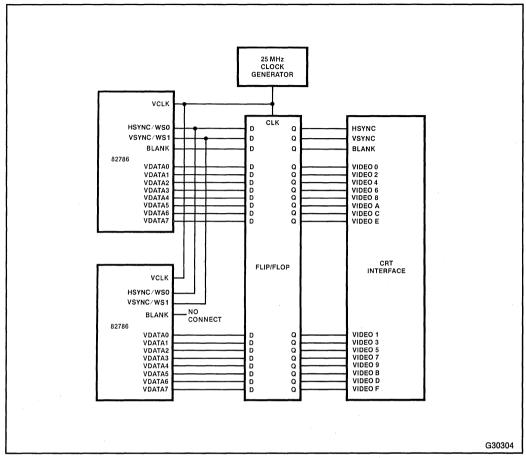

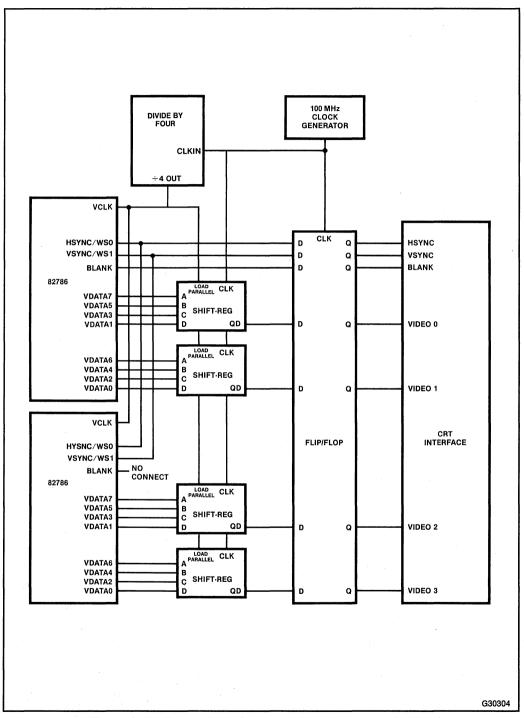

| 6.5 Greater Resolution with Multiple 82786s                        | 6-14 |

| 6.5.1 An Interlaced Display with Two or More 82786s                | 6-16 |

| 6.5.2 Bitmap Configurations with Dual 82786s                       |      |

| 6.6 Video RAM (VRAM) Interface                                     | 6-18 |

| 6.7 External Character ROM                                         | 6-18 |

| 6.8 Combining the 82786 with Other Video Sources                   | 6-20 |

| 6.9 Other Types of Displays and Printers                           | 6-23 |

| 6.9.1 Pixel Clock Rate                                             | 6-23 |

| 6.9.2 Partial Display Updates                                      | 6-23 |

| 6.9.3 Pixel Address Generation                                     | 6-24 |

| 6.9.4 Super High Resolution                                        |      |

| 6.10 Calculating Video Parameters                                  |      |

| 6.10.1 Application Parameters                                      |      |

| 6.10.2 Monitor Parameters                                          |      |

| 6.10.3 Video Interface Parameters                                  | 6-29 |

| 6.10.4 Sample Video Parameter Calculations                         | 6-30 |

| 6.11 A Spreadsheet for Calculating Video Parameters                | 6-34 |

### APPENDIX A TEST MODES

APPENDIX B 88-PIN GRID ARRAY

APPENDIX C 82786 COMMANDS

### **Figures**

| Figure | Title                                                    | Page |

|--------|----------------------------------------------------------|------|

| 1-1    | 82786 Functional Overview                                | 1-1  |

| 1-2    | Sequential Ordering Replaces Traditional Bit Plane Model | 1-4  |

| 1-3    | 82786 128-Byte Internal Register Block                   | 1-8  |

| 1-4    | Low-End Low-Priced Personal Computer                     | 1-9  |

| 1-5    | Multi-Tasking Office Workstation                         | 1-9  |

| 1-6    | High-End Workstation                                     | 1-9  |

| 2-1    | Bitmap Coordinates                                       | 2-2  |

| 2-2    | Graphics Processor Internal Registers                    | 2-5  |

| 2-3    | Graphics Processor Status Register                       | 2-5  |

| 2-4    | Graphics Processor Instruction Pointer                   | 2-6  |

| 2-5    | Graphics Command Format                                  | 2-9  |

| 2-6    | Sample Graphics Command Block (GCMB)                     | 2-11 |

| 2-7    | Opcode Register Used in Poll State                       | 2-12 |

| 2-8    | GP Registers Used in Exception Handling                  | 2-12 |

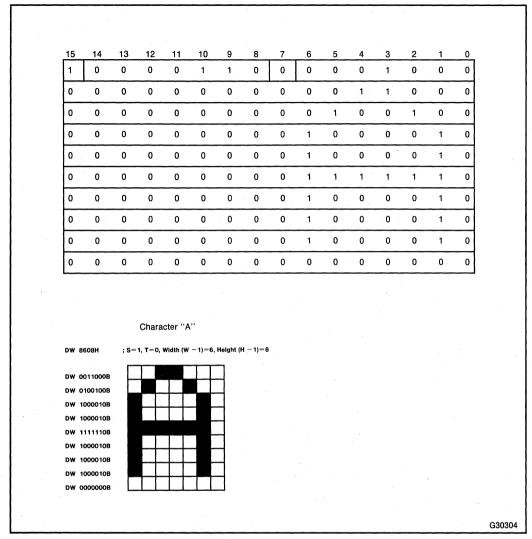

| 2-9    | Character Descriptor Block Format                        | 2-19 |

| 2-10   | Sample Character Descriptor Block                        | 2-21 |

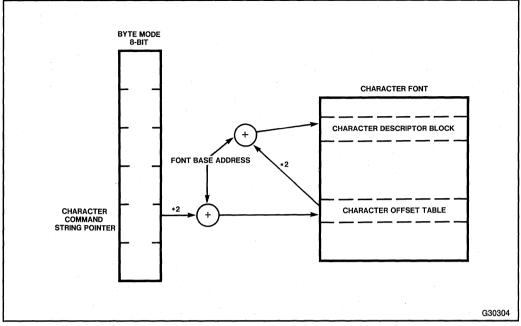

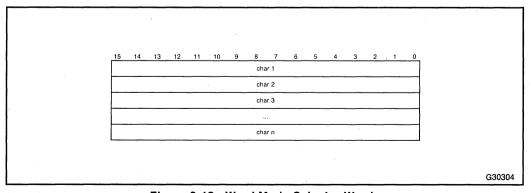

| 2-11   | Byte Mode                                                | 2-22 |

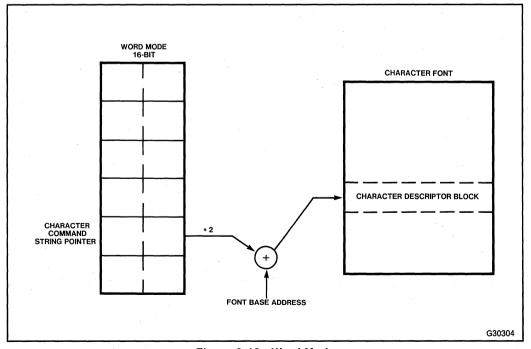

| 2-12   | Word Mode                                                | 2-22 |

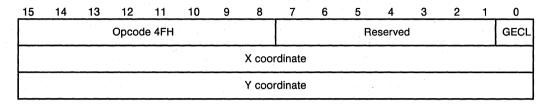

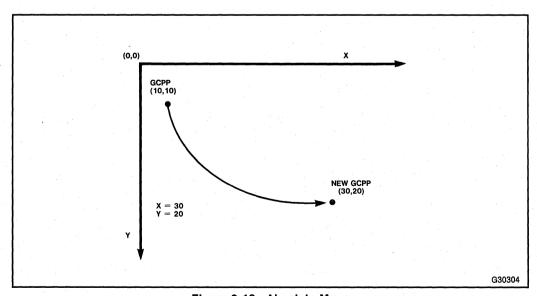

| 2-13   | Absolute Move                                            | 2-24 |

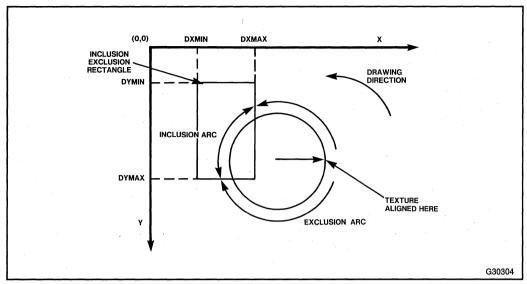

| 2-14   | Draw Arc                                                 | 2-26 |

| 2-15   | Bit Block Transfer                                       | 2-28 |

| 2-16   | Bit Block Transfer Between Two Bitmaps                   | 2-30 |

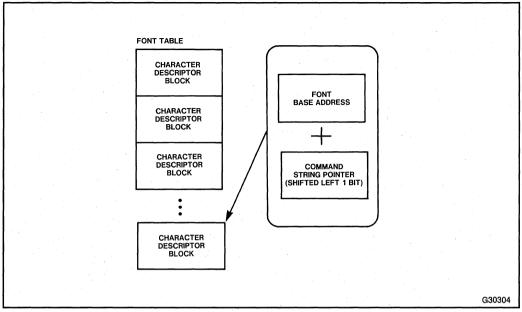

| 2-17   | Character Descriptor Block                               | 2-33 |

| 2-18   | Sample Character Descriptor Block                        | 2-34 |

| 2-19   | Word Mode Selector Words                                 | 2-35 |

| 2-20   | Character Command in Word Mode                           | 2-36 |

| 2-21   | Byte Mode Selector Words                                 | 2-36 |

| 2-22   | Draw Circle                                              | 2-38 |

| 2-23   | Define Bitmap                                            | 2-40 |

| 2-24   | Define Character Orientation                             | 2-42 |

| 2-25   | Character Descriptor Block                               | 2-44 |

### intel°

| Figure                 | Title                                                    |              |

|------------------------|----------------------------------------------------------|--------------|

| 2-26                   | Sample Descriptor Block                                  | 2-44         |

| 2-27                   | Word Mode Character                                      | 2-46         |

| 2-28                   | Byte Mode Character                                      | 2-47         |

| 2-29                   | Define Clipping Rectangle                                | 2-50         |

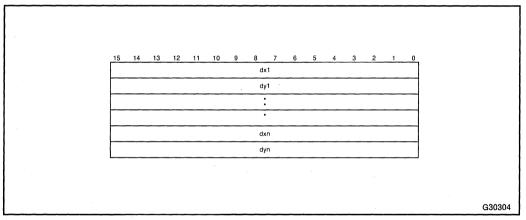

| 2-30                   | Incr_Point Descriptor Array                              | 2-63         |

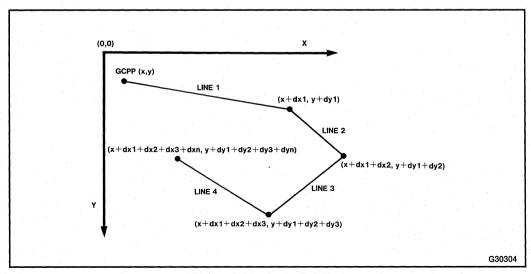

| 2-31                   | Array Values for Incr_Point                              | 2-64         |

| 2-32                   | Draw Line                                                | 2-68         |

| 2-33                   | Draw Point                                               | 2-73         |

| 2-34                   | Draw Polygon                                             | 2-75         |

| 2-35                   | Polygon Vertices Array Information                       | 2-75         |

| 2-36                   | Draw Polyline                                            | 2-76         |

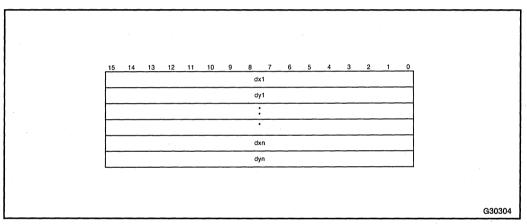

| 2-37                   | Polyline Vertices Array                                  | 2-77         |

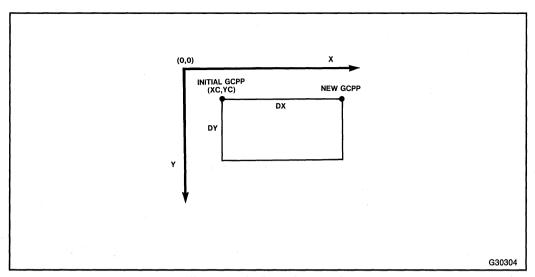

| 2-38                   | Draw Rectangle                                           | 2-79         |

| 2-39                   | Relative Move                                            | 2-80         |

| 2-40                   | Scan_Lines Horizontal Line Array                         | 2-82         |

| 3-1                    | 82786 and IBM PC Swapped Byte Bitmap Formats             | 3-2          |

| 3-2                    | IBM PC CGA Swapped Byte, 2 Bank Example                  | 3-3          |

| 3-3                    | Swapped Byte, 4 Bank IBM PCJr Example                    | 3-3          |

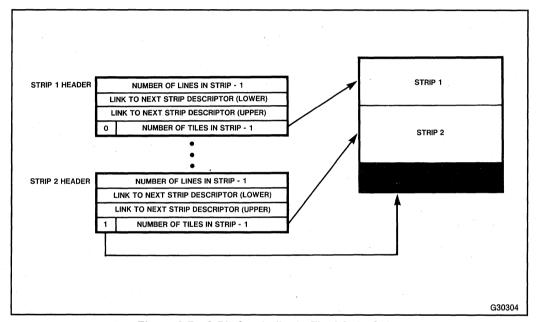

| 3-4                    | Screen Composition with Strips and Tiles                 | 3-4          |

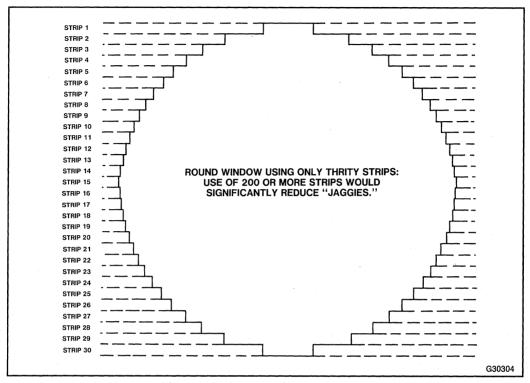

| 3-5                    | Irregular Shaped Window                                  | 3-5          |

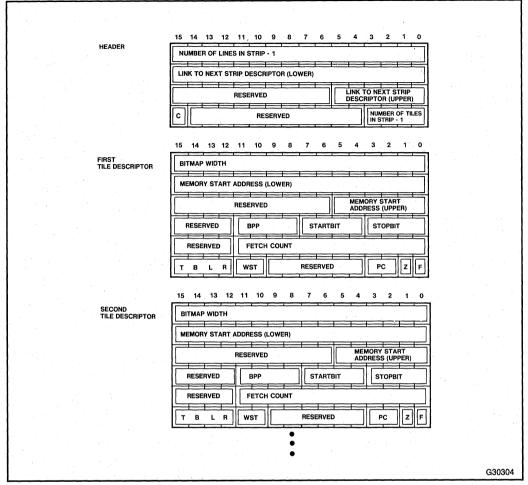

| 3-6                    | Strip and Tile Descriptors                               | 3-6          |

| 3-7                    | C Bit Can Indicate Final Strip Color                     | 3-9          |

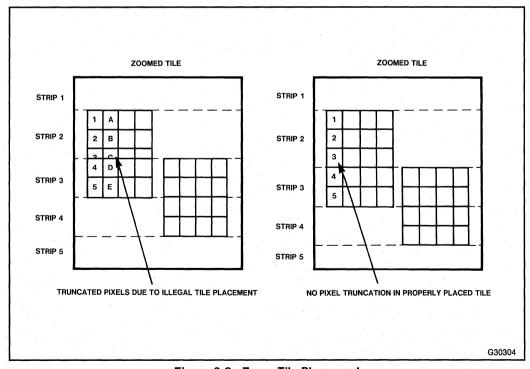

| 3-8                    | Zoom Tile Placement                                      | 3-14         |

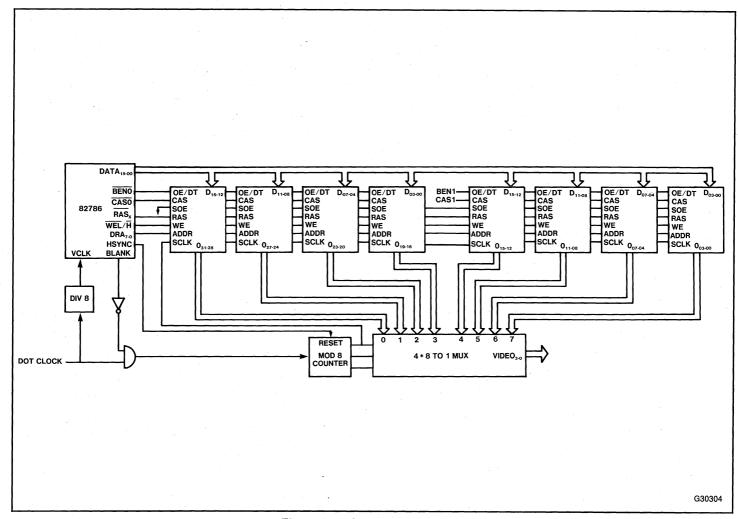

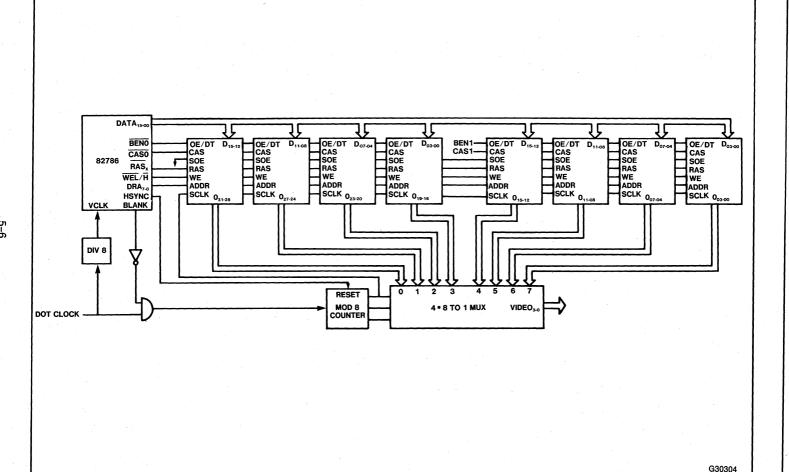

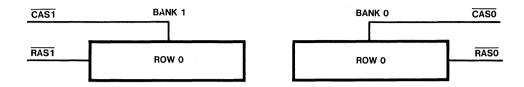

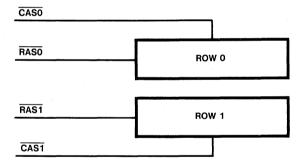

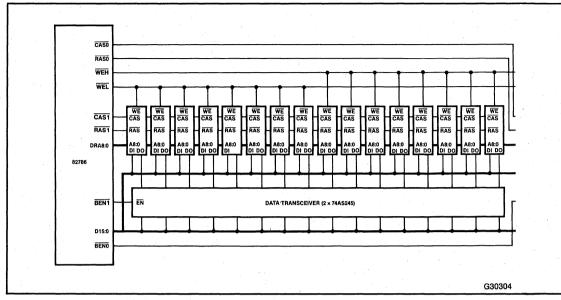

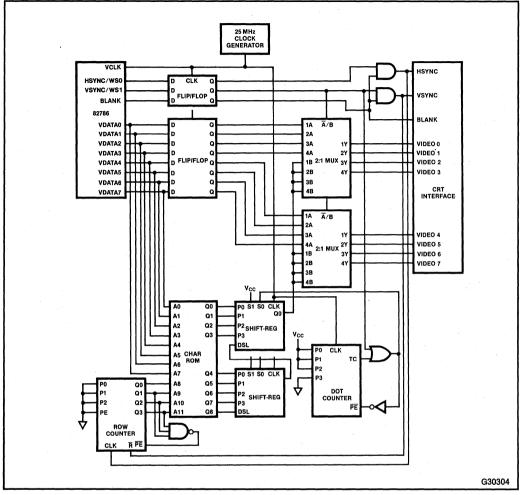

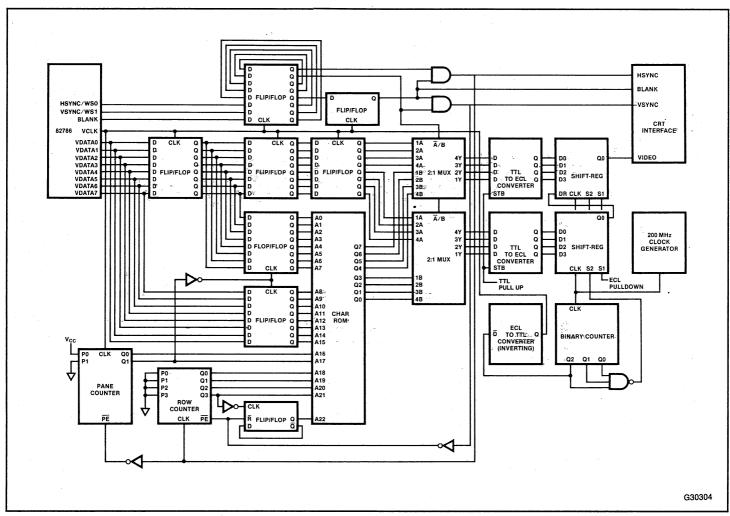

| 3-9                    | Sample VRAM Design                                       | 3-16         |

| 3-10                   | Display Processor Internal Registers                     | 3-19         |

| 3-11                   | DPStatus Register Bits                                   | 3-20         |

| 3-12                   | Display Control Block Registers                          | 3-22         |

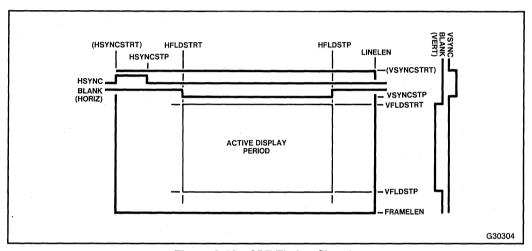

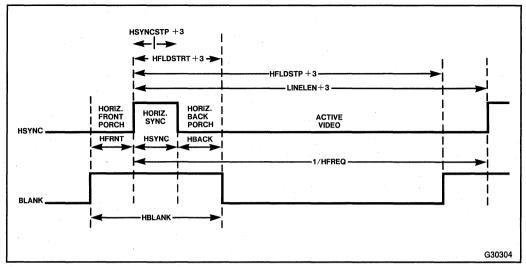

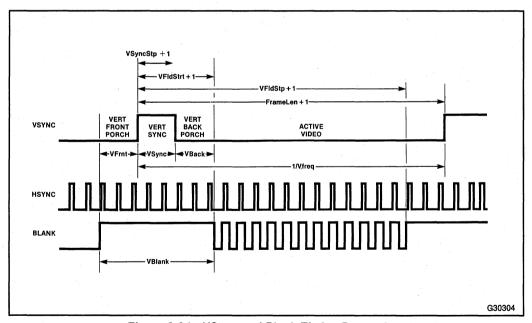

| 3-13                   | CRT Timing Signals                                       | 3-27         |

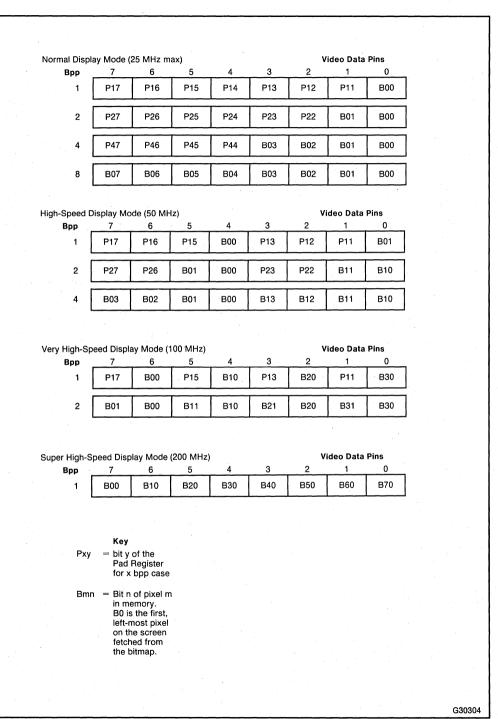

| 3-14                   | Video Data Pin Outputs                                   | 3-28         |

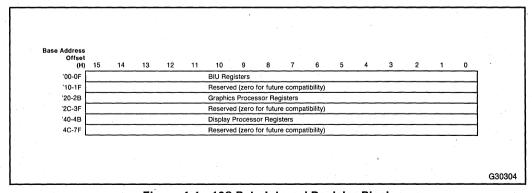

| 4-1                    | 128-Byte Internal Register Block                         | 4-2          |

| 4-2                    | BIU Register Map                                         | 4-3          |

| 4-3                    | Relocation Register                                      | 4-4          |

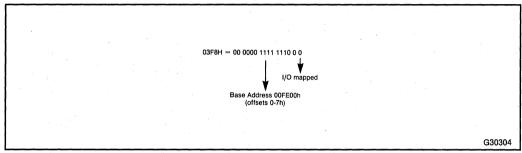

| <del>4-</del> 3<br>4-4 | Internal Relocation Register Address                     | 4-4          |

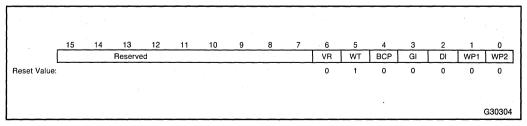

| 4-5                    | BIU Control Register                                     | 4-5          |

| 4-6                    |                                                          | 4-5<br>4-6   |

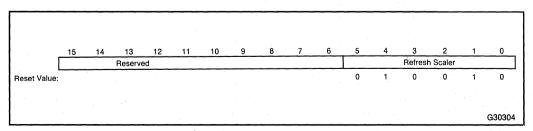

| 4- <del>0</del><br>4-7 | Refresh Scaler                                           | 4-8          |

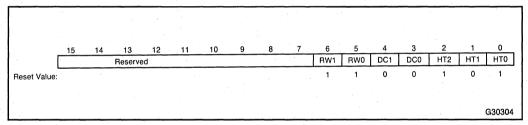

| 4- <i>7</i><br>4-8     | DRAM/VRAM Control Register                               | 4-0<br>4-9   |

|                        | Display Priority Register                                |              |

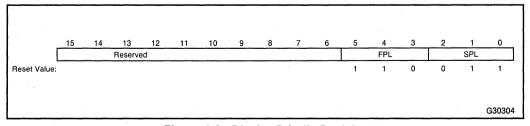

| 4-9<br>4-10            | Graphics Processor Priority Register                     | 4-10         |

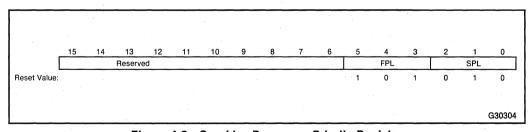

|                        | External Priority Register                               | 4-10         |

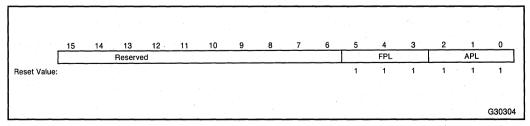

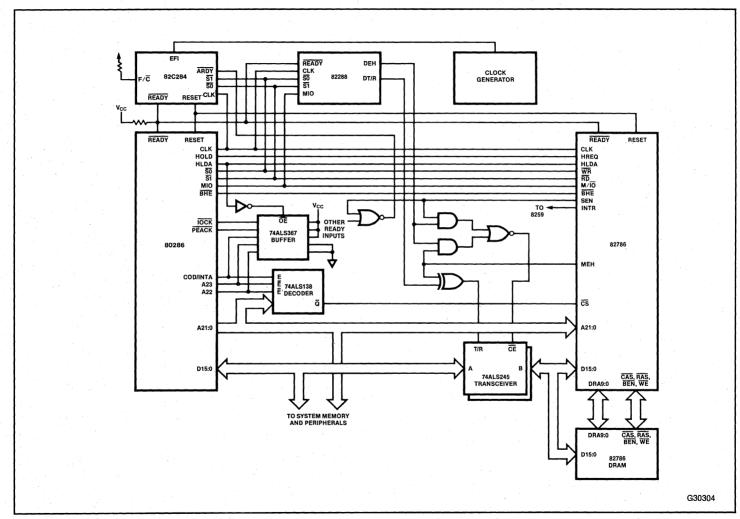

| 4-11                   | 82786 Synchronously Connected to an 80286                | 4-20<br>4-24 |

| 4-12                   | Asynchronous Slave 10 MHz 82786 Interface to 8 MHz 80186 |              |

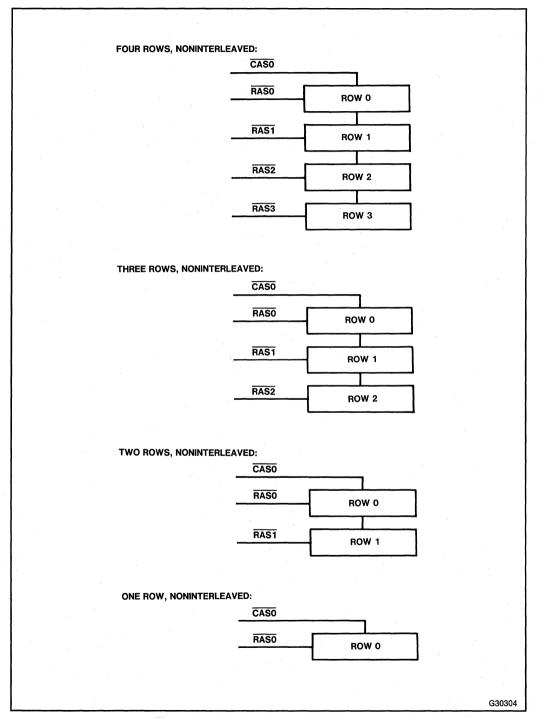

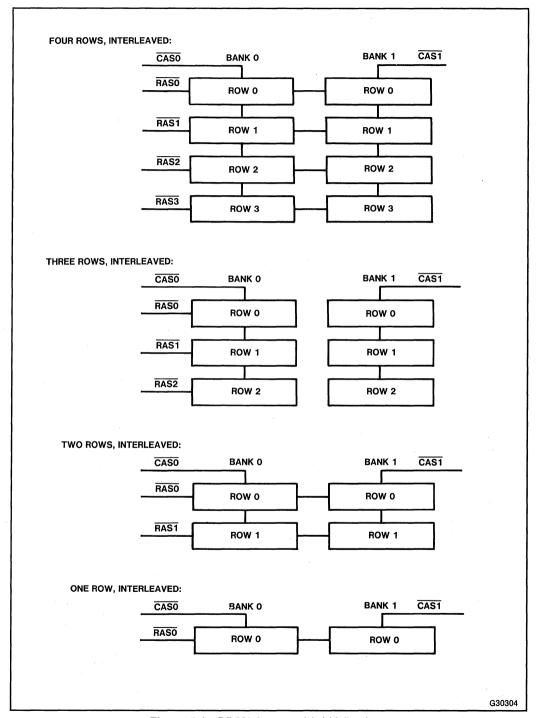

| 5-1                    | Noninterleaved DRAM Arrays                               | 5-2          |

### intel°

| Figure      | Title                                                                            | Page |

|-------------|----------------------------------------------------------------------------------|------|

| 5-2         | DRAM Arrays with ×8 Devices                                                      | 5-3  |

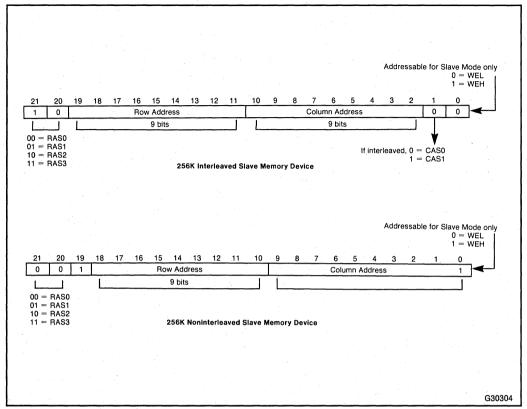

| 5-3         | Correlation of Address with RAS and CAS                                          | 5-4  |

| 5-4         | External Multiplexers Provide 4 Bpp                                              | 5-6  |

| 5-5         | Two Interleaved Banks of 256K × 1                                                | 5-8  |

| 5-6         | Data Line Connections X1                                                         | 5-10 |

| 5-7         | Data Line Connections ×4 and ×8                                                  | 5-11 |

| 5-8         | 82786 Viewpoint of Graphics Memory Map                                           | 5-13 |

| 5-9         | CPU Memory Map                                                                   | 5-14 |

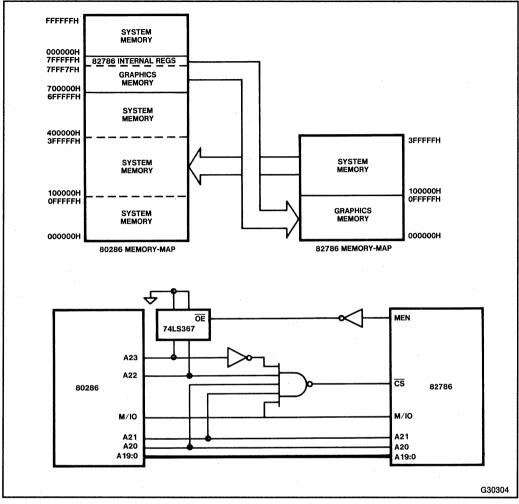

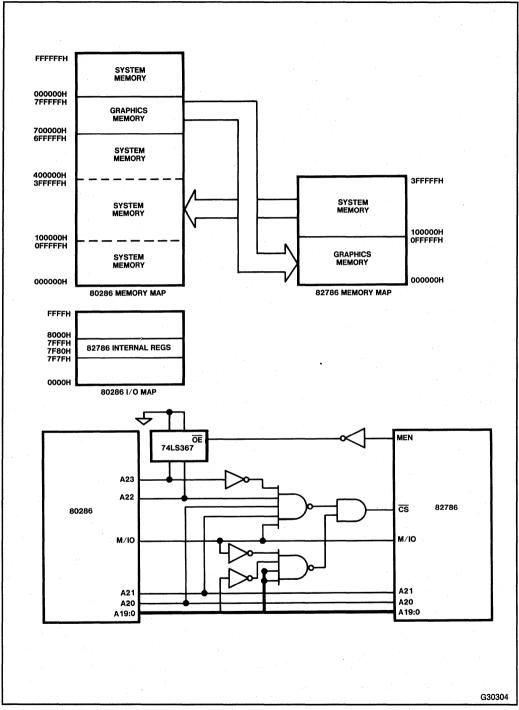

| 5-10        | Possible Memory Map for 80286/82786 System with Memory Mapped Internal Registers | 5-15 |

| 5-11        | Memory Mapping for 80286/82786 System with I/O Mapped Internal                   |      |

| <b>5</b> 40 | Registers                                                                        | 5-16 |

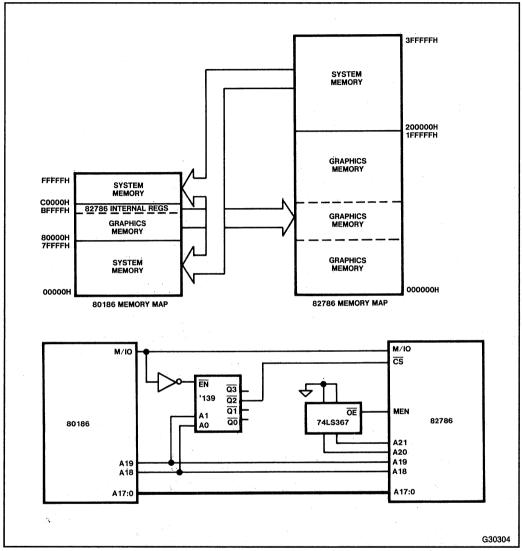

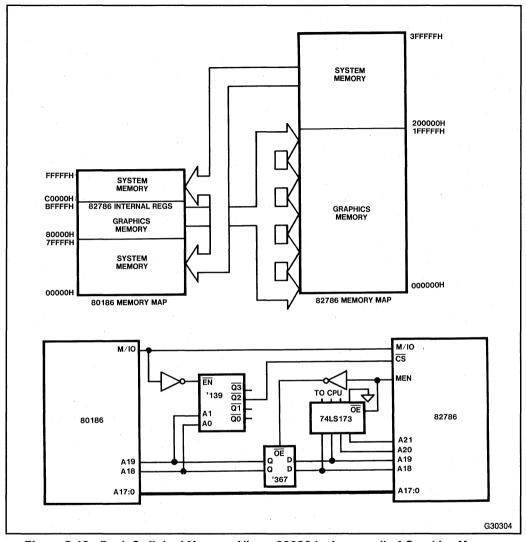

| 5-12        | 80186 System Accesses Only a Portion of Graphics Memory                          | 5-17 |

| 5-13        | Bank Switched Memory Allows 80286 to Access all of Graphics Memory               | 5-18 |

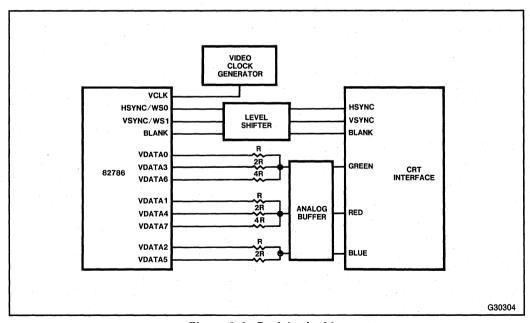

| 6-1         | 82786 Drives CRT with TTL-Level Inputs                                           | 6-3  |

| 6-2         | Buffer Used to Drive TTL-Input CRT Interface                                     | 6-3  |

| 6-3         | Analog CRT Interface Allows 256 Colors                                           | 6-4  |

| 6-4         | Resistor Ladder                                                                  | 6-4  |

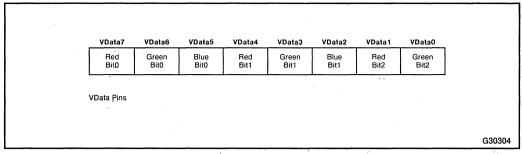

| 6-5         | VDATA Color Assignments                                                          | 6-5  |

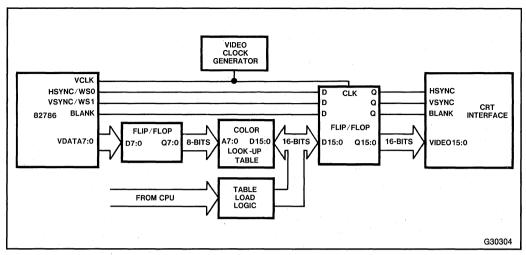

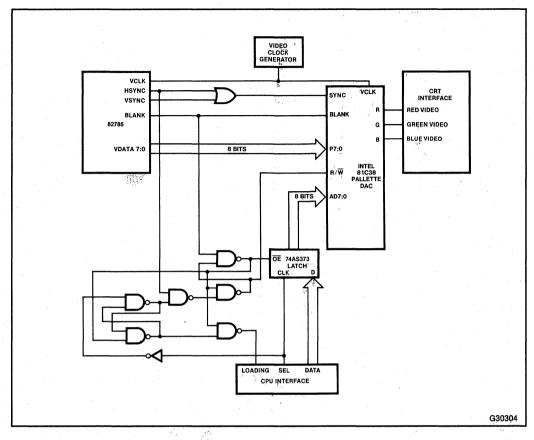

| 6-6         | Color Lookup Table                                                               | 6-6  |

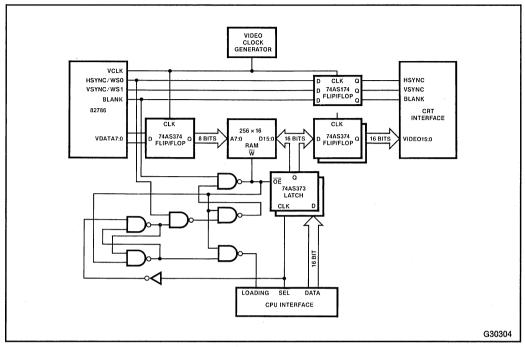

| 6-7         | Color Lookup Table Circuit Generates 16 Video Bits from 8                        | 6-7  |

| 6-8         | Hybrid Color Lookup Table and DAC Simplifies Interface                           | 6-8  |

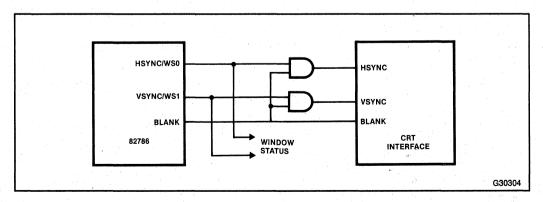

| 6-9         | Blank Demultiplexes Window Status Pins                                           | 6-8  |

| 6-10        | Four Color Lookup Tables Selectable by Window Status Outputs                     | 6-9  |

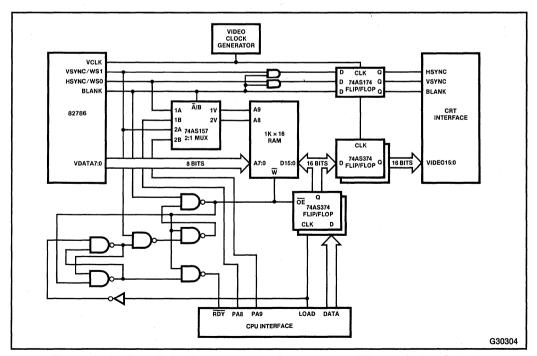

| 6-11        | External Multiplexer Allows up to 50 MHz Video with 4 Bpp                        | 6-10 |

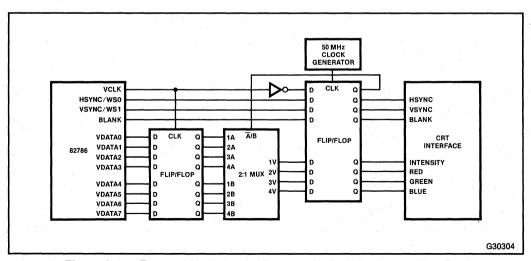

| 6-12        | Configuration for Video Data Rates up to 100 MHz                                 | 6-13 |

| 6-13        | External ECL Shift Register Allows up to 200 MHz Video with 1 Bpp                | 6-14 |

| 6-14        | Dual 82786s Generate 16 Bpp at 25 MHz                                            | 6-15 |

| 6-15        | Two 82786s Create a 4-Bpp Display at 100 MHz                                     | 6-17 |

| 6-16        | Character ROM and Bitmap Graphics on Same Screen                                 | 6-20 |

| 6-17        | Very Large Character ROM and Bitmap Graphics on Same Screen                      | 6-21 |

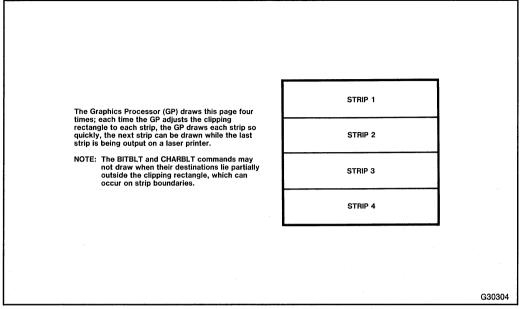

| 6-18        | Dividing a Page into Strips Decreases Memory Requirements                        | 6-25 |

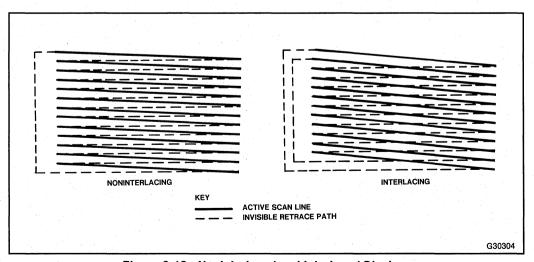

| 6-19        | Noninterlaced and Interlaced Displays                                            | 6-26 |

| 6-20        | HSync and Blank Timing Parameters                                                | 6-28 |

| 6-21        | VSync and Blank Timing Parameters                                                | 6-28 |

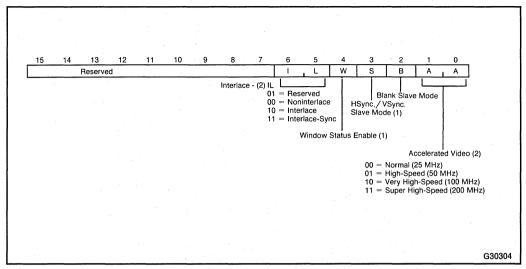

| 6-22        | Display Processor Register 05H                                                   | 6-30 |

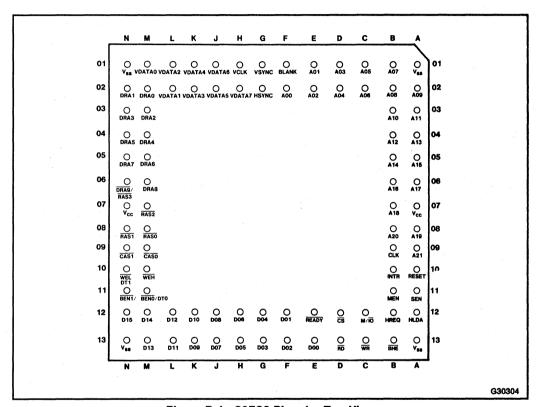

| B-1         | 82786 Pinout — Top View                                                          | B-1  |

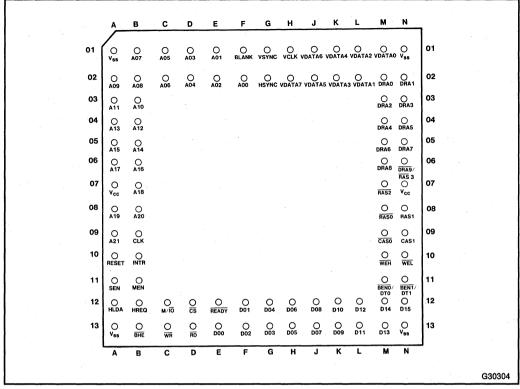

| B-2         | Pinout 82786 — Bottom View                                                       | B-2  |

### **Tables**

| Table | Title                                     | Page |

|-------|-------------------------------------------|------|

| 2-1   | Bits Per Pixel (bpp) and Pixels Per Word  | 2-3  |

| 2-2   | Effective Address Variables               | 2-3  |

| 2-3   | Graphics Processor Status Register Bits   | 2-6  |

| 2-4   | Graphics Processor Control Registers      | 2-7  |

| 2-5   | Context Registers                         | 2-8  |

| 2-6   | Drawing Command Attributes                | 2-14 |

| 2-7   | Logical Operations                        | 2-15 |

| 2-8   | Logical Operations                        | 2-52 |

| 2-9   | Control Registers                         | 2-56 |

| 2-10  | Context Registers                         | 2-57 |

| 2-11  | Increment Point Codes                     | 2-64 |

| 2-12  | Incr_Point Command Array Values           | 2-65 |

| 3-1   | Tile Descriptor Parameters                | 3-7  |

| 3-2   | Possible CRT Displays with Standard DRAMs | 3-11 |

| 3-3   | Possible CRT Displays with VRAMs          | 3-11 |

| 3-4   | HSync, VSync, and Blank Settings          | 3-11 |

| 3-5   | Timing Signal Resolution Changes          | 3-13 |

| 3-6   | BPP for Dot Rate Tradeoffs                | 3-13 |

| 3-7   | DPStatus Register                         | 3-20 |

| 3-8   | Display Control Registers                 | 3-23 |

| 4-1   | RW1:0 Values                              | 4-8  |

| 4-2   | DC1:0 Values                              | 4-8  |

| 4-3   | HT2:0 Values                              | 4-9  |

| 4-4   | Default Priority Levels Following RESET   | 4-12 |

| 4-5   | Suggested Priority Values                 | 4-12 |

| 4-6   | 80286 Bus Master Performance              | 4-14 |

| 4-7   | 82786 Address Comparison                  | 4-18 |

| 4-8   | 82786 Status Interface for the 80286      | 4-18 |

| 4-9   | BHE# and MIO Pin Values                   | 4-19 |

| 5-1   | Memory Configurations                     | 5-9  |

| 5-2   | DRAM Single Cycle Times                   | 5-11 |

| 5-3   | DRAM Block Transfer Rates                 | 5-11 |

| 6-1   | Possible CRT Displays with Standard DRAMs | 6-1  |

| 6-2   | Possible CRT Displays with VRAMs          | 6-2  |

| 6-3   | Valid StartBit and StopBit Values         | 6-11 |

| 6-4   | HSync, VSync, and Blank Settings          | 6-22 |

| 6-5   | Accelerated Video Mode Values             | 6-29 |

| A-1   | 82786 Test Modes                          | A-1  |

| B-1   | Pin Descriptions                          | B-2  |

### CHAPTER 1 82786 GRAPHICS COPROCESSOR OVERVIEW

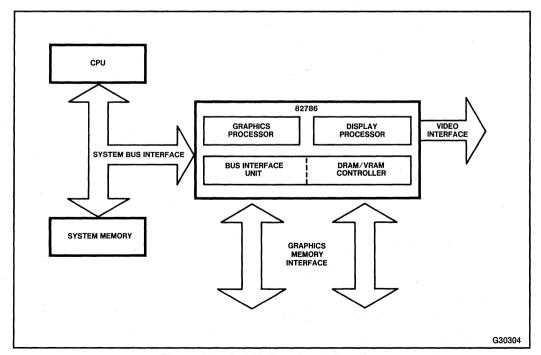

The 82786 is an intelligent graphics coprocessor that replaces subsystems and boards, which traditionally use discrete components and/or software for graphics functions. In a single 88-pin grid array or leaded carrier, the 82786 integrates a:

- Graphics Processor,

- Display Processor with a CRT controller, and a

- Bus interface unit with a DRAM/VRAM controller supporting 4 MB of memory, which can consist of both graphics and system memory.

The Graphics Processor (GP) and the Display Processor (DP) are independent processors on the 82786. The Bus Interface Unit (BIU) with its DRAM/VRAM controller arbitrates bus requests between the Graphics Processor (GP), Display Processor (DP), and the External CPU or Bus Master.

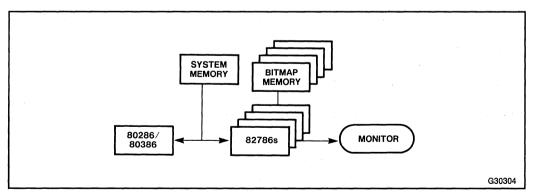

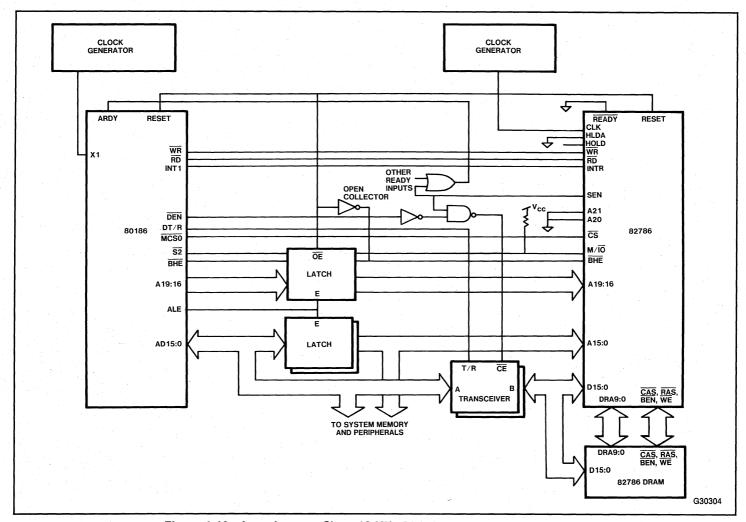

Figure 1-1 provides a functional overview of the 82786. Refer to Appendix B for top and bottom pin-out views and a description of each pin.

Figure 1-1. 82786 Functional Overview

The integrated design of the 82786 increases programming efficiency and overall performance while decreasing development and production time and costs of many microprocessor-based graphics applications such as personal computers, engineering workstations, terminals, and laser printers. Compatibility with Intel microprocessors, the many device independent standards, and IBM Personal Computer bitmap memory format (see Section 3.1.2 "IBM PC Bitmap Format Support") combined with support for international character sets, multitasking, and an 8- or 16-bit host makes programming the 82786 flexible and straightforward. The extensive features of the 82786 accommodate many designs. The list below contains some of the main 82786 features.

- Available in 88-pin grid array or leaded carrier

- Interface designed for device independent software

- Integrated drawing engine with a high-level computer graphics interface instruction set

- Supports multiple character sets (fonts) that can be used simultaneously for text display applications

- Hardware support for fast manipulation and display of multiple windows on the screen

- DRAM/VRAM controller supporting up to 4 MB of graphics memory, shift registers, and DMA channel

- Supports sequential access DRAMs and dual port video DRAMs (VRAMs)

- Fast bit-block transfers (bitblt) between system and graphics memory

- Supports up to 200 MHz CRTs or other video interface

- Up to 256 simultaneous colors per frame

- Programmable video timing

- Third-party software support

- Supports rapid pattern fill

- International character support

- Advanced CHMOS technology

- IBM Personal Computer bitmap formats

Support for high resolution displays using a 25 MHz pixel clock lets the 82786 display up to 256 colors simultaneously. Systems designed with multiple 82786s or a single 82786 with VRAMs can support virtually unlimited color and resolution.

### 1.0 REVISION INFORMATION

This revision (-003) of the 82786 Graphics Coprocessor User's Manual reflects the features and capabilities of the "D" level of revision of the component, noted in this manual by the term "D-step."

### 1.1 ARCHITECTURE

The powerful yet flexible design of the 82786 requires minimal support circuitry for most applications, which reduces costs and board space requirements for many applications.

Also key to the 82786 is its memory structure. The 82786 can access either graphics memory directly supported by the integral DRAM/VRAM controller or external system memory that resides on the CPU bus. When the 82786 accesses system memory, it controls the bus and operates in Master Mode. The 82786 can also operate as a Slave with the CPU accessing the 82786 graphics memory and the Internal Registers. From the software standpoint, the 82786 accesses graphics and external system memory in the same manner. However, performance increases when the 82786 accesses its own graphics memory because the 82786 DRAM/VRAM controller accesses it directly without encountering contention with the CPU. Conversely, the CPU accesses its own system memory more quickly than graphics memory because it does not encounter contention from the Display Processor (DP) or Graphics Processor (GP).

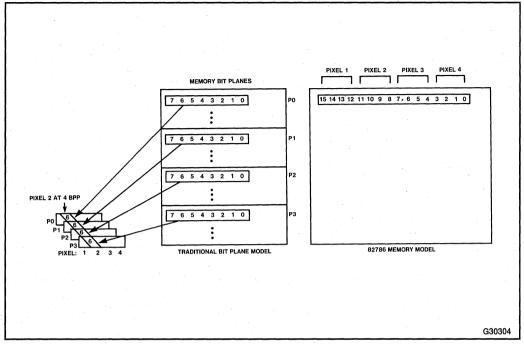

Another feature of the 82786 is the bitmap organization. Replacing the traditional "bit plane" memory model, the 82786 utilizes sequential ordering (linear memory) and takes advantage of the fast sequential access modes of DRAMs or dual port video DRAMs (VRAMs) to gain performance. The 82786 supports a packed pixel bitmap organization for color in which all color bits for each pixel are stored in the same byte in memory. In the traditional bit plane model, each plane defines separate color information. For example, a 4-plane bitmap describes a bitmap with four colors as shown in Figure 1-2. Each byte of memory contains one bit of color information for each pixel in the 4-plane bitmap. In the 82786 packed pixel model, each byte stores data for two pixels. Section 2.1.3 "Pixels" describes the packed pixel bitmap in detail.

### 1.1.1 Graphics Processor (GP)

The 82786 Graphics Processor (GP) draws all geometric objects and characters and moves images within and between bitmaps. The GP creates and updates the bitmap, executes commands placed in memory by the host CPU, and updates the bitmap memory for the Display Processor (DP). The GP high-level commands provide high speed drawing of graphics objects and text. The GP performs all these functions independent of the DP. Refer to Chapter 2 for a detailed discussion of the GP and its functions.

### 1.1.2 Display Processor/CRT Controller (DP)

The Display Processor (DP) traverses bitmaps generated by the Graphics Processor (GP) or external CPU, organizes the data, and displays the bitmaps in the form of windows on the screen. The DP has a video shift register that can assemble several windows on the screen from different bitmaps in memory and zoom any of the windows in the horizontal and/or vertical directions. When the DP detects a window edge, it automatically switches to the next bitmap to display the subsequent window.

Figure 1-2. Sequential Ordering Replaces Traditional Bit Plane Model

Essentially, the DP operates as an address generator that accesses appropriate portions of memory-resident bitmaps. The data fetched from bitmaps is passed to the DP CRT controller, which displays the bitmap data on the screen. The DP CRT controller generates and synchronizes the Horizontal Synchronization (HSync), Vertical Synchronization (VSync), and Blank signals. The DP performs all these functions independent of the GP. Refer to Chapter 3 for a detailed discussion of the DP and its functions.

### 1.1.3 Display Processor (DP) Master and Slave Modes

The Display Processor operates as a Master or a Slave based on the Horizontal Synchronization (HSync) and Vertical Synchronization (VSync) signals, which are set with the S bit in the CRTMode Display Control Register (see Table 3-8 in Section 3.3.2 "Display Control Block Registers"). When the S bit is set to one, the DP is a slave with the HSync and VSync signals as inputs. If the S bit is 0, the DP operates as a Master with HSync and VSync as outputs. For details, refer to Section 3.2.1 "CRT Controller."

### 1.1.4 Bus Interface Unit (BIU)

The Bus Interface Unit (BIU) controls communication between the 82786, the external CPU, and graphics and external system memory when both are configured. A low-end system can use a single memory shared by the CPU and 82786 with the DRAM/VRAM controller

managing memory accesses as shown in Figure 1-4 in Section 1.2 "System Configurations." The BIU uses a DRAM/VRAM controller that supports dual port video DRAMs (VRAMs) and high speed burst access modes of page and fast page mode DRAMs. Both the GP and DP use the BIU to access bitmaps in memory. Refer to Chapter 4 for a detailed discussion of BIU concepts.

### 1.1.5 Memory Structure

The 82786 can address 4 MB of memory. Most systems divide memory in at least two segments: the 82786 graphics memory, which uses the DRAM/VRAM controller, and external system memory. Dividing memory can enhance the performance of graphics applications. The DRAM/VRAM controller allows faster access to graphics memory than external system memory because it does not encounter contention from the CPU. The CPU accesses system memory and executes programs simultaneously, while the 82786 accesses graphics memory and executes its commands. For sample system configurations, see Figures 1-5 and 1-6 in Section 1.2 "System Configurations."

However, when performance is not critical, the 82786 and CPU can share the same memory with the integral 82786 DRAM/VRAM controller managing memory accesses. With this configuration, target applications must be able to tolerate the decreased bandwidth of system memory. For a sample system configuration, see Figure 1-4 in Section 1.2 "System Configurations."

The 82786 assumes graphics memory starts at address 0H and ascends to the configured value, specified in the BIU DRAM/VRAM Control Register described in Section 4.2.4 "DRAM/VRAM Control Register." The 82786 can support a maximum of 4 MB of graphics memory, but the 82786 cannot access system memory if all its 4 MB addressing capacity is configured as graphics memory.

### 1.1.6 Memory Access and Arbitration

The BIU receives requests to access graphics memory from the Graphics Processor (GP), Display Processor (DP), and CPU. The BIU also receives memory refresh requests from the DRAM/VRAM controller. The BIU uses a priority system to arbitrate all requests. Memory refresh requests always have highest priority. Other requests have programmable priorities. A higher priority memory cycle can interrupt a lower one. For details, refer to Section 4.3 "Bus Cycle Arbitration."

### 1.1.7 Master and Slave Memory Access Interfaces

During memory access, the 82786 operates either as a Master or a Slave. The 82786 operates as a Master when it accesses external system memory. The 82786 acts as a Slave when the host CPU accesses graphics memory or any of the 82786 Internal Registers (see Section 1.1.8).

### 1.1.7.1 MASTER MODE INTERFACE

The 82786 operates as a Master whenever it accesses a memory address that is beyond the upper limit of configured graphics memory. Usually, this memory is external memory that the 82786 and CPU share. A high level on the Hold Request (HREQ) line indicates the 82786 is requesting the bus. The 82786 drives the external bus only after it receives a Hold Acknowledge (HLDA) from the External Bus Master. The HLDA is either externally synchronized (82786 synchronous mode) or internally synchronized (82786 asynchronous mode). The 82786 deactivates the HREQ when it no longer needs to access external memory or senses an inactive HLDA. The 82786 indicates that it controls the bus by a high level on the Master Enable (MEN) output. Details on the synchronous and asynchronous modes are discussed in Section 4.5 "System Bus Interface." For details on the Master Mode Interface, refer to Section 4.4.1.

### 1.1.7.2 SLAVE INTERFACE

As a Slave, the 82786 receives requests from the External Bus Master. For example, the host CPU accesses the 82786 graphics memory or its Internal Registers. The external CPU starts a slave access by asserting the Chip Select Low  $(\overline{CS})$  input for a read/write to the 82786. When the 82786 is not Bus Master, the address lines (A21:0), Read Low  $(\overline{RD})$ , Write Low  $(\overline{WR})$ , Memory-I/O (MIO), and Byte High Enable Low  $(\overline{BHE})$  lines are inputs. The 82786 constantly monitors the  $\overline{RD}$ ,  $\overline{WR}$ , MIO, and  $\overline{CS}$  lines to detect whether a CPU cycle occurred. The 82786 indicates the beginning of a Slave access by bringing Slave Enable (SEN) high and indicates the end of the access by bringing SEN low. The data bus transceiver can be enabled by SEN. For details on the Slave Interface, refer to Section 4.4.2.

### 1.1.8 Internal Registers

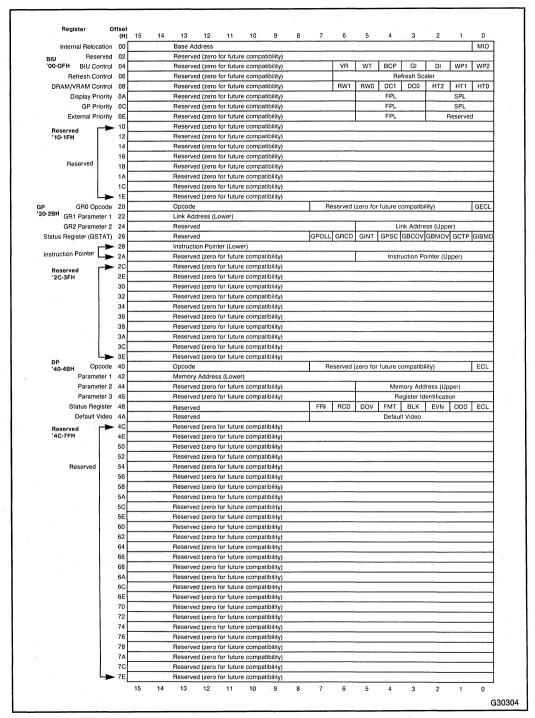

The 82786 has a 128-byte block of contiguous directly addressable Internal Registers, which is shown in Figure 1-3. The host CPU directly addresses this block of Internal Registers to communicate with the Graphics Processor (GP), Display Processor (DP), and Bus Interface Unit (BIU). The block can be either Memory or I/O mapped in the CPU address space. The base address and memory-I/O map (MIO) option are programmable through the BIU Internal Relocation Register, described in Section 4.2.1.

### 1.2 SYSTEM CONFIGURATIONS

The high performance and flexible features of the 82786 offer excellent solutions for a diverse range of applications and system configurations. Figures 1-4 through 1-6 illustrate just a few system designs.

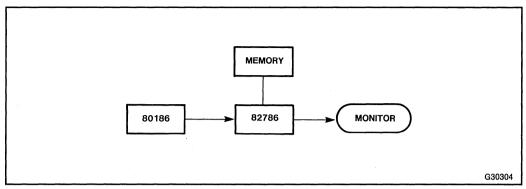

In Figure 1-4, the 82786 combined with the 80186, shared system and graphics memory, and a monitor provide a low-end, low-priced, graphics system. In this system the CPU and the 82786 share memory and use the 82786 DRAM/VRAM controller for managing memory accesses. Target applications must tolerate the decreased bandwidth of system memory.

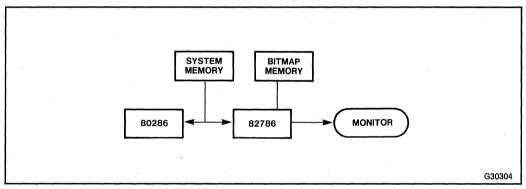

In Figure 1-5, the 82786 combined with an 80286, separate system and graphics memory, and a monitor provide an excellent multi-tasking office workstation.

For processing-intensive engineering environments, Figure 1-6 depicts a system with multiple 82786s in which each 82786 configures 4 MB of memory, an 80286 or 80386, and a monitor, which offers a powerful solution.

Figure 1-3. 82786 128-Byte Internal Register Block

Figure 1-4. Low-End Low-Priced Personal Computer

Figure 1-5. Multi-Tasking Office Workstation

Figure 1-6. High-End Workstation

### CHAPTER 2 GRAPHICS PROCESSOR OVERVIEW

The Graphics Processor (GP) is an independent processor within the 82786 that creates and manages bitmaps in graphics or system memory. The GP creates and updates all graphics and text in each bitmap. The GP draws and moves all images in and between bitmaps. The list below outlines major functions provided by the GP.

- permits bitmaps to be any size (up to  $32K \times 32K$  pixels) and use 2, 4, 16, or 256 colors depending on the number of bits per pixel (bpp) which can be 1, 2, 4, or 8

- draws geometric shapes with attributes such as texture and color

- draws characters from user-defined fonts with attributes such as color, path, rotation, and proportional spacing

- combines one rectangular portion of a bitmap with another area, within the same bitmap or into another bitmap

- allows logical operations between source and destination (for example, logical Exclusive-OR or Complement of Source with Destination)

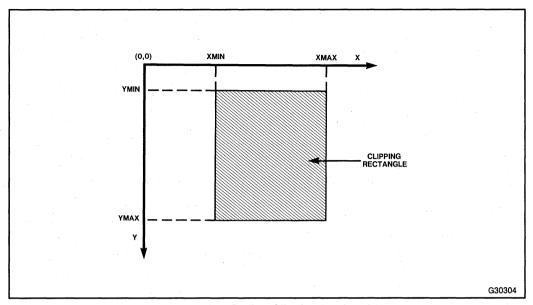

- clips drawings to a rectangular region

- supports picking, a mechanism used by user interfaces to select graphics menus (called icons) with a pointing device such as a mouse

### 2.1 GRAPHICS CONCEPTS

To use the 82786 effectively, an understanding of basic graphics concepts and how they relate to the 82786 is essential. The following sections discuss bitmaps, pixels, calculating the effective address of pixels, bitmap coordinates, and windows in the 82786 environment.

### 2.1.1 Bitmaps

The 82786 writes all graphics and text into bitmaps in memory. Each bitmap is a rectangular drawing area consisting of pixels that describe a graphic image or a character. The size of a bitmap varies based on the number of pixels and the number of bits associated with each pixel. A bitmap can be up to 32,768 pixels in each direction and contain 1, 2, 4, or 8 bits of color or gray scale information for each pixel. The amount of available memory determines the number of bitmaps that can exist.

A bitmap and the output display area do not necessarily correspond on a one-to-one basis. For example, a bitmap can be larger or smaller than the screen output area. Each bitmap has a specific number of bpp, whereas a screen can display several bitmaps; each with a different number of bpp. The Display Processor (DP) interprets the information residing within bitmaps and extracts a bitmap which can be positioned anywhere on the screen as a window. For details on DP operation, refer to Chapter 3.

Programming and performance efficiency can be improved by segmenting graphics and system memory, and using graphics memory and separate bitmaps for generating text and color graphics. The GP can access graphics memory faster than system memory because it does not encounter CPU contention. Two bitmaps can increase efficiency if, one bitmap contains text with one bit per pixel (bpp) and the other bitmap contains a multicolor graphic image with several bpp.

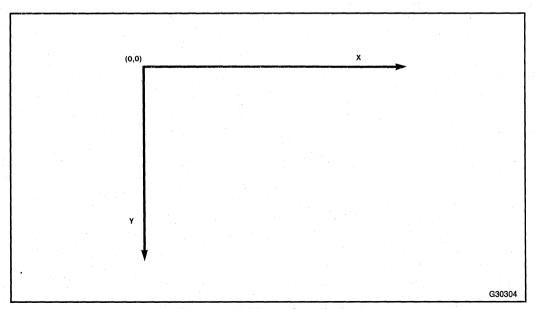

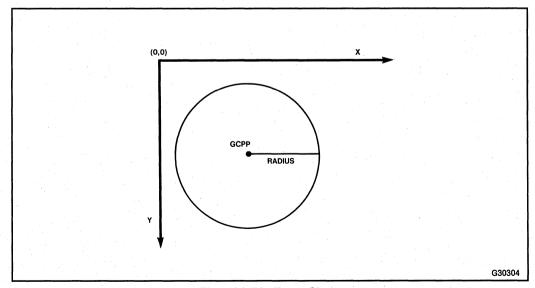

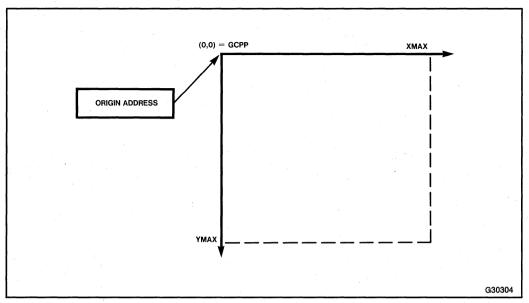

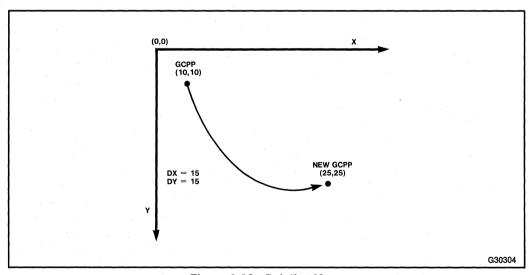

### 2.1.2 Bitmap Coordinates

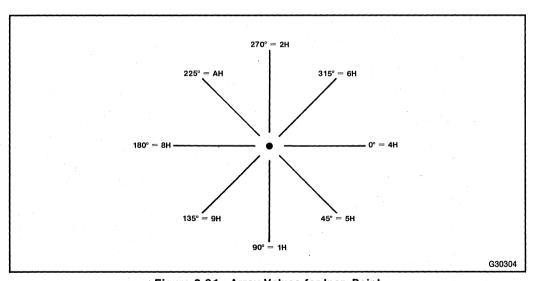

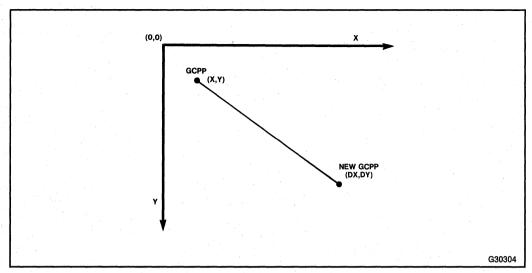

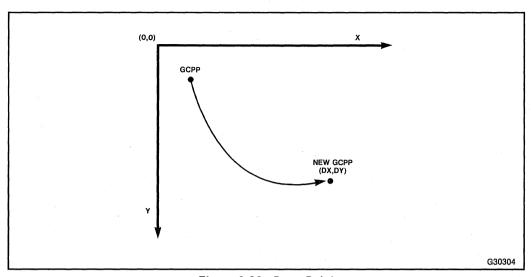

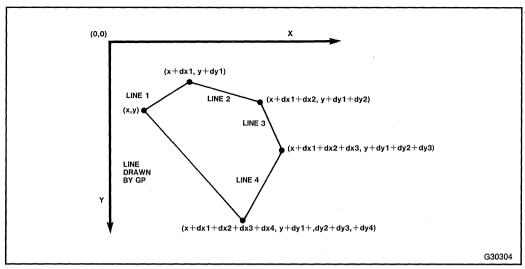

Any location in a bitmap can be referenced through a set of (x,y) coordinates. As shown in Figure 2-1, the 82786 uses a set of coordinates whose Origin Address begins at coordinates (0,0), located in the top left corner. The x axis extends across the top and increases to the right. The y axis extends down the left side and increases from top to bottom.

### **2.1.3 Pixels**

Most Graphics Processor (GP) commands manipulate a pixel or a group of pixels within a bitmap. A pixel is the smallest element that can be displayed on a CRT. A pixel can associate 1, 2, 4, or 8 bits with it. The number of bits per pixel (bpp) varies based on the attributes associated with the pixel. Although the attributes, hence the bpp, can vary, all pixels in the same bitmap must have the same number of bpp. Color and multiple gray scale displays require multiple bpp.

Figure 2-1. Bitmap Coordinates

All bitmaps are stored in memory in a sequential packed pixel manner. The 82786 stores pixels sequentially with as many pixels as possible in each 16-bit word. The number of pixels each word contains varies based on the number of bpp. For example, if the bitmap has 2 bpp, each word contains 8 successive pixels. Table 2-1 lists variations on the number of bpp and pixels per word.

| ВРР | Pixels Per Word |

|-----|-----------------|

| 1   | 16              |

| 2   | 8               |

| 4   | 4               |

| 8   | 2               |

Table 2-1. Bits Per Pixel (bpp) and Pixels Per Word

The GP stores each bitmap as a series of bits, which the GP and Display Processor (DP) interpret as a series of lines consisting of sequentially ordered pixels. Lines are arranged from top to bottom and contain pixels ordered from left to right. The first pixel of every bitmap is the top left-most pixel. Each bitmap starts at the Origin Address, coordinates (0,0), which must be an even byte address because the GP and Display Processor (DP) address words only. The contents of each word varies based on the bpp. In the 2-bpp model, the first word of the bitmap holds the value of the first 8 pixels of the first line, (coordinates (0,0), (1,0), (2,0), ... (7,0)). The next word represents the next 8 pixels of the first line, and so on until the end of the line. The word containing the first 8 pixels of the second line (coordinates (0,1), (1,1) (2,1) ... (7,1)) follows the word containing the pixels for the end of the first line. The 82786 stores all bitmaps in this manner.

### 2.1.4 Calculating the Effective Address (EA)

To calculate the effective address of a pixel, refer to the formula below. Table 2-2 defines all variables.

EA (Effective Address) = Bitmap Origin Address + ((x\*bpp) DIV 16) + y\*N

bnum (starting bit position) = 15 - (x\*bpp) MOD 16

Table 2-2. Effective Address Variables

| Variable                                                      | Definition                                                                                                             |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| bnum =                                                        | starting bit position of pixel (bnum = 0 is the least significant bit)                                                 |

| W =<br>H =<br>bpp =<br>(x,y) =<br>N (Memory words per line) = | Bitmap Width (in number of pixels) Bitmap Height (in number of pixels) Bits per Pixel Pixel Coordinates (W*bpp) DIV 16 |

Note: (W\*bpp) must be an integral multiple of 16. The Bitmap Origin Address must point to a word (even byte) address.

### 2.1.5 Windows

Windows consist of one or more tiles, which are portions of bitmaps output by the Display Processor (DP). Horizontally, the 82786 supports up to 16 tiles per displayed line. Vertically, the 82786 can support the same number of tiles as scan lines. A tile must be a subset of a single bitmap, which can contain the entire bitmap, but not portions of two or more bitmaps.

### 2.2 GRAPHICS PROCESSOR (GP) REGISTERS

The Graphics Processor (GP) uses three types of registers:

- GP 82786 Internal Registers

- GP Control Registers

- Context Registers

All GP registers are 16 bits wide. Each register contains either data or an address. A data register can use all or just a portion of the 16 bits in the register. When the register value does not require all 16 bits, the value is right justified in the word and the upper unused bits are zeroed to ensure future compatibility. An address register requires two consecutive words to contain a 22-bit address. An address always begins on an even byte. Address registers do not explicitly store the least significant bit, which is assumed to be 0. The first word contains the 16 least significant bits. The second word contains the remaining six bits with the upper ten bits zeroed for future compatibility. The following sections discuss GP registers in detail.

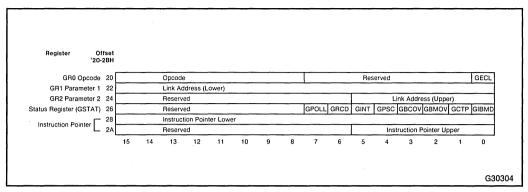

### 2.2.1 Internal Graphics Processor (GP) Registers

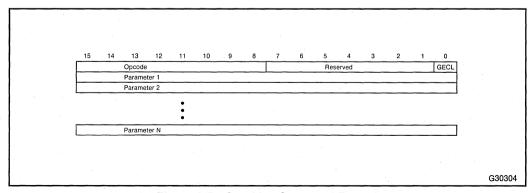

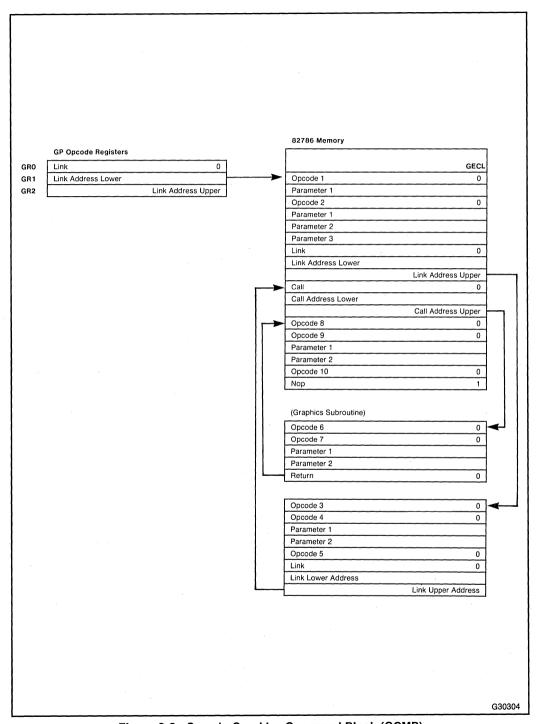

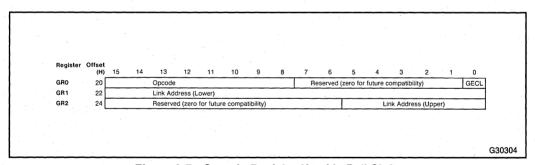

The Graphics Processor (GP) has six Internal Registers on the 82786 that are either I/O or memory mapped. The external CPU uses these registers to initiate execution of graphics command lists and record status. Unlike other GP registers, which must be read and written to with Load and Dump Register commands, these GP registers are directly addressable. They are located at Internal Register Block offsets 20h through 2Ah from the base address (see Figure 1-3). The base address marks the beginning of the Internal Register Block and is contained in the BIU Relocation Register described in Section 4.2.1. Figure 2-2 displays these GP Internal Register Block registers which include GR0, the Opcode Register at offset 20h; GR1 and GR2, the lower and upper values of the starting address of the next Graphics Command Block (GCMB) at offsets 22h and 24h (see Section 2.3 "Command Execution and Format" for details); the GP Status Register (GSTAT) at offset 26 (see Section 2.2.1.1

Figure 2-2. Graphics Processor Internal Registers

Figure 2-3. Graphics Processor Status Register

for details); and the Instruction Pointer (GCIP) at offsets 28h and 2Ah, (see Section 2.2.1.2 for details). These registers are word or byte addressable based on the setting of the BCP bit in the BIU Control Register described in Section 4.2.2 "Control Register."

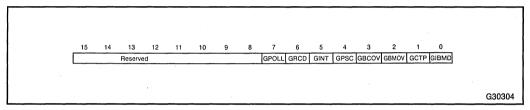

### 2.2.1.1 GRAPHICS PROCESSOR STATUS REGISTER (GSTAT)

The Graphics Processor Status Register (GSTAT) contains the Status Byte, shown in Figure 2-3. Table 2-3 describes the GSTAT bits, which start at offset 26h. All the status bits, except GPOLL are cleared upon RESET. The GPOLL bit is set on RESET as discussed in Section 2.3.3 "RESET and Initialization."

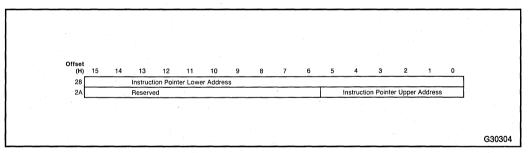

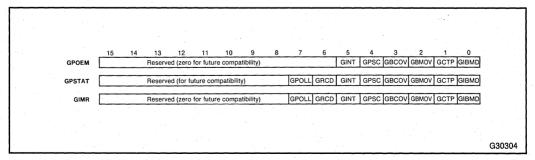

## 2.2.1.2 GRAPHICS PROCESSOR INSTRUCTION POINTER

The Graphics Processor Instruction Pointer (GCIP) points to the current command in the Graphics Command Block (GCMB). The GCIP consists of a 22-bit value stored in two 82786 Internal Registers (GCIPL and GCIPH) at Internal Register Block offsets 28h and 2Ah from the base address as shown in Figure 2-4. The base address marks the beginning of the Internal Register Block and is contained in the BIU Relocation Register described in Section 4.2.1.

Table 2-3. Graphics Processor Status Register Bits

| Bit   | Function                                                                                                                                                                                                                                                                                                                                   |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPOLL | Indicates if the Graphics Processor is in Poll State. See Section 2.3.2 "Poll State."                                                                                                                                                                                                                                                      |

| GRCD  | Set if the Graphics Processor encounters an illegal opcode.                                                                                                                                                                                                                                                                                |

| GINT  | The INTR_GEN command, described in Section 2.10.21, sets this bit, which can cause an interrupt if the value in the GINT bit in the Interrupt Mask Register (GIMR) is zero. For details on the GIMR, refer to Section 2.3.4 "Exception Handling."                                                                                          |

| GPSC  | Pick Successful Flag. Set or cleared while the Graphics Processor (GP) is in PICK Mode. Set if the Pick operation is successful on any command.                                                                                                                                                                                            |

| GBCOV | Bitmap Overflow. This flag is set when executing a Bitblt or Charblt command if any portion of the destination rectangle lies outside the clipping rectangle.                                                                                                                                                                              |

| GBMOV | Bitmap Overflow Flag for geometric commands. This flag is set when drawing a pixel lying outside the clipping rectangle as a result of any geometric drawing command (Line, Circle, etc.).                                                                                                                                                 |

| GCTP  | Character Trap. Indicates that a character had its Trap Bit set in the character string parameter of the Char command. This is useful in initiating error handling or special character handling routines such as those in which each character consists of multiple 16×16 pixel segments.                                                 |

| GIBMD | Illegal Bitmap Definition. Set if the Def_Bitmap command executes with illegal parameters. The illegal parameters are bits per pixel other than 1, 2, 4, 8, or Xmax defined to be greater than 32k-1. This bit should not be masked out in the Interrupt Mask (GIMR) to ensure the CPU is informed of this exception as soon as it occurs. |

Figure 2-4. Graphics Processor Instruction Pointer

# 2.2.2 Graphics Processor (GP) Control Registers

The Graphics Processor (GP) has four Control Registers in addition to the Internal Register Block registers:

| Register        | Mnemonic |

|-----------------|----------|

| Poll Mask       | GPOEM    |

| Interrupt Mask  | GIMR     |

| Stack Pointer   | GSP      |

| Character Count | GCNT     |

Table 2-4 lists the function and ID of each register.

Register ID Number of Bits Function **GPOEM** 0003 6 Poll Mask Six right justified bits in a 16-bit register corresponding to GSTAT bits: GINT, GPSC, GBCOV, GBMOV, GCTP, and GIBMD. If any GPOEM bits corresponding to set GSTAT bits have a value of zero, the GP enters Poll State. **GIMR** 0004 8 Interrupt Mask Eight right justified bits in a 16-bit register corresponding to GSTAT bits: GPOLL, GRCD, GINT, GPSC, GBCOV, GBMOV, GCTP, and GIBMD. The GP generates an interrupt if any GIMR bits corresponding to set GSTAT bits have a value of 0. 010C **GSP** 21 Stack Pointer The 21-bit address contained in two consecutive words points to the current top of stack. The stack grows toward lower addresses. **GCNT** 0015 16 Contains the character count while drawing characters in the bitmap.

Table 2-4. Graphics Processor Control Registers

The registers in Table 2-4 can be read from or written to with the Dump\_Reg (Section 2.10.15) and Load\_Reg (Section 2.10.24) commands. Each register is identified by a 9-bit Register ID, which is right justified in the lower nine bits of a 16-bit word in which the upper bits are zeroed.

GPOEM, GIMR, and GCNT are data registers, which always store their values right justified in a 16-bit word of memory in which the upper unused bits are zeroed. The Stack Pointer (GSP) requires two consecutive words of memory to hold its 22-bit address. The first word contains the lower 16 bits; the second word contains the six most significant bits in bits 0 through 5 with the remaining upper bits zeroed. The stack grows down toward lower addresses.

## 2.2.3 Graphics Processor (GP) Context Registers

The Graphics Processor (GP) also uses context registers, which should not be accessed normally, but must be saved and restored if the GP is to be shared by multiple processes. Any other access to these registers should be avoided. Table 2-5 lists these registers, their IDs, and the number of bits each uses. A register using 16-bits or less stores its value in a 16-bit word. If the register does not require the entire 16 bits, the value is right justified in the word and the upper bits are zeroed, unless noted otherwise. A register with a value larger than 16 bits uses two consecutive 16-bit words of memory. The first word contains the lower 16 bits and the second word contains the upper bits with any remaining bits zeroed.

**Table 2-5. Context Registers**

| Name     | ID   | Bits   | Function                                        |  |  |  |  |  |

|----------|------|--------|-------------------------------------------------|--|--|--|--|--|

| GCOMM    | 0002 | (16)   | Command                                         |  |  |  |  |  |

| GPOEM    | 0003 | (6)    | Poll Mask                                       |  |  |  |  |  |

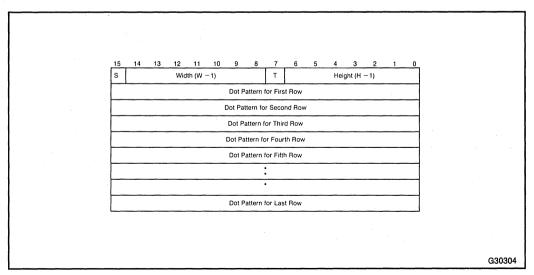

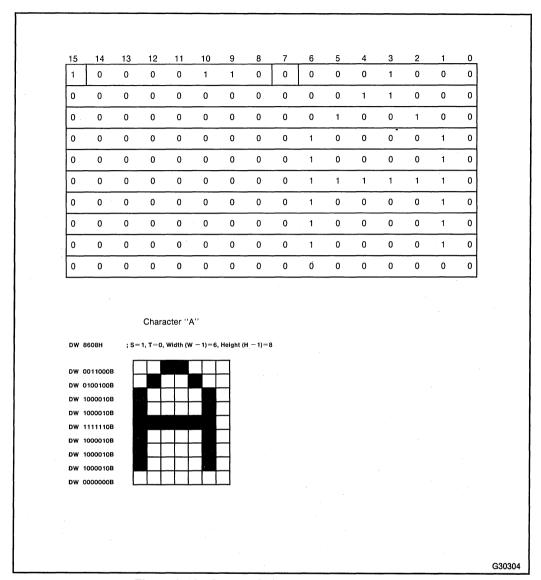

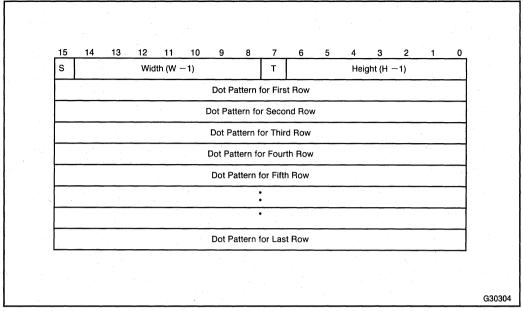

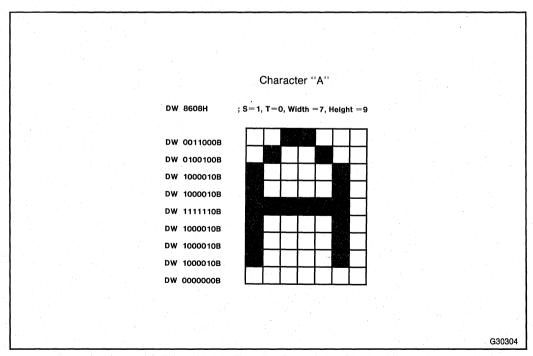

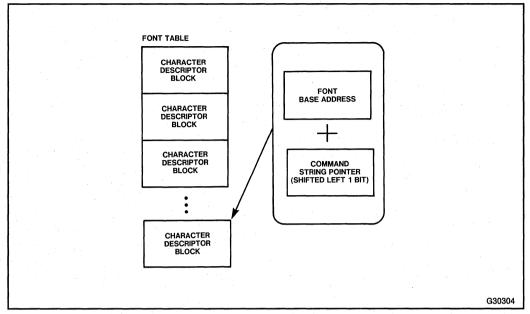

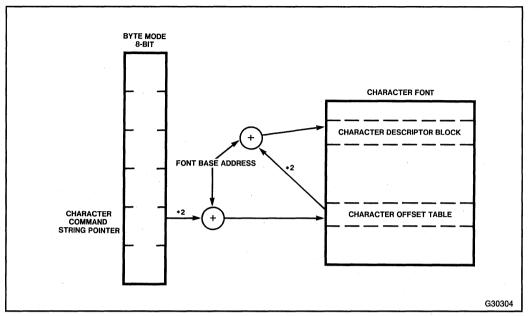

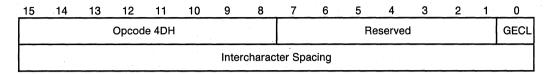

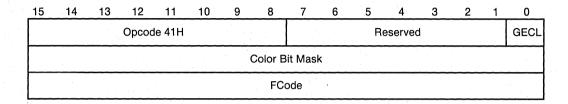

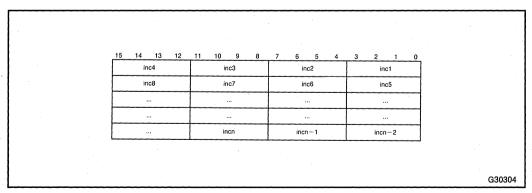

| GIMR     | 0004 | (6)    | Interrupt Mask                                  |  |  |  |  |  |