# iSBC® 028CX, 056CX, 012CX, 010CX AND 020CX iLBX™ RAM BOARDS

- Dual port capability via MULTIBUS® and iLBX™ Interfaces

- Single bit error correction and double bit error detection utilizing Intel 8206 ECC device

- 128K byte, 256K byte, 512K byte, 1024K byte, and 2048K byte versions available

- Control status register supports multiple ECC operating modes

- Error status register provides error logging by host CPU board

- 16 megabyte addressing capability

- Supports 8- or 16-bit data transfer and 24-bit addressing

- Auxilliary power bus and memory protect logic for battery back-up RAM requirements

The iSBC® 028CX, iSBC 056CX, iSBC 012CX, iSBC 010CX, and iSBC 020CX RAM memory boards are members of Intel's complete line of iSBC memory and I/O expansion boards. Each board interfaces directly to any iSBC 80, iSBC 86, iSBC 186 and iSBC 286 Single Board Computers. The dual port feature of the CX series of RAM-boards allows access to the memory of both the MULTIBUS® and iLBX™ bus interfaces.

In addition to the dual port features the "CX" series of RAM-boards provide Error Checking and Corrections Circuitry (ECC) which can detect and correct single bit errors and detect, but not correct, double and most multiple bit errors.

The iSBC 028CX, iSBC 056CX, and iSBC 012CX boards contain 128K, 256K, and 512K bytes of read/write memory using 64K dynamic RAM components. The iSBC 010 CX and iSBC 020 CX boards contain 1024K and 2048K bytes of read/write memory using 256K dynamic RAM components.

Due to the iLBX dual port capability and on-board ECC features of the boards they are ideally suited in applications where memory performance and integrity is critical, such as financial transactions, process control and medical equipment applications.

The following are trademarks of Intel Corporation and may be used only to describe Intel products: Intel, ICE, iMMX, iRMX, iSBC, iSBX, iSXM, MULTIBUS, Multichannel and MULTIMODULE. Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supercedes previously published specifications on these devices from Intel.

© INTEL CORPORATION, 1983

February, 1984 Order Number: 231023-001

#### **FUNCTIONAL DESCRIPTION**

#### General

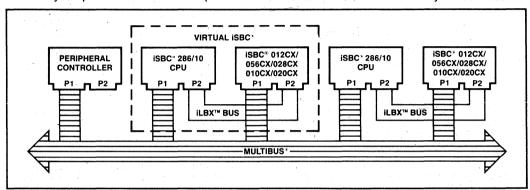

The iSBC 028CX, 056CX, 012CX, 010CX and 020CX RAM boards are physically and electrically compatible with the MULTIBUS interface standard, IEEE-796, as outlined in the Intel MULTIBUS specification. In addition the CX series of RAM-boards are physically and electrically compatible with the iLBX bus (Local Bus

Extension) interface as outlined in the Intel iLBX Specification (see Figure 1).

## **Dual Port Capabilities**

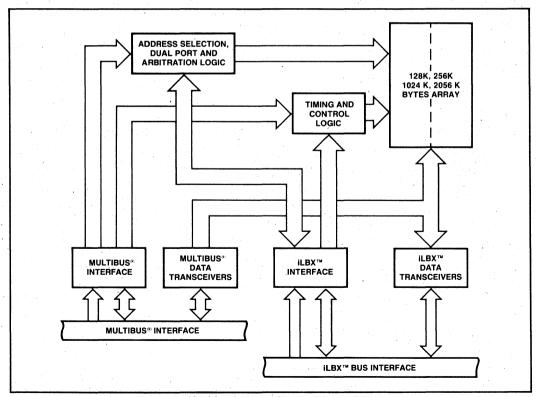

The "CX" series of RAM-boards can be accessed by either the MULTIBUS interface or the iLBX interface (see Figure 2). Intel's iLBX interface is an unarbitrated bus architecture which allows direct transfer of data between the CPU and the memory boards without ac-

Figure 1. Typical iLBX™ System Configuration

Figure 2. iSBC® 028CX/056CX/012CX Block Diagram

cessing the MULTIBUS bus. Due to the unarbitrated nature of the iLBX interface significant improvements in memory access times result, typically a 2-6 Wait State improvement over MULTIBUS memory access.

# **System Memory Size**

Maximum system memory size with this series of boards is 16 megabytes. Memory partitioning is independent for the MULTIBUS interface and the iLBX interface.

For MULTIBUS operations, on-board jumpers assign the board to one of four 4-megabyte pages. Each page is partitioned into 256 blocks of 16K bytes each. The smallest partition on any board in this series is 8K bytes. Jumpers assign the base address (lowest 16K block) within the selected 4-megabyte page.

The iLBX bus memory partitioning differs from the MULTIBUS bus partitioning in that the iLBX bus address space consists of 256 contiguous blocks of 64K bytes totaling 16 megabytes. As with the MULTIBUS bus partitioning, the base addresses are set with onboard jumpers.

# **Error Checking and Correcting (ECC)**

Error checking and correction is accomplished with the Intel 8206 Error Checking and Correcting device. This ECC component, in conjunction with the ECC check bit RAM array, provides error detection and correction of single bit errors and detection only of double bit and most multiple bit errors. The ECC circuitry can be programmed via the Control Status Register (CSR) to various modes while error logging is supported by the Error Status Register (ESR). Both CSR and ESR communicate with the master CPU board through a single I/O port.

#### **ECC I/O Address Selection**

The processor board communicates with the ECC circuitry via a single I/O port. This port is used for the Control Status Register (CSR) and the Error Status Register (ESR). The CSR is programmed by the user to determine the mode of operation while the ESR provides information about memory errors.

The iSBC 028CX, iSBC 056CX, iSBC 012CX, iSBC 010CX, and iSBC 020CX RAM boards are shipped with a Programmed Array Logic (PAL) device which allows selecting one of 9 possible addresses for the I/O port. The actual selection is done by jumper configuration. Additional unprogrammed locations are left in the PAL to allow application specific I/O addresses to be defined.

#### **CONTROL STATUS REGISTER**

There are six ECC modes of operation in the "CX" family of RAM boards. Each mode is obtained by soft-

ware programming of the CSR from the master iSBC board. The six modes are:

- a. Interrupt on any error mode

- b. Interrupt on non-correctable error only mode

- c. Correcting mode

- d. Non-correcting mode

- e. Diagnostic mode

- f. Examine syndrome word mode

Modes (a) and (b) can be used in conjunction with (c) and (d). The six modes are described below.

Interrupt on Any Error Mode — In this mode the RAM board will interrupt the iSBC processor board when any error (single bit or multiple bit) is detected by the ECC circuitry.

Interrupt on Non-Correctable Error Mode — In this mode the RAM board will interrupt the iSBC processor board only when a non-correctable (multiple bit) error is detected by the ECC circuitry. A multiple bit error is not correctable by the ECC circuitry.

Correcting Mode — In this mode the RAM board corrects any correctable error (single bit error). Errors which are not correctable are not modified. Interrupts are generated depending on the interrupt mode selected.

Non-Correcting Mode — In this mode the RAM board does not correct any error. The ECC circuitry continues to check for errors, but no corrective action is taken. Interrupts continue as described previously.

Diagnostic Mode — This mode is used for testing the on-board ECC circuitry. In this mode the write enable strobe to the ECC RAM array is continuously disabled. The diagnostic mode can be used to simulate errors and in conjunction with the "Examine Syndrome Word Mode" examine the check bits generated by the ECC circuitry.

Examine Syndrome Word Mode — This mode, in conjunction with the diagnostic mode, is used for testing the ECC memory. In this mode, the syndrome bits/ check bits are clocked into the ESR on every memory read/write cycle, respectively. The ESR translation PROM switches to a transparent mode in the examine syndrome word mode. This allows the actual syndrome word generated by the 8206 ECC device to be examined.

#### **ERROR STATUS REGISTER**

This 8-bit register contains information about memory errors. The ESR reflects the latest error occurence. Table 1 shows the status register format. Bits 5 and 6 show the failing row while bits 0 through 4 indicate which bit (of the 16-bit data word or the 6-bit ECC syndrome) is in error. Bit 7 is always high.

| Table 1. Error Status Register Cimiat |       |     |                                          |   |     |     |     |     |     |                      |

|---------------------------------------|-------|-----|------------------------------------------|---|-----|-----|-----|-----|-----|----------------------|

|                                       | Bit   | •   | en e |   |     |     | Bit |     |     |                      |

|                                       | 6 5   |     | Meaning                                  |   | 4   | 3   | 2   | 1   | 0   | Meaning              |

|                                       | 0 0   |     | Error in row                             | 0 | 0   | 1   | 0   | 1   | 0   | Error in data bit 10 |

|                                       | 0 1   |     |                                          | 1 | 0   | 1   | 0   | 1   | 1   | 11                   |

|                                       | 1 0   |     |                                          | 2 | 0   | _1  | 1   | 0   | 0   | . 12                 |

|                                       | 1 1.  |     |                                          | 3 | 0   | 1   | 1   | 0   | 1   | 13                   |

|                                       |       |     |                                          |   | 0   | 1   | 1   | 1   | 0   | 14                   |

|                                       | Bit   | 1.0 | Meaning                                  |   | 0   | . 1 | 1   | 1   | 1   | <b>15</b>            |

| 4                                     | 3 2 1 | 0   | arang kalendaran Majabat                 |   | · 1 | Ω   | 0   | 0   | 0   | Error in check bit 0 |

| 0                                     | 0 0 0 | 0   | Error in data bit                        | 0 | - 1 | ň   | ñ   | ñ   | 1   | 1                    |

| 0                                     | 0 0 0 | 1   |                                          | 1 | 1   | Ŏ   | Õ   | 1   | Ó   | 2                    |

| 0                                     | 0 0 1 | 0   |                                          | 2 | 1   | Ŏ   | Ō   | - 1 | 1   | $ar{3}$              |

| 0                                     | 0 0 1 | 1   |                                          | 3 | 1   | 0   | 1   | Ó   | 0   | <b>4</b>             |

| 0                                     | 0 1 0 | 0   |                                          | 4 | 1   | Ŏ   | -1  | ō   | 1   | 5                    |

| 0                                     | 0 1 0 | 1 . |                                          | 5 |     |     |     |     | ^   | No Cine              |

| 0                                     | 0 1 1 | 0   |                                          | 6 | 1   | 1   | 1   | 1   | . 0 | No Error             |

| 0                                     | 0 1 1 | 1   | ***                                      | 7 | 1   | 1   | . 1 | 1   | 1 1 | Non-correctable      |

| 0                                     | 1 0 0 | . 0 | 1.0                                      | 8 |     |     |     |     |     | (multiple-bit error) |

9

Table 1. Error Status Register Format

# **Battery Back-up/Memory Protect**

0

An auxillary power bus is provided to allow separate power to the RAM array for systems requiring backup of read/write memory. An active low TTL compatible

memory protect signal is brought out on the auxillary bus connector which, when asserted, disables read/write access to the RAM board. This input is provided for the protection of RAM contents during system power-down sequences.

#### **SPECIFICATIONS**

# **Word Size Supported**

8- or 16-bits

#### **Memory Size**

131,072 bytes (iSBC 028CX board) 262,144 bytes (iSBC 056CX board) 524,288 bytes (iSBC 012CX board) 1,048,576 bytes (iSBC 010CX board) 2,097,152 bytes (iSBC 020CX board)

#### Access Times (All densities)

**MULTIBUS® System Bus**

Read/Full Write - 380 ns (max)

Write Byte - 530 ns (max)

iLBX™ Local Bus

Read/Full Write - 340 ns (max)

Write Byte - 440 ns (max)

**Cycle Times (All densities)**

**MULTIBUS®** System Bus

Read/Full Write - 490 ns (max)

Write Byte - 885 ns (max)

iLBX<sup>™</sup> Local Bus

Read/Full Write - 375 ns

Write Byte - 740 ns

NOTE: If an error is detected, read access time and cycle times are extended to 255 ns (max)

#### **Memory Partitioning**

Maximum System memory size is 16M Bytes for both MULTIBUS and iLBX BUS. MULTIBUS partitioning is by Page, Block and Base, while the iLBX BUS is by Block and Base only.

## **Page Address**

MULTIBUS® — 0-4 megabytes; 4-8 megabytes, 8-12 megabytes; 12-16 megabytes

ILBX™ BUS - N/A

## **Base Address**

MULTIBUS® System Bus — Any 16K byte boundary within the 4M-byte page.

iLBX™ Local Bus — Any 64K byte boundary selectable on board boundaries to 8M-bytes and some 64K-byte boundaries in the first megabyte. Others available if PAL programming is changed.

# **Power Requirements**

Voltage - 5 VDC ± 5%

| Product     | Current     | Standby<br>(Battery Back-up) |

|-------------|-------------|------------------------------|

| iSBC® 028CX | 3.8A (typ.) | 2.0A (typ.)                  |

| Board       | 6.5A (max.) | 2.1A (max.)                  |

| iSBC® 056CX | 4.0A (typ.) | 2.1A (typ.)                  |

| Board       | 6.6A (max.) | 2.2A (max.)                  |

| iSBC® 012CX | 4.4A (typ.) | 2.2A (typ.)                  |

| Board       | 6.8A (max.) | 2.4A (max.)                  |

| iSBC® 010CX | 4.8A (typ.) | 2.1A (typ.)                  |

| Board       | 7.0A (max.) | 2.3A (max.)                  |

| iSBC® 020CX | 5.3A (typ.) | 2.2A (typ.)                  |

| Board       | 7.5A (max.) | 2.4A (max.)                  |

# **Environmental Requirements**

**Operating Temperature** — 0°C to 55°C airflow of 200 linear feet per minute

Operating Humidity - To 90% without condensation

# **Physical Dimensions**

Width — 30.48 cm (12 inches)

**Height** — 17.15 cm (6.75 inches)

Thickness — 1.27 cm (0.50 inches)

**Weight** — iSBC 028CX board: 4699 gm (16.7 ounces); iSBC 056CX board: 5329 gm (19.0 ounces); iSBC 012CX board: 6589 gm (23.5 ounces); iSBC 010CX board: 5329 gm (19.0 ounces); iSBC 020CX board: 6589 gm (23.5 ounces)

## **Reference Manuals**

145158-003 — iSBC® 028CX/iSBC® 056CX/iSBC® 012CX Hardware Reference Manual

144456-001 — Intel iLBX™ 010CX, 020CX Specification

9800683-03 — Intel MULTIBUS® Specification

Manuals may be ordered from any Intel Sales Representative, Distributor Office or from the Intel Literature Department, 3065 Bowers Avenue, Santa Clara, CA. 95051

## ORDERING INFORMATION

| Part Number | Description                                       |

|-------------|---------------------------------------------------|

| iSBC® 012CX | 512K byte RAM board with ECC and iLBX™ Connectors |

| iSBC® 056CX | 256K byte RAM board with ECC and iLBX™ Connectors |

| iSBC® 028CX | 128K byte RAM board with ECC and iLBX™ Connectors |

| iSBC® 010CX | 1M byte RAM board with ECC and iLBX™ Connectors   |

| iSBC® 020CX | 2M byte RAM board with ECC and iLBX™ Connectors   |