# **Table of Contents**

| 1 | Introduction |  |  |  |  |  |  |  |

|---|--------------|--|--|--|--|--|--|--|

|---|--------------|--|--|--|--|--|--|--|

## **2** Data Sheets

|   | iSBX <sup>™</sup> 344 BITBUS <sup>™</sup> Controller MULTIMODULE <sup>™</sup> Board | . 1 |

|---|-------------------------------------------------------------------------------------|-----|

| _ | iRCB 44/10 BITBUS™ Remote Controller Board                                          | 10  |

|   | iRMX™ 51 Real-Time Multitasking Executive                                           | 20  |

| _ | iRMX™ 510 iDCM Support Package                                                      | .26 |

|   | 8084AH/8344AH High Performance 8-Bit Microcontroller with                           |     |

|   | On-Chip Serial Communication Controller                                             | 30  |

## 3 The BITBUS™ Interconnect Serial Control Bus Specification

| - | 1.0 General                          | 51 |

|---|--------------------------------------|----|

|   | 1.1 Scope                            | 51 |

|   | 1.2 Definitions                      | 51 |

| - | 2.0 Functional Overview              | 2  |

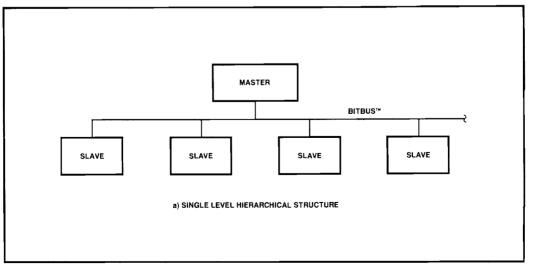

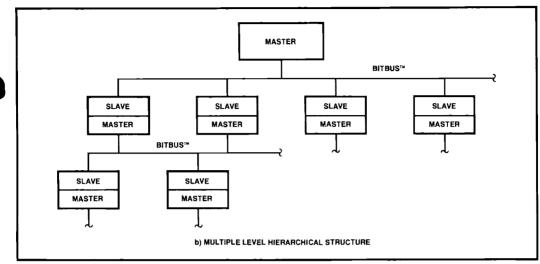

|   | 2.1 Hierarchical Model5              | 2  |

|   | 2.2 Bus Elements                     | 53 |

|   | 2.3 Modes of Operation               | 54 |

|   | 2.4 Levels of Specification          | 57 |

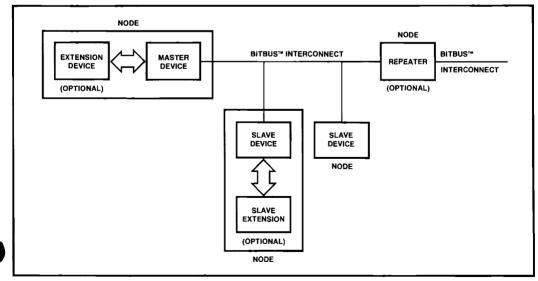

| - | 3.0 Electrical Specification         | 8  |

|   | 3.1 Data Encoding Techniques5        | 8  |

|   | 3.2 DC Specifications                | 0  |

|   | 3.3 AC Specifications                | 5  |

|   | 4.0 Data Link Protocol Specification | ;9 |

|   | 4.1 System State                     |    |

|   | 4.2 Frame Format                     | 0  |

|   | 4.3 Control Field Definition7        | '1 |

|   | 4.4 Data Link Operation              |    |

| - | 5.0 Message Protocol                 | '9 |

|   | 5.1 Order/Reply Structure            |    |

|   | 5.2 Message Format                   | 30 |

| - | 6.0 Remote Access and Control        |    |

|   | 6.1 Message Format For RAC           | 32 |

|   | 6.2 RAC Commands                     | 32 |

|   | 6.3 RAC Responses                    | 38 |

|   | 7.0 Mechanical Specification         | 39 |

|   | 7.1 Connector Specification          | 39 |

|   | 7.2 I/O Board Specification9         | )1 |

| - | 8.0 Levels of Compliance             | )5 |

|   | 8.1 Concept of Level of Compliance9  |    |

|   | 8.2 Compliance Levels                | 96 |

## FIGURES

| TITLE PA                                                             | GE |

|----------------------------------------------------------------------|----|

| Figure 1a. BITBUS™ Interconnect Hierarchy                            | 52 |

| Figure 1b. BITBUS™ Interconnect Hierarchy                            | 53 |

| Figure 2. BITBUS™ Interconnect Elements                              | 53 |

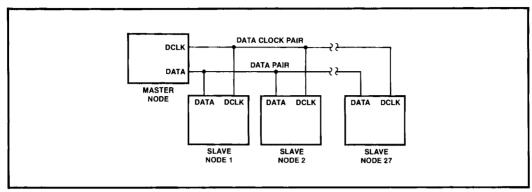

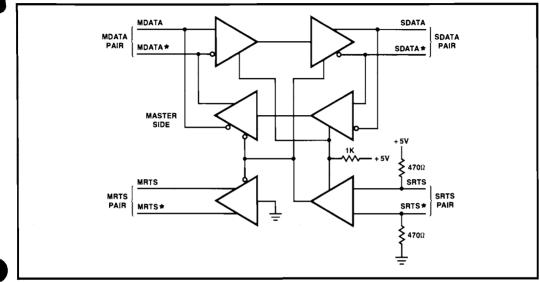

| Figure 3. Synchronous Mode Connection                                | 55 |

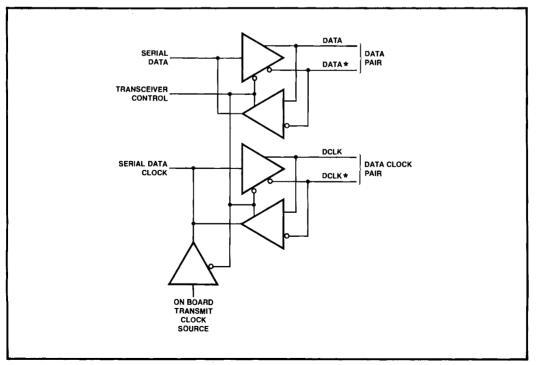

| Figure 4. Typical Synchronous Mode Interface                         | 55 |

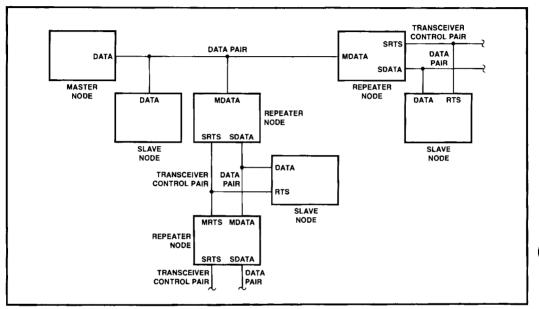

| Figure 5. Self Clocked Mode Connection                               | 56 |

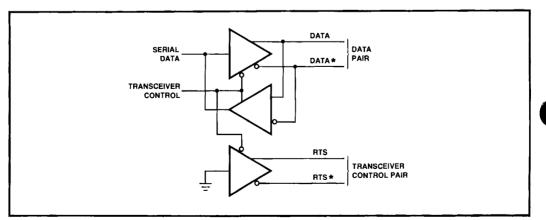

| Figure 6. Typical Self Clocked Mode Interface                        | 56 |

| Figure 7. Typical Repeater                                           | 57 |

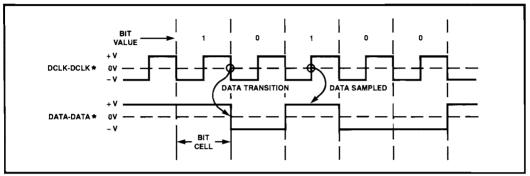

| Figure 8. Synchronous Mode Data Encoding                             | 59 |

| Figure 9. Self Clocked Mode Data Encoding (NRZI)                     | 59 |

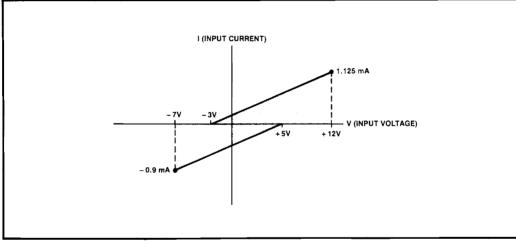

| Figure 10. Standard Unit Load                                        | 60 |

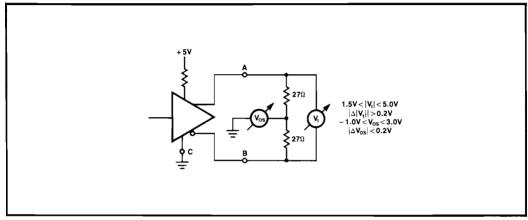

| Figure 11. Transmitter Open Circuit Test Configuration               | 61 |

| Figure 12. Transmitter Test Termination Configuration 1              | 62 |

| Figure 13. Transmitter Test Termination Configuration 2              | 62 |

| Figure 14. Transmitter Fault Conditions                              | 63 |

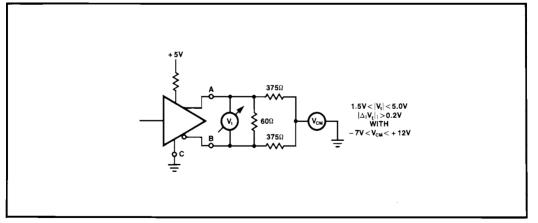

| Figure 15. Receiver Sensitivity Specification                        | 63 |

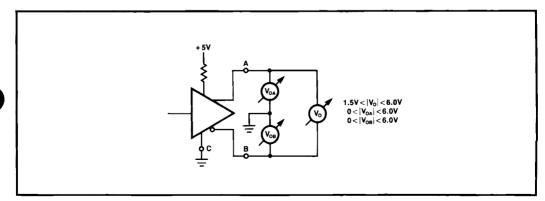

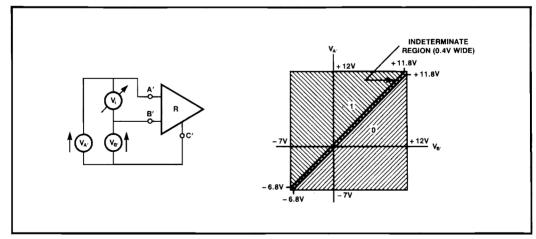

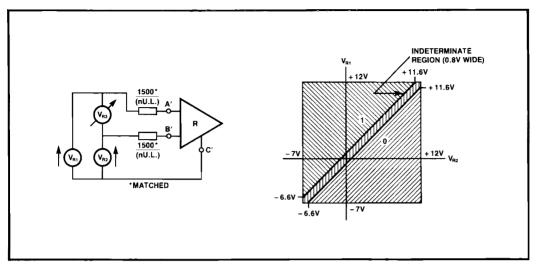

| Figure 16. Receiver Balance Specification                            | 64 |

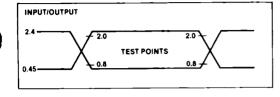

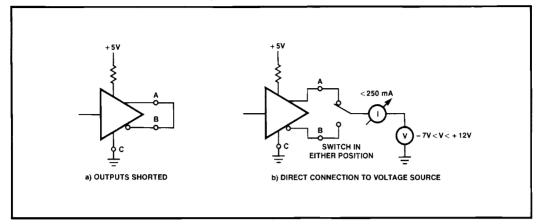

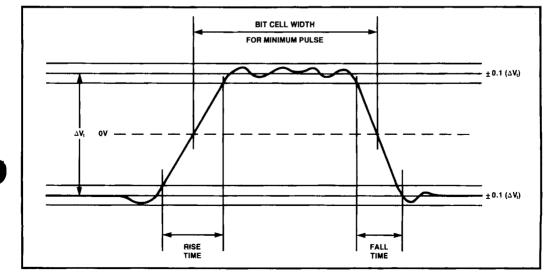

| Figure 17. Rise and Fall Time Specification                          | 65 |

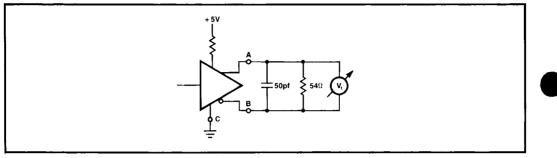

| Figure 18. Test Configuration for Rise and Fall Time Measurement.    | 66 |

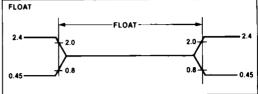

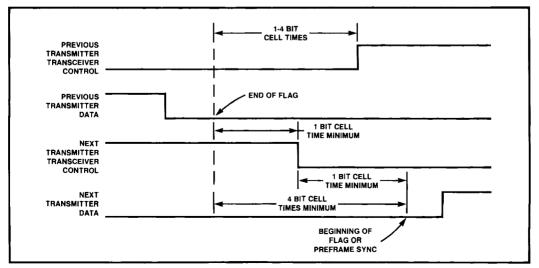

| Figure 19. Transmitter Enable Timing                                 | 66 |

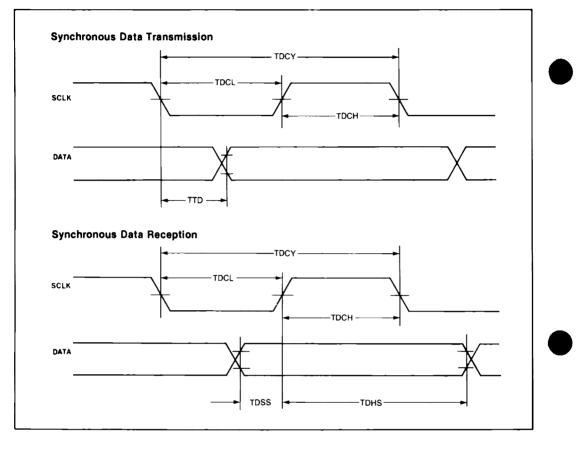

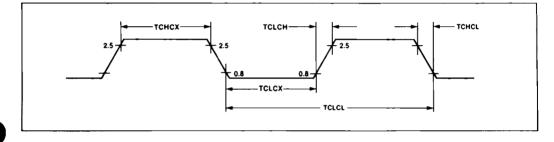

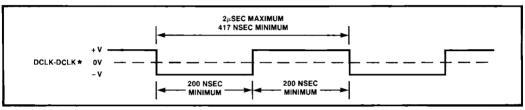

| Figure 20. Data Clock Signal Pair Specification for Synchronous Mode | 67 |

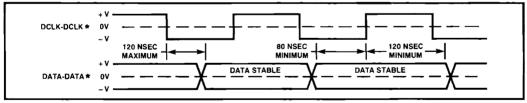

| Figure 21. Data Signal Pair Specification for Synchronous Mode       | 67 |

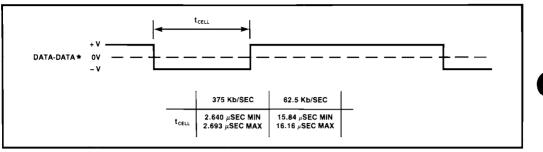

| Figure 22. Data Signal Pair Specification for Self Clocked Mode      | 68 |

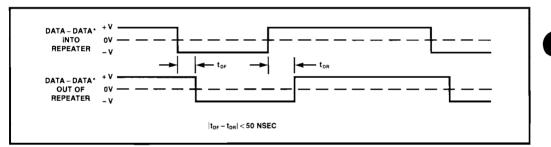

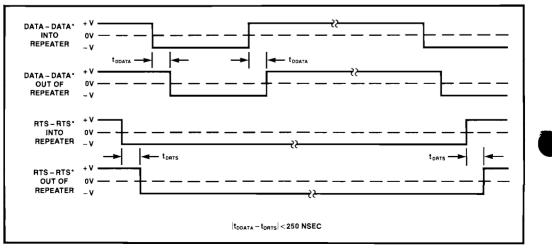

| Figure 23. Repeater Skew on Transitions                              | 68 |

| Figure 24. Repeater Skew Between Signal Pairs                        | 68 |

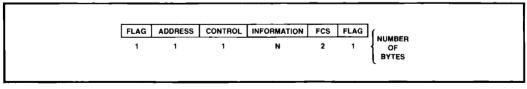

| Figure 25. Standard Frame Format                                     | 70 |

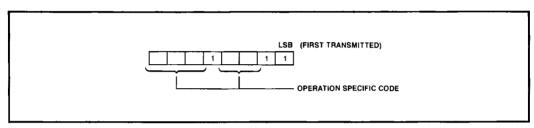

| Figure 26. Unnumbered Control Field Format                           | 72 |

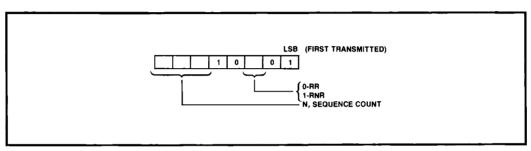

| Figure 27. Supervisory Control Field Format                          | 73 |

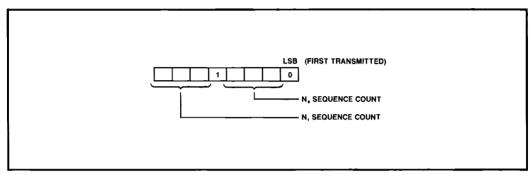

| Figure 28. Information Control Field Format                          | 74 |

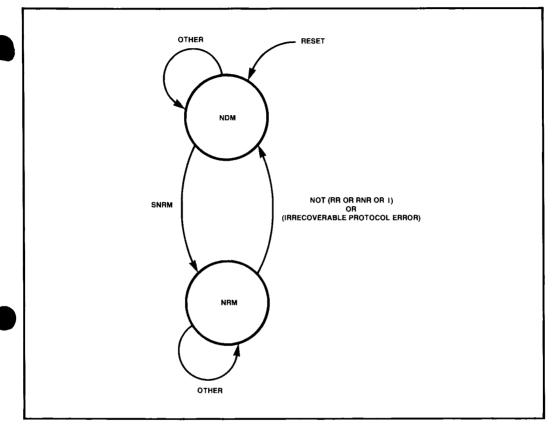

| Figure 29. Slave Device State Diagram                                | 75 |

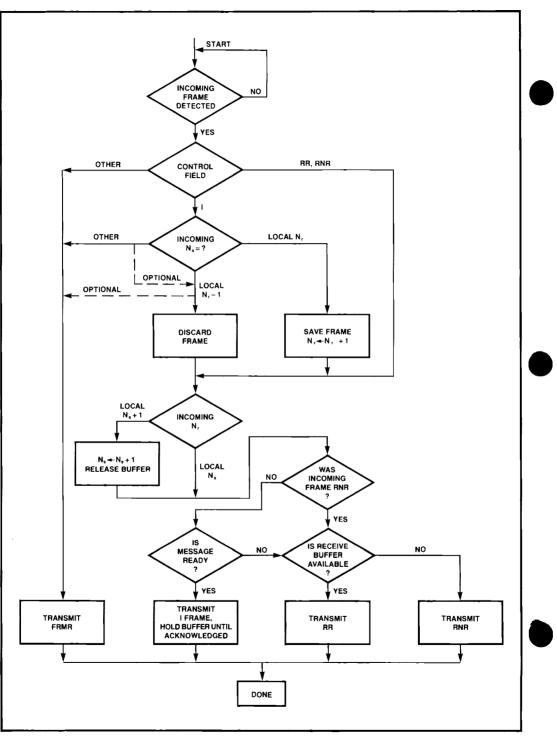

| Figure 30. Slave Response to Incoming Frame in NRM                   | 76 |

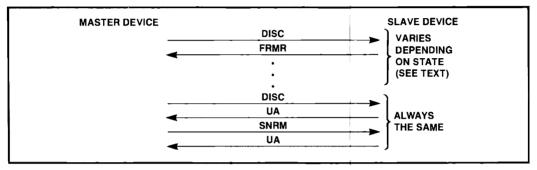

| Figure 31. Typical Initialization Sequence                           | 77 |

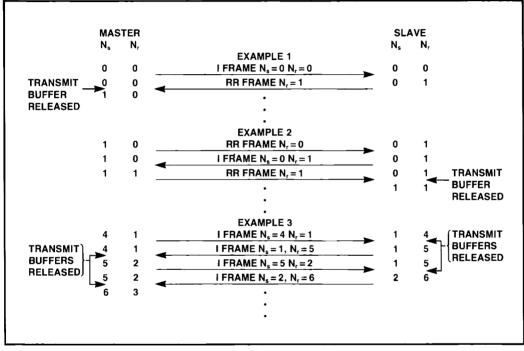

| Figure 32. Transfer Sequence Examples                                | 78 |

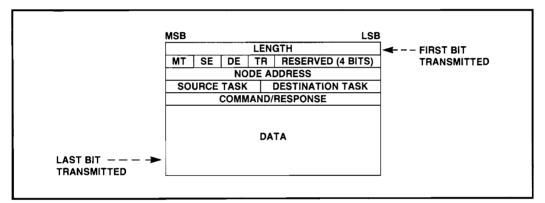

| Figure 33. Message Format                                            | 80 |

| Figure 34. GET Function ID Reply Example                             | 84 |

## FIGURES (Con't)

| T | ľ | I | Ľ | E |

|---|---|---|---|---|

|---|---|---|---|---|

#### PAGE

| Figure 35. Data Field Format for Memory Commands | 85 |

|--------------------------------------------------|----|

| Figure 36. Data Field Format for I/O Commands    | 86 |

| Figure 37. Data Field Format for Status Commands | 88 |

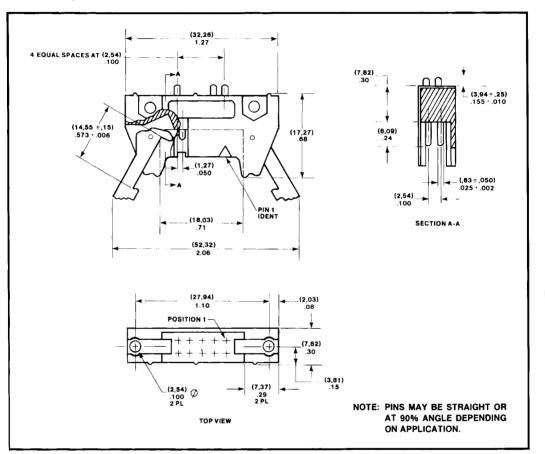

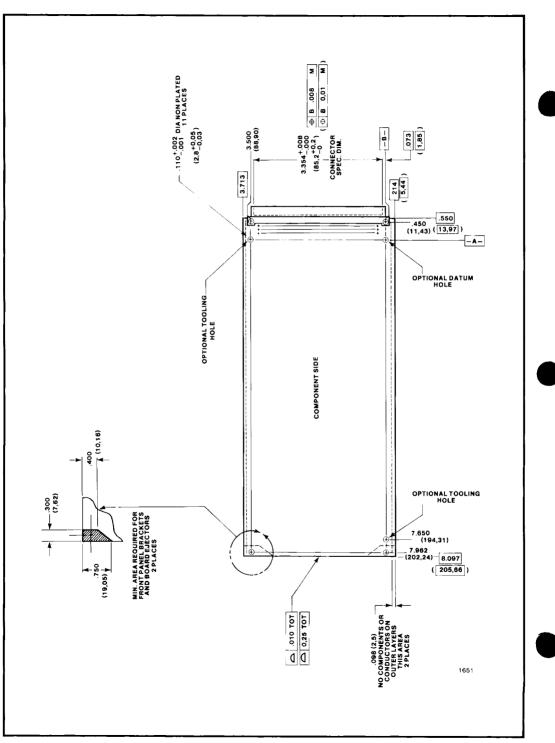

| Figure 38. Printed Board Connector               | 90 |

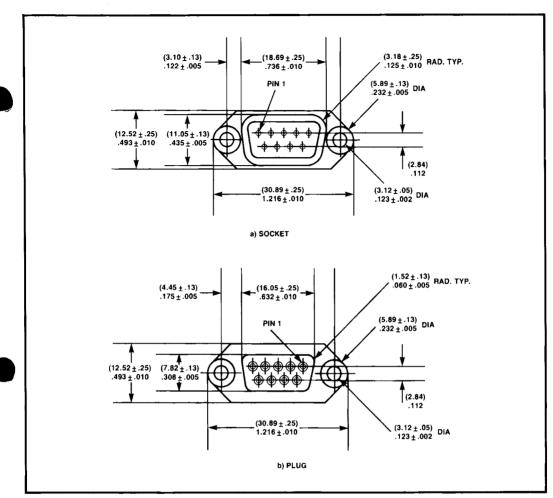

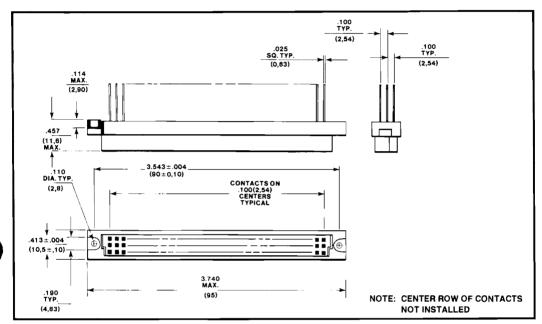

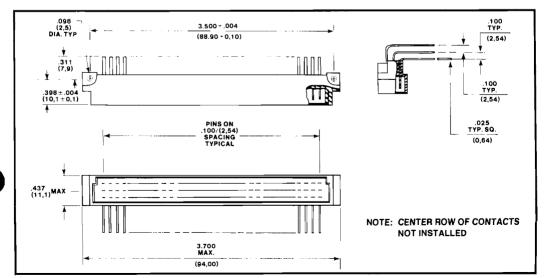

| Figure 39. Cable to Cable Connector              | 91 |

| Figure 40. Standard Board Dimensions             | 92 |

| Figure 41. Board Connector                       | 93 |

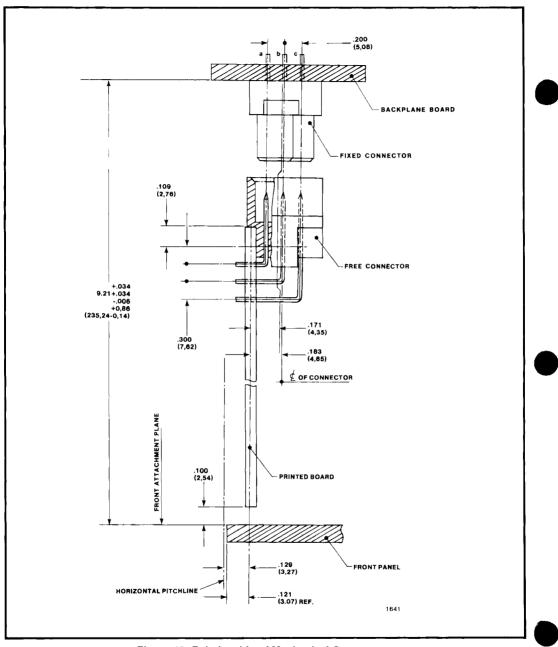

| Figure 42. Backplane Connector                   | 93 |

| Figure 43. Relationship of Mechanical Components | 94 |

## TABLES

#### TITLE PAGE Table 1. Number of Repeaters..... 69 Table 2. Unnumbered Control Fields..... 72 Table 3. Slave Device State Transitions and Responses..... 75 Table 4. Message Protocol Responses 81 Table 5. RAC Commands..... 83 Table 6. Function ID Code Assignments..... 84 Table 7. RAC Error Responses 89 Table 8. Connector Pin Assignments..... 90 Table 9. I/O Board Pin Assignment 95

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BITBUS             | iLBX                   | iPDS            | Plug-A-Bubble |

|--------------------|------------------------|-----------------|---------------|

| COMMputer          | im                     | iPSB            | Prompt        |

| CREDIT             | iMMX                   | iRMX            | Promware      |

| Data Pipeline      | Insite                 | iSBC            | QUEX          |

| GENIUS             | Intel                  | iSBX            | QUEST         |

| A                  | intel                  | iSDM            | Ripplemode    |

| i                  | intelBOS               | iSSB            | RMX/80        |

| I <sup>2</sup> ICE | Intelevision           | iSXM            | RUPI          |

| ICE                | Inteligent Identifier  | Library Manager | Seamless      |

| iCS                | Inteligent Programming | MCS             | SOLO          |

| iDBP               | Intellec               | Megachassis     | SYSTEM 2000   |

| iDIS               | Intelink               | MICROMAINFRAME  | UPI           |

|                    | iOSP                   | MULTIBUS        |               |

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

## Introduction to the Distributed Control Modules

#### Overview

Intel's Distributed Control Module (iDCM) products provide building blocks for construction of realtime distributed control systems based on the BITBUS<sup>™</sup> interconnect. This new serial bus architecture addresses many of the limitations inherent in traditional connection methods. For instance, future system cost reductions are limited in systems based on parallel bus structures due to their electrical and mechanical characteristics. Other traditional connection methods such as current loops and RS 232 C do not provide sufficient performance or flexibility for complex industrial control applications. In addition, although there are numerous industry standards for connecting microprocessors, the MULTIBUS<sup>®</sup> and the STD-bus for example, there is no standard connection for microcontrollers. The BITBUS interconnect (Table 1) combines existing standards with new standard interfaces to provide the optimal solution for difficult distributed control problems.

The iDCM products combine hardware and software for use in applications that would benefit most from employing distributed architectures. Applications such as robotics, process control, data acquisition and control, and environmental control are a few examples.

| Interface                 | Specification                                                 |

|---------------------------|---------------------------------------------------------------|

| Electrical                | RS485                                                         |

| Cable                     | 10-conductor flat ribbon or 1 to 2 wire twisted pair          |

| Back-plane connector      | 64-pin Standard DIN                                           |

| End-cable connector       | 3M #3446-1302 female                                          |

| Control-board form-factor | Single-height, Double-depth<br>Eurocard                       |

| Data Link control         | Synchronous Data-link Control                                 |

| Data transfer rate        | 62.5K baud, 375K baud and 2.4M baud                           |

| Message formats           | Compatible with iRMX 51 format command/response/status        |

| Common command sequences  | Integral Remote Access and<br>Control (RAC) function          |

| Operating systems         | S/W drivers for iRMX 86, 88,<br>286R and ISIS (for iPDS only) |

#### Table 1. Standard BITBUS™ Interfaces

#### **Benefits of Distributed Architectures**

Distributed architectures are intrinsically more reliable than centralized architectures. In a centralized control system a central controller failure results in a system-wide failure. Distributed systems can be configured to prevent this. Also, distributed systems are more cost effective and more easily modified. For instance, performance improvements in centralized systems are expensive and do not concentrate improvements in the areas where they are needed most. In distributed systems, only the specific parts of the system that require enhancement need be modified. Most importantly, control systems based on distributed architectures have less difficulty responding to the external environment because they have less to manage.

## \_\_\_\_\_

The BITBUS™ Interconnect

int

The BITBUS interconnect is a serial bus optimized for high speed transfer of short control messages in a hierarchical system. In order to provide an easy to use high performance serial interconnect, transparent to the applications programmer, high-level interfaces are specified. These interfaces include: the message structure and protocol for a multitasking environment, and a set of high-level commands for remote I/O access and application task control. As with traditional bus specifications, the electrical and data protocol levels have been defined.

The BITBUS interconnect supports up to 250 nodes and three bit rates dependent on application performance requirements. Different BITBUS segments may support different bit rates.

#### A Simple and Reliable Solution

The BITBUS architecture supplies the system designer with a simple and reliable foundation. Some key features of this architecture are: defined high-level interfaces that provide all communication and user program management, the reliable SDLC protocol, power-up diagnostics, standard industrial packaging, compact software and hardware provided in the high performance 12MHz 8044 microcontroller, and a board-level integrated solution. In addition, complex, expensive, and awkward connection problems are no longer a factor because the BITBUS interconnect is a serial bus requiring a simple twisted wire pair.

#### **Open Systems — An Answer to Obsolescence**

Intel's Open Systems philosophy requires systems be open to: future VLSI, all levels of integration, third party suppliers, and special requirements. In order to facilitate this design strategy, the BITBUS interconnect was developed as a standard microcontroller interface. The same benefits realized by users of Intel's MULTIBUS architecture will be realized by users of the BITBUS architecture — the ability to exploit VLSI technology without having to pay premiums for new system design, multiple supply sources, wide product selections, and competitive prices.

The Open Systems philosophy characterizes the iDCM product line. Distributed Control Modules are compatible (open) at three levels of integration: components, boards, and systems. This multilevel approach enables OEM's to adapt to new business environments and opportunities as VLSI technology evolves.

#### **Distributed Control Modules**

The iDCM product line consists of both software and hardware products: the iRMX<sup>™</sup> 51 Executive, iRMX 510 Support Package, iSBX<sup>™</sup> 344 BITBUS MULTIMODULE<sup>™</sup> Board, and the iRCB 44/10 BITBUS Remote Controller Board. All iDCM hardware products include integral firmware to implement the high-level BITBUS interfaces: message formats, command sequences, and operating system environments.

#### iRMX™ 51 Executive

The iRMX 51 Executive is a compact, easy to use, software tool for development and implementation of applications built on the high performance 8-bit family of 8051 microcontrollers. A pre-configured version of the Executive is included in firmware of the two iDCM hardware products. During run-time, some of the services provided by this event driven Executive are: task scheduling, interrupt handling, and message passing. Streamlined code, the simple user interface and modular design of the iRMX 51 Executive enhance system reliability.

#### iRMX<sup>™</sup> 510 iDCM Support Package

The iRMX 510 iDCM Support Package provides the software development and run-time support for BITBUS systems. Also included are the software interfaces for other operating systems: iRMX 86, iRMX 286R, iRMX 88, and the iPDS ISIS. These software interfaces ease integration of a BITBUS system into MULTIBUS or iPDS environments.

#### iSBX<sup>™</sup> 344 BITBUS<sup>™</sup> MULTIMODULE<sup>™</sup> Board

The iSBX 344 board facilitates expansion of MULTIBUS and iPDS systems via the BITBUS interconnect. This board is the iDCM hardware interface. MULTIBUS system capabilities can be expanded to include low-cost remote control using the iSBX 344 MULTIMODULE board and the iRMX 510 iDCM Support Package. Also, BITBUS system capabilities can be expanded using this board with user supplied software. The iSBX 344 board's integral firmware reduces application development time, ensures real time response, eases system integration, and lowers system cost.

#### iRCB 44/10 BITBUS™ Remote Controller Board

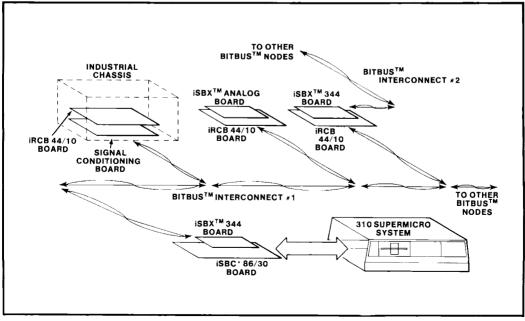

The iRCB 44/10 BITBUS Remote Controller module is a low-end, single-board computer with 24 lines of parallel I/O. The board has a single-high Eurocard form factor with a DIN connector for increased reliablity and integration with standard industrial packaging. One iSBX I/O Expansion connector will accommodate one of many iSBX MULTIMODULE Boards for I/O expansion. Also, sockets for repeaters are provided for extending the BITBUS interconnect beyond the length limits of one BITBUS segment. This board lowers distributed system cost via the BITBUS interconnect support and the same integral firmware provided on the iSBX 344 BITBUS Controller MULTIMODULE board.

#### Expanding a MULTIBUS® System with Distributed Control Modules

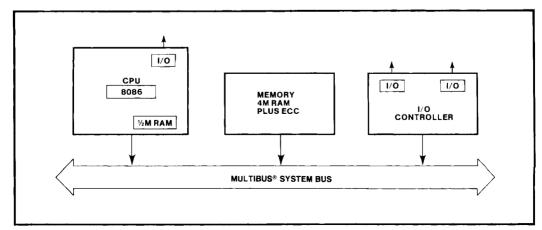

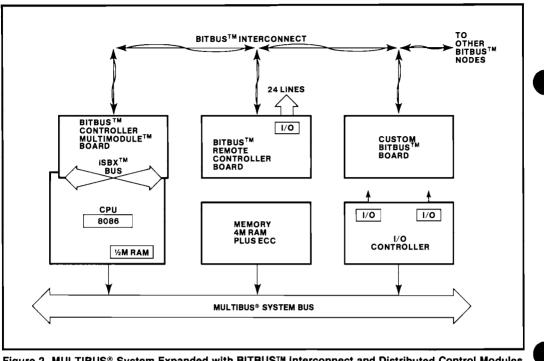

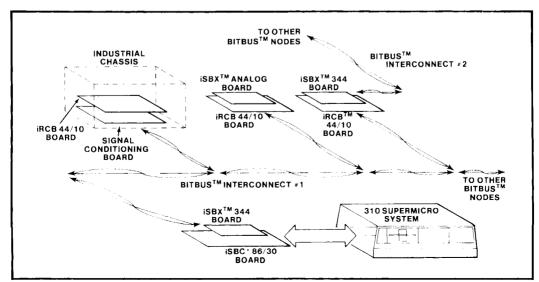

An example of how a MULTIBUS system can be expanded with iDCM Modules is shown in Figures 1 and 2. Figure 1 shows a basic MULTIBUS system: processor board, memory module, and I/O controller. Figure 2 illustrates the expanded system. Some advantages of the expanded system follow: The burden on the central processor has been reduced, thereby increasing overall system performance. System cost reduction is realized because the BITBUS architecture removes the necessity of adding expensive centralized systems to handle increased performance demands. Also, the BITBUS architecture enables implementation of a more efficient and flexible system that is insensitive to the addition of more nodes, or changes in node job functions.

Figure 1. Basic MULTIBUS® System

Figure 2. MULTIBUS<sup>®</sup> System Expanded with BITBUS™ Interconnect and Distributed Control Modules

#### Summary

This overview has introduced the attributes and advantages of the BITBUS interconnect and Distributed Control Modules. Initial iDCM products (the iRMX 51 Executive, the iRMX 510 iDCM Support Package, iSBX 344 BITBUS Controller MULTIMODULE and iRCB 44/10 BITBUS Remote Controller boards) are intended to allow rapid assimilation of this new technology. Data sheets describing the individual iDCM products are included in the next section of this document. The final section presents the BITBUS Specification (supported by the iDCM products).

# intel

## iSBX™ 344 BITBUS™ CONTROLLER MULTIMODULE™ BOARD

- High performance 12MHz 8044 controller

- Integral firmware including the iRMX<sup>™</sup> 51 Executive optomized for real-time control applications

- Full BITBUS<sup>™</sup> support

- 2 28-pin JEDEC memory sites for user's control functions

- Low cost, double-wide iSBX<sup>™</sup> BITBUS<sup>™</sup> expansion MULTIMODULE<sup>™</sup> board

- Power up diagnostics increase reliablity

The iSBX<sup>™</sup> 344 BITBUS<sup>™</sup> Controller MULTIMODULE<sup>™</sup> board is the BITBUS gateway to all Intel products that support the iSBX I/O Expansion Interface. Based on the highly integrated 8044 component (an 8 bit 8051 microcontroller and an SDLC controller on one chip) the iSBX 344 MULTIMODULE board extends the capability of other microprocessors via the BITBUS interconnect. With the other members of Intel's Distributed Control Modules (iDCM) family, the iSBX 344 MULTIMODULE board expands Intel's OEM microcomputer system capabilities to include distributed real-time control. Like all members of the iDCM family, the iSBX 344 MULTIMODULE board includes many features that make it well suited for industrial control applications such as: data acquisition and monitoring, process control, robotics, and machine control.

#### **OPERATING ENVIRONMENT**

Intel's Distributed Control Modules (iDCM) product family contains the building blocks to implement real-time distributed control applications. The iDCM family incorporates the BITBUS interconnect to provide standard high speed serial communication between microcontrollers. The two iDCM hardware products, the iSBX 344 MULTIMODULE board and the iRCB 44/10 BITBUS Remote Controller Board, communicate in an iDCM system via the BITBUS interconnect as shown in Figure 1.

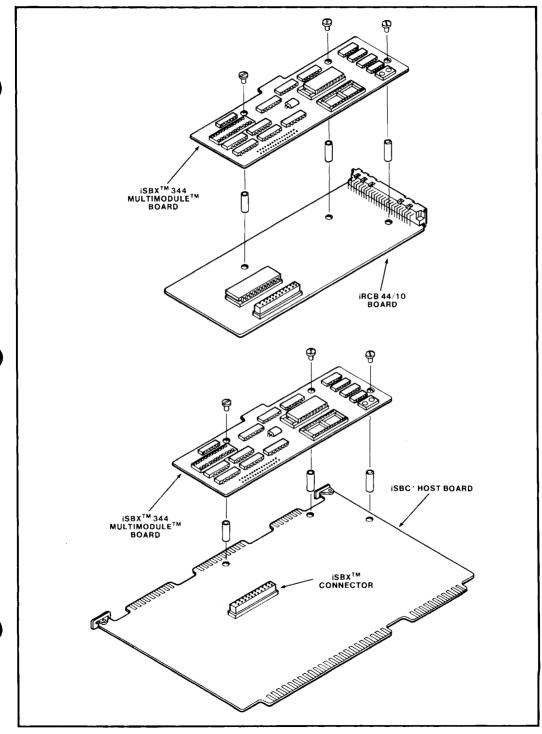

As a member of the iDCM product line the iSBX 344 MULTIMODULE board fully supports the BITBUS microcontroller interconnect. Typically, the iSBX 344 MULTIMODULE board would be part of a node (master or slave) on the BITBUS interconnect in an iDCM system. As shown in Figure 2 the iSBX 344 MULTIMODULE board plugs into any iSBC<sup>®</sup> board with an iSBX connector.

The iSBX 344 MULTIMODULE board is the hardware interface between Intel's MULTIBUS<sup>®</sup> and iPDS<sup>™</sup> ISIS environment and the BITBUS environment. With this interface the user can harness the capabilities of other Intel microprocessors eg: 80286, 80186, 8086 in a BITBUS/iDCM system or extend an existing MULTIBUS or iPDS ISISbased system with the iDCM family.

#### MULTIBUS<sup>®</sup> and iPDS<sup>™</sup> I/O Expansion

Typically, MULTIBUS iSBC boards have a maximum of two iSBX I/O expansion connectors. These connectors facilitate addition of one or two iSBX I/O MULTIMODULE boards with varying numbers of I/O lines. The iSBX 344 MULT-IMODULE board increases the number of I/O lines that can be accommodated by a MULTIBUS system by at least an order of magnitude. The iSBX 344 MULTIMODULE board extends the I/O of Intel's Personal Development System (iPDS) or other systems products in a similar manner.

#### Extending BITBUS™/iDCM System Processing Capability

The iSBX 344 MULTIMODULE board allows utilization of other processors in a BITBUS/iDCM system to accomodate particular application requirements. The MULTIMODULE board is compatible with any iSBX connector so that any board having a compatible connector can potentially enhance system performance. Intel's iRMX 510 iDCM Support Package provides the software interface required for a variety of iSBC boards. The iSBC 186/03, 86/30, 286/10, and 188/48 boards are a few examples. Custom configurations are also possible with user customized software.

Figure 1. iDCM Operating Environment

intel®

Figure 2. iSBX™ 344 Installation

### ARCHITECTURE

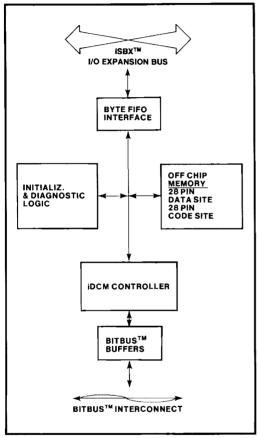

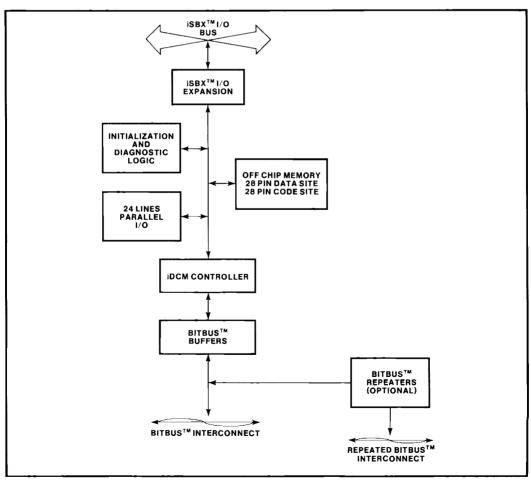

Figure 3 illustrates the major functional blocks of the iSBX 344 MULTIMODULE board : iDCM controller, memory, BITBUS microcontroller interconnect, Byte FIFO interface, initialization and diagnostic logic.

Figure 3. iSBX™ 344 Block Diagram

#### **iDCM** Controller

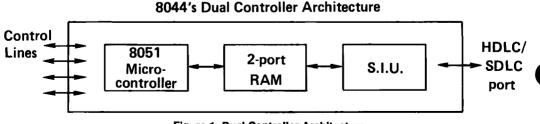

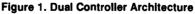

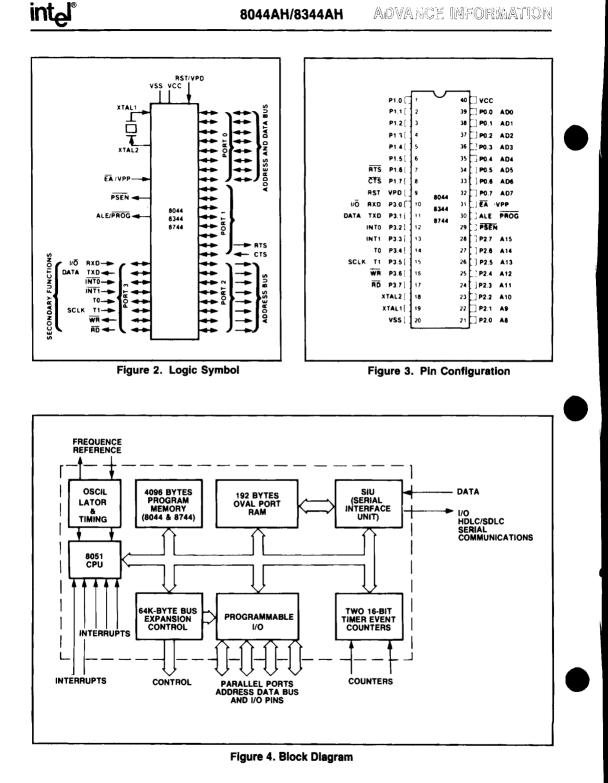

The heart of the iSBX 344 MULTIMODULE board's controlling and communication capability is the highly integrated 12 MHz 8044 microcontroller. The 8044 consists of the advanced 8-bit, 8051 microcontroller and a SDLC controller called the Serial Interface Unit (SIU). This dual processor architecture allows complex control and high speed communication to be realized cost effectively.

Another essential part of the iDCM controller is the integral firmware that resides on-chip to

implement the BITBUS interface. In the operating environment of the iSBX 344 MULTIMODULE board, the 8044's SIU acts as a SDLC controller which offloads the on-chip 8051 microcontroller of communication tasks; freeing the 8051 to concentrate on real-time control.

The iDCM controller (8044 microcontroller and on-chip firmware) provides, in one package, a simple user interface, and high performance communications and control capabilities to efficiently and economically build a complex control system.

#### Memory

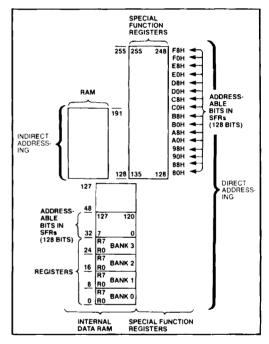

The iSBX 344 MULTIMODULE board memory consists of two sections: internal and external. Internal memory is located in the on-chip memory of the iDCM controller. The iRMX 51 Executive and the remaining iDCM controller firmware ration this resource. However, eight bytes of bit addressable internal memory are reserved for the user. Ample space is reserved for user programs and data in the iSBX 344 MULTIMODULE board external memory.

Two 28 pin JEDEC sites comprise the iSBX 344 MULTIMODULE board external memory. One site has been dedicated for data; the other for code. Table 1 lists the supported memory devices for each site. Intel's 2764, 27128, and 2817A are a few examples. The user may choose one of two memory configurations and specify different memory sizes by placing the proper jumpers at system initialization. The most flexible configuration option provides the user with access to the code site for program download or upload. This feature ensures expansion of an existing system is easily accomodated. For example, the addition of another conveyor to a material handling system would require adding another controller or controllers and changes to existing applications code and addition of new code.

#### Table 1. Supported Memory Devices

| DEVICE                             | DATA SITE | CODE SITE |

|------------------------------------|-----------|-----------|

| 4K × 8-64K × 8<br>EPROM/ROM        | NO        | YES       |

| 2K × 8-32K × 8<br>SRAM             | YES       | YES       |

| 2K × 8-16K × 8<br>NVRAM and E2PROM | NO        | YES       |

#### BITBUS™ Microcontroller Interconnect

The iSBX 344 MULTIMODULE board fully supports the BITBUS microcontroller interconnect. The BITBUS interconnect is a serial bus optimized for control applications. The interconnect supports both synchronous and self-clocked modes of operation. These modes of operation are selectable dependent on application requirements as are the transmission rates. Table 2 shows different combinations of modes of operations. transmission rates, and distances. The SDLC protocol, BITBUS message format, and compatbility with Intel's other software and hardware products comprise the remainder of this established architecture. These features contribute to BITBUS reliability and usefulness as a microcontroller interconnect.

The BITBUS connection consists of one or two differential pair(s) of wires. The BITBUS interface of the iSBX 344 MULTIMODULE board consists of a half-duplex RS 485 tranceiver and an optional clock source for the synchronous mode of operation.

#### **Byte FIFO Interface**

The Byte FIFO Interface on the iSBX 344 MULT-IMODULE board implements the required hardware buffering between the iDCM controller and an extension. An extension is defined as a device attached to the iSBX I/O expansion interface on the iSBX 344 MULTIMODULE board. In an iDCM system, an example of an extension is an iSBC 86/30 board which may be considered the host board in a MULTIBUS system. When used with the software handlers in the iRMX 510 iDCM Support Package, implementation of this interface is complete.

For particular applications, the user may wish to develop a custom software interface to the extension or host board. On the iSBX 344 MULTI-MODULE board side of the interface the iDCM firmware automatically accepts messages for the FIFO. No user code is required increasing the time available for application system development.

The Byte FIFO supports both byte and message transfer protocol in hardware via three register ports: data, command, and status. The extension side supports polled, interrupt, and limited DMA modes of operation (e.g. 80186 type DMA controllers).

#### Initalization and Diagnostic Logic

Like the other members of Intel's Distributed Control Modules (iDCM) product line, the iSBX 344 MULTIMODULE board includes many features which make it well suited for industrial control applications. Power up diagnostics is just one of these features. Diagnostics simplify system startup considerably, by immediately indicating an iDCM controller or external bus failure. The LEDs used for power up diagnostics are available for user diagnostics after power up as well as to further contribute to reliable operation of the system.

Initial iSBX 344 MULTIMODULE board parameters are set by positioning jumpers. The jumpers determine the BITBUS mode of operation: synchronous, self-clocked, transmission rate, and address of the iSBX module in the BITBUS system. This minimizes the number of spare boards to be stocked for multiple nodes, decreasing stocking inventory and cost.

#### INTEGRAL FIRMWARE

The iSBX BITBUS Controller MULTIMODULE board contains resident firmware located in the iDCM Controller. The on-chip firmware consists of: a pre-configured iRMX 51 Executive for user program development; a Remote Access and Control (RAC) function that enables user communication and control of different microcontrollers and I/O points; a communications gateway to

|              | Speed<br>Kb/s | Maximum Distance<br>Between Repeaters<br>M/ft | Maximum # Nodes<br>Between Repeaters | Maximum #<br>Repeaters |

|--------------|---------------|-----------------------------------------------|--------------------------------------|------------------------|

| Synchronous  | 2400          | 30/100                                        | 28                                   | 0                      |

| Self Clocked | 375<br>62.5   | 300/1000<br>1200/4000                         | 28<br>28                             | 2<br>10                |

#### Table 2. BITBUS™ Microcontroller Interconnect Modes of Operation

connect the BITBUS interconnect, iSBX bus, and iRMX 51 Executive tasks; and power up diagnostics.

The iRMX 51 Executive is an event-driven software manager that can respond to the needs of multiple tasks. This real-time multitasking executive provides: task management, timing, interrupt handling, and message passing services. Table 3 shows the iRMX 51 user interfaces. Both the executive and the communications gateway allow for the addition of up to seven user tasks at each node while making BITBUS operations transparent.

The Remote Access and Control Function is a special purpose task that allows the user to transfer commands and program variables to remote BITBUS controllers, obtain the status of a remote I/O line(s), or reverse the state of a remote I/O line. Table 4 provides a complete listing of the RAC services. No user code need be written to use this function. Power up tests provide a quick diagnostic service.

The services provided by the iSBX 344 MULT-IMODULE board integral firmware simplify the development and implementation of complex real-time control application systems. All iDCM hardware products contain integral firmware thus supplying the user with a total system solution.

#### **DEVELOPMENT ENVIRONMENT**

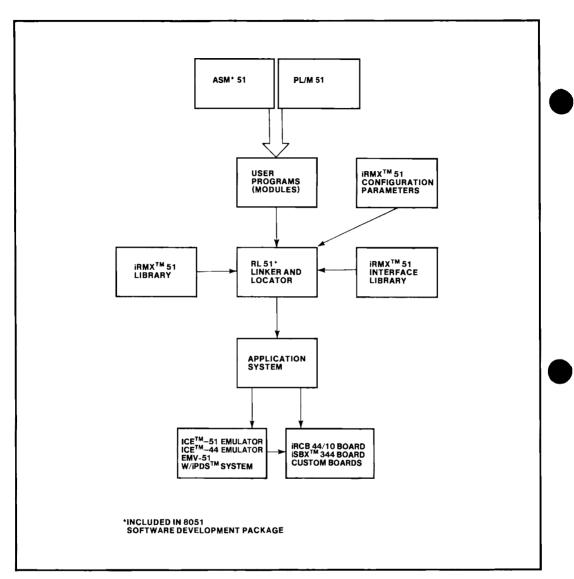

Intel provides a complete development environment for the iSBX 344 MULTIMODULE board. Software development support consists of : the 8051 Software Development Package, and the iRMX 510 iDCM Support Package. The 8051 Software Development Package provides the RL 51 Linker and Relocator Program, and ASM 51. PL/M 51 is also available. The iRMX 510 Support Package includes the iDCM Controller firmware files on diskette as well as iRMX 51 libraries. Hardware tools consist of of the IN-Circuit Emulator (ICE-44), Intel's Portable Development System (iPDS), and Intellec Series II or III Development Systems.

| COMMAND               | DESCRIPTION                                                                                                                                                  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RQ SEND MESSAGE       | Sends a message (a command from the BITBUS master, a response from a slave, or a simple message between tasks on the same BITBUS component) to another task. |

| RQ WAIT               | Waits for an interrupt, and event time-out, a message, or any combination of the three.                                                                      |

| RQ CREATE TASK        | Causes a new sequence of code to be run as an iRMX 51 task with a specific function identification code and priority.                                        |

| RQ DELETE TASK        | Stops the specified task and removes it from all execution lists.                                                                                            |

| RQ ALLOCATE           | Allocates a fixed-length buffer from the on-chip, scratch-pad RAM for gen-<br>eral use, or, in BITBUS applications, for a BITBUS message buffer.             |

| RQ DEALLOCATE         | Returns an on-chip buffer to the system.                                                                                                                     |

| RQ SET INTERVAL       | Set the time interval to be used as a separate event-timer for the task.                                                                                     |

| RQ ENABLE INTERRUPT   | Allow external interrupts to signal the microcontroller.                                                                                                     |

| RQ DISSABLE INTERRUPT | Stops all external interrupts from signaling the microcontroller.                                                                                            |

| RQ GET FUNCTION ID    | Provides a list of the 8 function identification codes representing the tasks currently operating on the microcontroller.                                    |

#### Table 3. iRMX™ 51 Interfaces

| COMMAND                  | DESCRIPTION                                                                                                               |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------|

| READ I/O                 | Read external I/O location. Return result in reply message.                                                               |

| WRITE I/O                | Write byte to external I/O location.                                                                                      |

| UPDATE I/O               | Write byte to, then read byte from external I/O location. Return result in reply message.                                 |

| OR I/O                   | OR data with contents of external I/O location. Return OR'd value.                                                        |

| AND I/O                  | AND data with contents of external I/O location. Return AND'd value.                                                      |

| XOR I/O                  | XOR data with contents of external I/O location. Return XOR'd value.                                                      |

| READ INTERNAL MEMORY     | Read contents of internal memory location. Return result in reply message.                                                |

| WRITE INTERNAL MEMORY    | Write data to internal memory location.                                                                                   |

| DOWNLOAD EXTERNAL MEMORY | Write data starting at external memory location.                                                                          |

| UPLOAD EXTERNAL MEMORY   | Read data starting at external memory location. Return result in reply message.                                           |

| GET FUNCTIONS            | Provides a list of the 8 function identification codes representing the tasks currently operating on the microcontroller. |

| CREATE TASK              | Causes a new sequence of code to be run as in the iRMX <sup>™</sup> 51 interface.                                         |

| DELETE TASK              | Stops the specified task and removes it from all execution lists as in the iRMX <sup>™</sup> 51 interface.                |

| RAC PROTECT              | Suspends or resumes RAC Services.                                                                                         |

| RESET DEVICE             | Returns device software to original state at initialization.                                                              |

#### Table 4. RAC Services

#### NOTES:

Internal memory locations are included in the 192 bytes of data RAM provided in the microcontroller. External memory refers memory outside the microcontroller --- the 28-pin sockets of the iSBX 344 module and the iRCB 44/10 board. Each RAC Access Function may refer to 1, 2, 3, 4, 5, or 6 individual I/O or memory locations in a single command.

#### SPECIFICATIONS

#### Word Size

Instruction - 8 bit Data — 8 bit

#### Processor Clock 12 MHz

#### Instruction Execution Times

1 µsec 60% instructions 2 µsec 40% instructions 4 µsec Multiply & Divide

#### Memory Capacity/Addressing

iDCM Controller - 64 K

#### **Address Range**

|          | Option 1     | Option 2     |

|----------|--------------|--------------|

| External |              |              |

| Memory   |              |              |

| Data     | 0000H-7FFFH  | 0000H-7FFFH  |

| Code     | 1000H-0FFFFH | 8000H-0FFEFH |

| Internal |              |              |

| Memory   |              |              |

| Code     | 0000H-0FFFH  | 0000H-0FFFH  |

#### Terminations

Sockets provided on board for 1/4 Watt 5% Carbon type resistors. Resistor value to match characteristic impedance of cable as closely as possible - 120 ohms or greater.

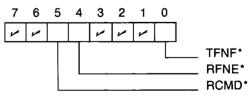

| FUNCTION      | ADDRESS | READ | WRITE | ВІТ | COMMENTS                                                                  |

|---------------|---------|------|-------|-----|---------------------------------------------------------------------------|

| Data          | FF00H   | -    | -     |     |                                                                           |

| Command       | FF01H   | ~    | -     |     | Write sets command to exten-<br>sion — Read clears command from extension |

| Status        |         |      |       |     |                                                                           |

| -RFNF*        | ВЗН     | -    |       | -   | Also INT1 Input                                                           |

| -TFNE*        | B2H     | -    |       | -   | Also INT0 Input                                                           |

| -TCMD*        | 92H     | -    |       | -   |                                                                           |

| LED #1        | 90H     | -    | -     | -   |                                                                           |

| LED #2        | 91H     | -    | -     | -   |                                                                           |

| RDY/NE*       | B4H     | · ·  | ~     | -   |                                                                           |

| Node Address  | FFFFH   | -    |       |     |                                                                           |

| Configuration | FFFEH   | -    |       |     |                                                                           |

#### iDCM Controller (8044 + firmware) I/O Addressing as viewed from the 8044

#### iSBX<sup>™</sup> 344 MULTIMODULE<sup>™</sup> board I/O Addressing as viewed from the iSBX<sup>™</sup> 344 MULTIMODULE<sup>™</sup> board

| REGISTER FUNCTION | ADDRESS  | COMMENTS                                                                    |  |

|-------------------|----------|-----------------------------------------------------------------------------|--|

| Data              | Base     | Read/Write                                                                  |  |

| Command           | Base + 1 | Write sets command from<br>extension<br>Read clears command to<br>extension |  |

| Status            | Base + 2 | Read Only                                                                   |  |

#### NOTES:

1. Base is determined by MCSO\* on extension device

#### Interrupt/DMA Lines

| SIGNAL | LOCATION   | INTERFACE<br>OPTION |

|--------|------------|---------------------|

| RINT   | MDRQ/MINT0 | INT                 |

| TINT   | MINT1      | INT                 |

| RCMI   | OPT0       | INT OR DMA          |

| RDRQ   | MDRQ/MINT0 | DMA                 |

| TDRQ   | MINT1      | DMA                 |

#### **Status Register Interface**

#### **Connector Options**

#### 10 Pin Plug

Flat Cable — 3M 3473-6010, TB Ansley 609-1001M, or equal Discrete Wire — BERG 65846-007, ITT Cannon 121-7326-105, or equal

#### Pin Out

| PIN | SIGNAL     |

|-----|------------|

| 1   | + 12V      |

| 2   | + 12V      |

| 3   | GND        |

| 4   | GND        |

| 5   | DATA*      |

| 6   | DATA       |

| 7   | DCLK*/RTS* |

| 8   | DCLK/RTS   |

| 9   | RGND       |

| 10  | RGND       |

#### **Electrical Characteristics**

#### Interfaces

**iSBX™ I/O expansion bus** — supports the standard I/O Expansion Bus Specification with compliance level D8

**Memory Sites** — Both code and data sites support the electrical Universal Memory Site specification

#### **Ordering Information**

| Part Number | Description              |  |  |

|-------------|--------------------------|--|--|

| iSBX 344    | <b>BITBUS</b> Controller |  |  |

MULTIMODULE board

**BITBUS™ Interconnect** — The iSBX 344 MULTI-MODULE board supports the BITBUS Specification as follows:

Fully supported synchronous mode at 2.4 Mbits/sec and self clocked mode for 375 kbits/sec and 62.5 kbits/sec

The iSBX 344 MULTIMODULE board presents one standard load to the BITBUS bus Message length of 18 bytes supported RAC Function support as shown in Table 4

#### **Power Requirements**

.9A at +5V±5% iSBX™ 344 MULTIMODULE™ board only — memory NOT included

#### **Physical Characteristics**

Double-wide iSBX™ MULTIMODULE™ Form Factor

#### Dimensions

Height — 10.16 mm (0.4 in) maximum component height Width — 63.5 mm (2.50 in)

**Depth** — 190.5 mm (7.50 in)

Weight - 113 gm (4 ounces)

#### **Environmental Characteristics**

**Operating Temperature** — 0°C to 55°C at 200 Linear Feet/Minute Air Velocity **Humidity** — 90% non-condensing

#### **Reference Manual (NOT Supplied)**

**146312** — Guide to Using the Distributed Control Modules

# Intel

## iRCB 44/10 BITBUS™ Remote Controller Board

- High performance 12 MHz 8044 controller

- Integral firmware including the iRMX<sup>™</sup> 51 Executive optomized for real-time control

- Full BITBUS™ support

- Standard industrial packaging: Eurocard, DIN connector

- 2 28-pin JEDEC memory sites for user's control functions

- Low cost I/O expansion with 8-bit iSBX<sup>™</sup> connector

- Programmable control/monitoring capability of 24 I/O lines

- Power up diagnostics increase reliability

The iRCB 44/10 BITBUS<sup>™</sup> Remote Controller Board, is an intelligent real-time controller and a remote I/O expansion device. Based on the highly integrated 8044 component (an 8 bit 8051 microcontroller and an intelligent SDLC controller on one chip) the iRCB 44/10 board provides high performance control capability at low cost. Incorporating complete BITBUS support, the iRCB 44/10 board and the other members of Intel's Distributed Control Modules (iDCM) family expand Intel's OEM microcomputer system capabilities to include distributed real-time control. Like all members of the iDCM family, the iRCB 44/10 board includes many features that make it well suited for industrial control applications such as: data acquisition and monitoring, process control, robotics, and machine control.

### **OPERATING ENVIRONMENT**

Intel's Distributed Control Modules (iDCM) product family contains the building blocks to implement real-time distributed control applications. The iDCM family incorporates the BITBUS interconnect to provide standard high speed serial communication between microcontrollers. The two iDCM hardware products, the iSBX 344 BIT-BUS controller MULTIMODULE<sup>™</sup> board and the iRCB 44/10 BITBUS Remote Controller Board, communicate in an iDCM system via the BITBUS interconnect as shown in Figure 1.

The iRCB 44/10 board can be used as an intelligent remote controller or an I/O expansion device. When performing as an intelligent controller the iRCB 44/10 board not only monitors the status of multiple process points, but it can execute varied user supplied control algorithms. When functioning as an I/O expansion device, the iRCB 44/10 board simply collects data from multiple I/O ports and transmits this information via the BITBUS or iSBX bus interface to the system controller for analysis or updating purposes.

As a member of the iDCM product line the iRCB 44/10 board fully supports the BITBUS microcontroller interconnect. Typically, the iRCB 44/10 board would be a node in a BITBUS system. The iRCB 44/10 board could be part of a master or slave node. (The BITBUS system supports a multidrop configuration: one master, many slaves.)

#### ARCHITECTURE

Figure 2 illustrates the major functional blocks of the iRCB 44/10 board: iDCM controller, memory, BITBUS microcontroller interconnect, parallel I/O, iSBX expansion, initialization and diagnostic logic.

#### **iDCM** Controller

The heart of the iRCB 44/10 board's controlling and communication capability is the highly integrated 12 MHz 8044 microcontroller. The 8044 consists of the advanced 8-bit 8051 microcontroller and a SDLC controller called the Serial Interface Unit (SIU). This dual processor architecture allows complex control and high speed communication functions to be realized cost effectively.

Another essential part of the iDCM controller is the integral firmware that resides on-chip to implement the BITBUS interface. In the operating environment of the iRCB 44/10 board, the 8044's SIU acts as a SDLC controller which offloads the on-chip 8051 microcontroller of communication tasks; freeing the 8051 to concentrate on realtime control.

The iDCM controller (8044 microcontroller and on-chip firmware) provides, in one package, a simple user interface, and high performance communications and control capabilities to efficiently and economically build a complex control system.

Figure 1. iDCM Operating Environment

## intel®

#### Memory

The iRCB 44/10 board memory consists of two sections: internal and external. Internal memory is located in the on-chip memory of the iDCM controller. The iRMX 51 Executive and the remaining iDCM controller firmware ration this resource. However, eight bytes of bit addressable internal memory are reserved for the user. Ample space is reserved for user programs and data in the iRCB 44/10 board external memory.

Two 28 pin JEDEC sites comprise the iRCB 44/10 board external memory. One site has been dedicated for data, the other for code. Table 1 lists the supported memory devices for each site. Intel's 2764, 27128, and 2817A are a few examples. The user may choose one of two memory configurations and specify different memory sizes by placing the proper jumpers at system initialization. The most flexible configuration option provides the user with access to the code site for program download or upload. This feature ensures expansion of an existing system is easily accomodated.

#### **Table 1. Supported Memory Devices**

| DEVICE                             | DATA SITE | CODE SITE |

|------------------------------------|-----------|-----------|

| 4K × 8-64K × 8<br>EPROM/ROM        | NO        | YES       |

| 2K × 8-32K × 8<br>SRAM             | YES       | YES       |

| 2K × 8-16K × 8<br>NVRAM and E2PROM | NO        | YES       |

Figure 2. iRCB™ 44/10 Block Diagram

#### BITBUS™ Microcontroller Interconnect

The iRCB 44/10 board serial interface fully supports the BITBUS microcontroller interconnect. The BITBUS interconnect is a serial bus optimized for control applications. The bus supports both synchronous and self-clocked modes of operation. These modes of operation are selectable dependent on application requirements as are the transmission speeds. Table 2 shows the different combinations of modes of operation, transmission speeds, and distances. The SDLC protocol, BITBUS message format, and compatibility with Intel's other software and hardware products comprise the remainder of the BITBUS architecture. These features contribute to BITBUS system reliability and usefulness as a microcontroller interconnect.

The BITBUS connection consists of one or two differential pair(s) of wires. The serial (BITBUS) interface of the iRCB 44/10 board consists of : a half-duplex RS 485 tranceiver, an optional BIT-BUS repeater and an optional clock source for the synchronous mode of operation.

#### Parallel I/O

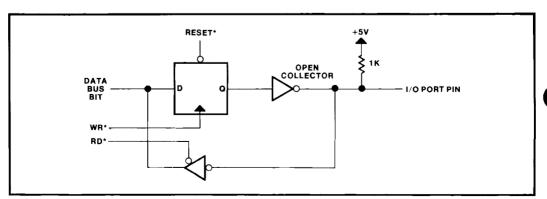

In order to provide an optimal parallel I/O interface for control applications, the iRCB 44/10 board supports 24 software programmable parallel I/O lines. This feature supplies the flexibility and simplicity required for control and data acquisition systems. Sixteen of these lines are fully programmable as inputs or outputs, with loopback, on a bit by bit basis so that bit set, reset, and toggle operations are streamlined. The remaining eight lines are dedicated as inputs. Figure 3 depicts the general I/O port structure.

The parallel I/O lines can be manipulated by using the Remote Access and Control (RAC) function (in iDCM controller firmware) from a supervisory node or locally by a user program. The user program can also access the RAC function or directly operate the I/O lines. Input, output, mixed — input and output, and bit operations are possible simply by reading or writing a particular port.

#### iSBX™ Expansion

One iSBX I/O expansion connector is provided on the iRCB 44/10 board. This connector can be used to extend the I/O capability of the board. In addition to specialized and custom designed iSBX boards, a full line of compatible high speed, 8-bit expansion MULTIMODULE boards, both single and double wide, are available from Intel. The only incompatible modules are those that require the MWAIT\* signal or DMA operation. A few of Intel's iRCB 44/10 board compatible iSBX MULTI-MODULE boards include: parallel I/O, serial I/O, BITBUS expansion, IEEE 488 GPIB, analog input, analog output, and magnetic bubble.

With the iSBX 344 BITBUS Controller MULTI-MODULE board and user supplied software, the iRCB 44/10 board can act as an intelligent BIT-BUS repeater facilitating the transition between two BITBUS segments operating at different speeds.

#### Initalization and Diagnostic Logic

Like the other members of Intel's Distributed Control Modules (iDCM) product line, the iRCB 44/10 board includes many features which make it well suited for industrial control applications. Power up diagnostics is just one of these features. Diagnostics simplify system startup considerably, by immediately indicating an iDCM controller or external bus failure. The LEDs used for power up diagnostics are available for user diagnostics after power up as well to further contribute to reliable operation of the system.

Initial iRCB 44/10 board parameters are set by positioning jumpers. The jumpers determine the

| Speed<br>Kb/s     Maximum Distance<br>Between Repeaters<br>M/ft     Maximum # Nodes<br>Between Repeaters<br>Between Repeaters     Maximum # Nodes<br>Repeaters |      |           |    |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|----|----|

| Synchronous                                                                                                                                                    | 2400 | 30/100    | 28 | 0  |

| Self Clocked                                                                                                                                                   | 375  | 300/1000  | 28 | 2  |

|                                                                                                                                                                | 62.5 | 1200/4000 | 28 | 10 |

#### Table 2. Modes of Operation

BITBUS mode of operation: synchronous, self clocked, transmission speed, and address of the iRCB 44/10 board in the BITBUS system. This minimizes the number of spare boards to be stocked for multiple nodes, decreasing stocking inventory and cost.

#### INTEGRAL FIRMWARE

The iRCB 44/10 board contains resident firmware located in the iDCM Controller. The on-chip firmware consists of: a pre-configured iRMX 51 Executive for user program development; a Remote Access and Control (RAC) function that enables user communication and control of different microcontrollers and I/O points; a communications gateway to connect the BITBUS interconnect, iSBX bus, and iRMX 51 tasks; and power up diagnostics.

The iRMX 51 Executive is an event-driven software manager that can respond to the needs of multiple tasks. This real-time multitasking executive provides: task management, timing, interrupt handling, and message passing services. Table 3 shows the iRMX 51 user interfaces. Both the Executive and the communications gateway allow for the addition of up to seven user tasks at each node while making BITBUS operations transparent.

The Remote Access and Control Function is a special purpose task that allows the user to trans-

| COMMAND               | DESCRIPTION                                                                                                                                                  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RQ SEND MESSAGE       | Sends a message (a command from the BITBUS master, a response from a slave, or a simple message between tasks on the same BITBUS component) to another task. |  |

| RQ WAIT               | Waits for an interrupt, and event time-out, a message, or any combination of the three.                                                                      |  |

| RQ CREATE TASK        | Causes a new sequence of code to be run as an iRMX 51 task with a specific function identification code and priority.                                        |  |

| RQ DELETE TASK        | Stops the specified task and removes it from all execution lists.                                                                                            |  |

| RQ ALLOCATE           | Allocates a fixed-length buffer from the on-chip, scratch-pad RAM for gen-<br>eral use, or, in BITBUS applications, for a BITBUS message buffer.             |  |

| RQ DEALLOCATE         | Returns an on-chip buffer to the system.                                                                                                                     |  |

| RQ SET INTERVAL       | Set the time interval to be used as a separate event-timer for the task.                                                                                     |  |

| RQ ENABLE INTERRUPT   | Allow external interrupts to signal the microcontroller.                                                                                                     |  |

| RQ DISSABLE INTERRUPT | Stops all external interrupts from signalling the microcontroller.                                                                                           |  |

| RQ GET FUNCTION ID    | Provides a list of the 8 function identification codes representing the tasks<br>currently operating on the microcontroller.                                 |  |

#### Table 3. iRMX™ 51 Interfaces

Figure 3. I/O Port Structure

fer commands and program variables to remote BITBUS controllers, obtain the status of a remote I/O line(s), or reverse the state of a remote I/O line. Table 4 provides a complete listing of the RAC services. No user code need be written to use this function. Power up tests provide a quick diagnostic service.

The services provided by the iRCB 44/10 board integral firmware simplify the development and implementation of complex real-time control application systems. All iDCM hardware products contain integral firmware thus supplying the user with a total system solution.

#### INDUSTRIAL PACKAGING

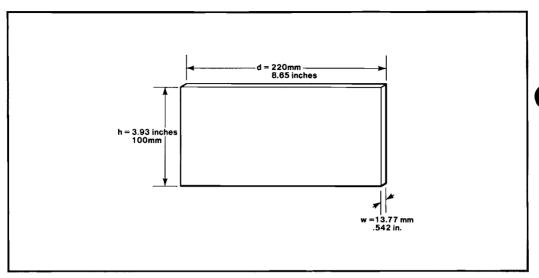

The iRCB 44/10 form factor is a single high, 220mm deep Eurocard as shown in Figure 4. The Eurocard form factor supports most standard industrial packaging schemes as well as Intel's MULTIBUS<sup>®</sup> II packaging scheme. The Eurocard form factor specifies reliable DIN connectors. A standard 64 pin connector is included on the iRCB 44/10 board.

#### DEVELOPMENT ENVIRONMENT

Intel provides a complete development environment for the iRCB 44/10 board. Software development support consists of: the 8051 Software Development Package, and the iRMX 510 iDCM Support Package The 8051 Software Development Package provides the RL 51 Linker and Relocator Program, and ASM 51. PL/M 51 is also available. The iRMX 510 Support Package includes the iDCM Controller firmware files on diskette, as well as iRMX 51 libraries. Hardware tools consist of of the In-Circuit Emulator (ICE-44), Intel's Portable Development System (iPDS), and Intellec Series II or III Development Systems.

| COMMAND                                                                                   | DESCRIPTION                                                                                                               |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| READ I/O                                                                                  | Read external I/O location. Return result in reply message.                                                               |  |  |

| WRITE I/O                                                                                 | Write byte to external I/O location.                                                                                      |  |  |

| UPDATE I/O                                                                                | Write byte to, then read byte from external I/O location. Return result in reply message.                                 |  |  |

| OR I/O                                                                                    | OR data with contents of external I/O location. Return OR'd value.                                                        |  |  |

| AND I/O                                                                                   | AND data with contents of external I/O location. Return AND'd value.                                                      |  |  |

| XOR I/O                                                                                   | XOR data with contents of external I/O location. Return XOR'd value.                                                      |  |  |

| READ INTERNAL MEMORY Read contents of internal memory location. Return result in message. |                                                                                                                           |  |  |

| WRITE INTERNAL MEMORY                                                                     | Write data to internal memory location.                                                                                   |  |  |

| DOWNLOAD EXTERNAL MEMORY                                                                  | Write data starting at external memory location.                                                                          |  |  |

| UPLOAD EXTERNAL MEMORY                                                                    | Read data starting at external memory location. Return result in reply message.                                           |  |  |

| GET FUNCTIONS                                                                             | Provides a list of the 8 function identification codes representing the tasks currently operating on the microcontroller. |  |  |

| CREATE TASK                                                                               | Causes a new sequence of code to be run as in the iRMX 51 inter-<br>face.                                                 |  |  |

| DELETE TASK                                                                               | Stops the specified task and removes it from all execution lists as in the iRMX 51 interface.                             |  |  |

| RAC PROTECT                                                                               | Suspends or resumes RAC Services.                                                                                         |  |  |

| RESET DEVICE                                                                              | Returns device software to original state at initialization.                                                              |  |  |

Table 4. RAC Services

#### NOTES:

Internal memory locations are included in the 192 bytes of data RAM provided in the microcontroller. External memory refers memory outside the microcontroller — the 28-pin sockets of the iSBX 344 module and the iRCB 44/10 board. Each RAC Access Function may refer to 1, 2, 3, 4, 5, or 6 individual I/O or memory locations in a single command.

#### SPECIFICATIONS

#### Word Size

Instruction — 8 bit Data — 8 bit

#### **Processor Clock 12 MHz**

#### Instruction Execution Times

1  $\mu$ sec 60% instructions 2  $\mu$ sec 40% instructions 4  $\mu$ sec Multiply & Divide

#### Memory Capacity/Addressing

iDCM Controller — 64 K

#### **Address Range**

|          | Option 1     | Option 2     |

|----------|--------------|--------------|

| External |              |              |

| Memory   |              |              |

| Data     | 0000H-7FFFH  | 0000H-7FFFH  |

| Code     | 1000H-0FFFFH | 8000H-0FFEFH |

| Internal |              |              |

| Memory   |              |              |

| Code     | 0000H-0FFFH  | 0000H-0FFFH  |

|          |              |              |

#### I/O Capacity

**iSBX MULTIMODULE™ board** — one single or doublewide not requiring MWAIT\* or DMA 24 Digital Lines Programmable Parallel I/O

#### **Interrupt Sources**

Two external — iSBX I/O Expansion bus sources or other sources. BITBUS Microcontroller Interconnect.

#### Terminations

Sockets provided on board for  $\frac{14}{4}$  Watt 5% Carbon type resistors. Resistor value to match characteristic impedance of cable as closely as possible — 120 ohms or greater.

#### Repeaters

Sockets provided on board — Devices 75174 and 75175

#### **Connector Options**

#### 10 Pin Plug

Flat Cable — 3M 3473-6010, TB Ansley 609-1001M, or equal Discrete Wire — BERG 65846-007, ITT Cannon 121-7326-105, or equal

#### **DIN Connector Plug**

Flat Cable — GW Elco 00-8259-096-84-124, Robinson Nugent RNE-IDC64C-TG30, or equal Discrete Wire — ITT Cannon G06 M96 P3 BDBL-004 GW Elco 60 8257 3017, or equal

| FUNCTION      | ADDRESS                   | READ                                    | WRITE | BIT |

|---------------|---------------------------|-----------------------------------------|-------|-----|

| PORT A        | FFCOH                     | ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ |       |     |

| PORT B        | FFC1H                     | -                                       |       |     |

| PORT C        | FFC2H                     | -                                       | -     |     |

| MCSO          | FF80H-FF87H<br>FF00, FF01 | -                                       | ~     |     |

| MSC1          | FF88H-FF8F                | -                                       | ~     |     |

| LED #1        | 90H                       | ~                                       | ~     | -   |

| LED #2        | 91H                       | ~                                       | ~     | -   |

| RDY/NE*       | B4H                       | ~                                       | Lan . | -   |

| NODE ADDRESS  | FFFFH                     | -                                       |       |     |

| CONFIGURATION | FFFEH                     | -                                       |       |     |

| OPT0          | 92H                       | -                                       | ~     | -   |

| OPT1          | 93H                       | -                                       | ~     | -   |

| INTO          | B2H                       | ~                                       |       | -   |

| INT1          | ВЗН                       | -                                       |       | -   |

#### iDCM Controller I/O Addressing

### 10 Pin Repeater Connector Pin Out

| PIN | SIGNAL     |

|-----|------------|

| 1   | + 12V      |

| 2   | + 12V      |

| 3   | GND        |

| 4   | GND        |

| 5   | DATA*      |

| 6   | DATA       |

| 7   | DCLK*/RTS* |

| 8   | DCLK/RTS   |

| 9   | RGND       |

| 10  | RGND       |

#### iRCB 44/10 Pin Out

| DIN Connector |                       |          |              |                       |            |

|---------------|-----------------------|----------|--------------|-----------------------|------------|

| DIN<br>PIN #  | PIN & SOCKET<br>PIN # | FUNCTION | DIN<br>PIN # | PIN & SOCKET<br>PIN # | FUNCTION   |

| 1a            |                       | GND      | 1c           |                       | GND        |

| 2a            |                       | + 5V     | 2c           |                       | + 5V       |

| 3a            |                       | DATA     | 3c           |                       | DATA*      |

| 4a            |                       | DLCK/RT  | 4c           |                       | DLCK*/RTS* |

| 5a            | 1                     | EXTINT   | 5c           |                       | RGND       |

| 6a            | 3                     | PB7      | 6c           | 2                     | GND        |

| 7a            | 5                     | PB6      | 7c           | 4                     | GND        |

| 8a            | 7                     | PB5      | 8c           | 6                     | GND        |

| 9a            | 9                     | PB4      | 9c           | 8                     | GND        |

| 10a           | 11                    | PB3      | 10c          | 10                    | GND        |

| 11a           | 13                    | PB2      | 11c          | 12                    | GND        |

| 12a           | 15                    | PB1      | 12c          | 14                    | GND        |

| 13a           | 17                    | PB0      | 13c          | 16                    | GND        |

| 14a           | 19                    | PC3      | 14c          | 18                    | GND        |

| 15a           | 21                    | PC2      | 15c          | 20                    | GND        |

| 16a           | 23                    | PC1      | 16c          | 22                    | GND        |

| 17a           | 25                    | PC0      | 17c          | 24                    | GND        |

| 18a           | 27                    | PC4      | 18c          | 26                    | GND        |

| 19a           | 29                    | PC5      | 19c          | 28                    | GND        |

| 20a           | 31                    | PC6      | 20c          | 30                    | GND        |

| 21a           | 33                    | PC7      | 21c          | 32                    | GND        |

| 22a           | 35                    | PA7      | 22c          | 34                    | GND        |

| 23a           | 37                    | PA6      | 23c          | 36                    | GND        |

| 24a           | 39                    | PA5      | 24c          | 38                    | GND        |

| 25a           | 41                    | PA4      | 25c          | 40                    | GND        |

| 26a           | 43                    | PA3      | 26c          | 42                    | GND        |

| 27a           | 45                    | PA2      | 27c          | 44                    | GND        |

| 28a           | 47                    | PA1      | 28c          | 46                    | GND        |

| 29a           | 49                    | PA0      | 29c          | 48                    | GND        |

| 30a           |                       | + 12V    | 30c          |                       | – 12V      |

| 31a           |                       | + 5V     | 31c          |                       | + 5V       |

| 32a           |                       | GND      | 32c          |                       | GND        |

#### **Electrical Characteristics**

#### Interfaces

**iSBX I/O expansion bus** — supports the standard I/O Expansion Bus Specification with compliance level D8/8F

**Memory Sites** — Both code and data sites support the electrical Universal Memory Site specification

**BITBUS™ Interconnect** — The iRCB 44/10 Remote Controller Board supports the BITBUS Specification as follows:

Fully supported synchronous mode at 2.4 Mbits/second and self clocked mode for 375 kbits/second and 62.5 kbits/second.

The iRCB 44/10 Remote Controller Board presents one standard load to the BITBUS bus without repeaters, with repeaters two standard loads Message length of 18 bytes supported

RAC Function support as shown in Table 4

**Parallel I/O** — See the Table 5 for Electrical Specifications of the interface.

#### **Power Requirements**

.9A at +5V±5% iRCB 44/10 board only — memory, repeater, or iSBX board NOT included

#### **Physical Characteristics**

Single high, 220mm deep Eurocard Form Factor **Dimensions**

Width — 13.77 mm (.542 in) maximum component height

Height — 100 mm (3.93 in)

Depth - 220 mm (8.65 in)

Weight — 169 gm (6 ounces)

#### **Environmental Characteristics**

**Operating Temperature** — 0°C to 55°C at 200 Linear Feet/Minute Air Velocity **Humidity** — 90% non-condensing

#### **Reference Manual (NOT Supplied)**

**146312** — Guide to Using the Distributed Control Modules

| PARAMETER       | CONDITION                                          | MIN   | MAX   | UNITS |

|-----------------|----------------------------------------------------|-------|-------|-------|

| V <sub>OL</sub> | l <sub>OL</sub> = 16 mA                            |       | 0.5   | v     |

| V <sub>OH</sub> | l <sub>OL</sub> = 16 mA<br>I <sub>OH</sub> = -2 mA | 2.4   |       | v     |

| V <sub>IH</sub> |                                                    | 2.0   | 7.0   | v     |

| V <sub>IL</sub> |                                                    | - 1.0 | 0.8   | V     |

| I <sub>IL</sub> | $V_{iL} = 0.5V$                                    |       | 6.0   | mA    |

| Г <sub>ІН</sub> | V <sub>IH</sub> = logic high                       |       | .0    | mA    |

| l <sub>1</sub>  | V <sub>IH</sub> ≈ 7V                               |       | - 2.2 | mA    |

|  | Table | 5. F | Parallel | 1/0 | Electrical | Specification |

|--|-------|------|----------|-----|------------|---------------|

|--|-------|------|----------|-----|------------|---------------|

#### **Ordering Information**

#### Part Number Description

iRCB 44/10 BITBUS Remote Controller board

# intel

## iRMX™ 51 REAL-TIME MULTITASKING EXECUTIVE

- Software tool for family of 8051 microcontroller based applications

- Real-time, multitasking executive

- Supports remote task communication

- Small 2.2K Bytes

- Reliable

- Simple user interface

- Compatible with BITBUS<sup>™</sup>/Distributed Control Modules (iDCM) product line: iSBX<sup>™</sup> 344 & iRCB 44/10 boards

The iRMX<sup>™</sup> 51 Executive is a compact, easy to use, software tool for development and implementation of applications built on the high performance 8-bit family of 8051 microcontrollers. A few members of this expansive family are the 8051, 8044, and 8052 microcontrollers. Like the 8051 family, the iRMX 51 Executive incorporates many features that make it exceptionally well suited for real-time control applications requiring manipulation and scheduling of more than one job, and fast response to external stimuli.

The 8051 microcontroller family is the family of choice for applications such as: data acquisition and monitoring, process control, robotics, and machine control. Using the iRMX 51 Executive for a foundation can significantly reduce applications development time. Also, the iRMX 51 Executive fully supports Intel's BITBUS<sup>™</sup> microcontroller interconnect expressly designed for reliable high performance real-time control.

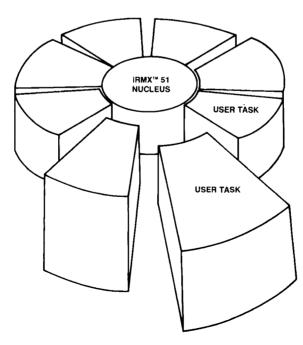

Figure 1. Structure Diagram

### ARCHITECTURE

#### **Real-time and Multitasking**

Real-time control applications must be responsive to the external environment and typically involve the execution of more than one function (task or set of tasks) in response to different external stimuli. Control of an industrial drying process is an example. This process could require monitoring of multiple temperatures and humidity; control of fans, heaters, and motors that must respond accordingly to a variety of inputs. The iRMX 51 Executive fully supports applications requiring response to stimuli as they occur ie. in real-time. This real-time response is supported for multiple tasks often needed to implement a control application.

Some of the facilities precisely tailored for development and implementation of real-time control application systems provided by the iRMX 51 Executive are: task management, interrupt handling, message passing, and when intergrated with communications support, message passing with different microcontrollers. Also, the iRMX 51 Executive is driven by events: interrupts, timers, and messages ensuring the application system always responds to the environment appropriately.

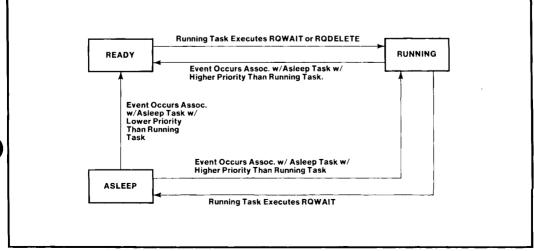

#### **Task Management**

A task is a program defined by the user to execute a particular control function or functions. Multiple programs or tasks may be required to implement a particular function such as 'controlling Heater 1. The iRMX 51 Executive recognizes three different task states as one of the mechanisms to accomplish scheduling of up to eight tasks. Figure 2 illustrates the different task states and their relationship to one another.

The scheduling of tasks is priority based. The user can prioritize tasks to reflect their relative importance within the overall control scheme. For instance, if Heater 1 must go off line prior to Heater 2 then the task associated with Heater 1 shutdown could be assigned a higher priority ensuring the correct shutdown sequence. The RQ WAIT system call is also a scheduling tool. In this example the task implementing Heater 2 shutdown could include an instruction to wait for completion of the task that implements Heater 1 shutdown.

The iRMX 51 Executive allows for PREEMPTION of a task that is currently being executed. This means that if some external event occurs such as a catastrophic failure of Heater 1, a higher priority task associated with the interrupt, message, or timeout resulting from the failure will preempt the running task. Preemption ensures the emergency will be responded to immediately. This is crucial for real-time control application systems.

#### **Interrupt Handling**

The iRMX 51 executive supports sixteen interrupt sources as shown in Table 1. Four of these interrupt sources, excluding timer 0, can be as-

Figure 2. Task State Transition Diagram

signed to a task. When one of the interrupts occurs the task associated with it becomes a running task (if it were the highest priority task in a ready state). In this way, the iRMX 51 Executive responds to a number of internal and external stimuli including time intervals designated by the user.

| INTERRUPT SOURCE       | INTERRUPT NUMBER |

|------------------------|------------------|

| External Request 0     | 00H              |

| Timer 0                | 01H              |

| External Request 1     | 02H              |

| Timer 1                | 03H              |

| Internal Serial Port 1 | 04H              |

| Reserved               | 05H              |

| Reserved               | 06H              |

| Reserved               | 07H              |