### 8207 DUAL-PORT DYNAMIC RAM CONTROLLER

- Provides All Signals Necessary to Control 16K, 64K and 256K Dynamic RAMs

- Directly Addresses and Drives up to 2 Megabytes without External Drivers

- Supports Single and Dual-Port Configurations

- Automatic RAM Initialization in All Modes

- Four Programmable Refresh Modes

- Transparent Memory Scrubbing in ECC Mode

- Fast Cycle Support for 8 MHz 80286 with 8207-16

- Slow Cycle Support for 8 MHz, 10 MHz 8086/88, 80186/188 with 8207-8, 8207-10

- Provides Signals to Directly Control the 8206 Error Detection and Correction Unit

- Supports Synchronous or Asynchronous Operation on Either Port

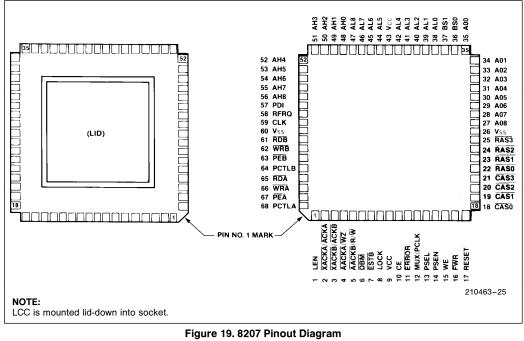

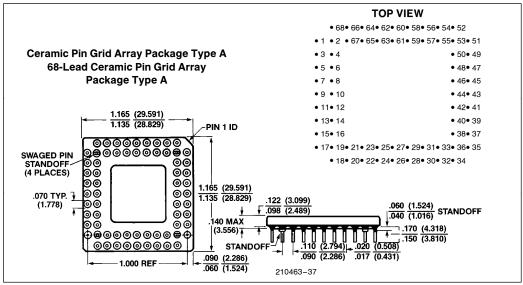

- 68 Lead JEDEC Type A Leadless Chip Carrier (LCC) and Pin Grid Array (PGA), Both in Ceramic.

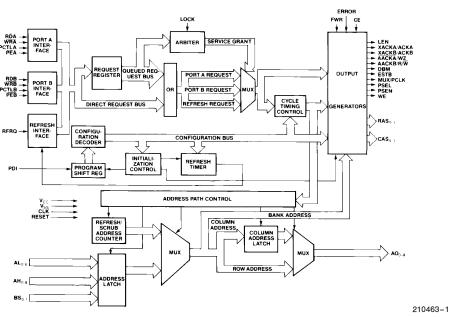

The Intel 8207 Dual-Port Dynamic RAM Controller is a high-performance, systems-oriented, Dynamic RAM controller that is designed to easily interface 16K, 64K and 256K Dynamic RAMs to Intel and other microprocessor systems. A dual-port interface allows two different busses to independently access memory. When configured with an 8206 Error Detection and Correction Unit the 8207 supplies the necessary logic for designing large error-corrected memory arrays. This combination provides automatic memory initialization and transparent memory error scrubbing.

Figure 1. 8207 Block Diagram

September 1987

Order Number: 210463-007

|                 | Table 1. Pin Description |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-----------------|--------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol          | Pin                      | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| LEN             | 1                        | 0    | ADDRESS LATCH ENABLE: In two-port configurations, when Port A is<br>running with iAPX 286 Status interface mode, this output replaces the ALE<br>signal from the system bus controller of port A and generates an address<br>latch enable signal which provides optimum setup and hold timing for the<br>8207. This signal is used in Fast Cycle operation only.                                                                                                                                                                                    |  |  |  |  |

| XACKA/<br>ACKA  | 2                        | 0    | <b>TRANSFER ACKNOWLEDGE PORT A/ACKNOWLEDGE PORT A:</b> In non-<br>ECC mode, this pin is XACKA and indicates that data on the bus is valid<br>during a read cycle or that data may be removed from the bus during a write<br>cycle for Port A. XACKA is a Multibus-compatible signal. In ECC mode, this<br>pin is ACKA which can be configured, depending on the programming of the X<br>program bit, as an XACK or AACK strobe. The SA programming bit<br>determines whether the AACK will be an early EAACKA or a late LAACKA<br>interface signal. |  |  |  |  |

| XACKB/<br>ACKB  | 3                        | Ο    | <b>TRANSFER ACKNOWLEDGE PORT B/ACKNOWLEDGE PORT B:</b> In non-<br>ECC mode, this pin is XACKB and indicates that data on the bus is valid<br>during a read cycle or that data may be removed from the bus during a write<br>cycle for Port B. XACKB is a Multibus-compatible signal. In ECC mode, this<br>pin is ACKB which can be configured, depending on the programming of the X<br>program bit, as an XACK or AACK strobe. The SB programming bit<br>determines whether the AACK will be an early EAACKB or a late LAACKB<br>interface signal. |  |  |  |  |

| AACKA/<br>WZ    | 4                        | 0    | <b>ADVANCED ACKNOWLEDGE PORT A/WRITE ZERO:</b> In non-ECC mode, this pin is AACKA and indicates that the processor may continue processing and that data will be available when required. This signal is optimized for the system by programming the SA program bit for synchronous or asynchronous operation. In ECC mode, after a RESET, this signal will cause the 8206 to force the data to all zeros and generate the appropriate check bits.                                                                                                  |  |  |  |  |

| AACKB/<br>R/W   | 5                        | 0    | <b>ADVANCED ACKNOWLEDGE PORT B/READ/WRITE:</b> In non-ECC mode, this pin is AACKB and indicates that the processor may continue processing and that data will be available when required. This signal is optimized for the system by programming the SB program bit for synchronous or asynchronous operation. In ECC mode, this signal causes the 8206 EDCU to latch the syndrome and error flags and generate check bits.                                                                                                                         |  |  |  |  |

| DBM             | 6                        | 0    | <b>DISABLE BYTE MARKS:</b> This is an ECC control output signal indicating that<br>a read or refresh cycle is occurring. This output forces the byte address<br>decoding logic to enable all 8206 data output buffers. In ECC mode, this<br>output is also asserted during memory initialization and the 8-cycle dynamic<br>RAM wake-up exercise. In non-ECC systems this signal indicates that either a<br>read, refresh or 8-cycle warm-up is in progress.                                                                                        |  |  |  |  |

| ESTB            | 7                        | 0    | <b>ERROR STROBE:</b> In ECC mode, this strobe is activated when an error is detected and allows a negative-edge triggered flip-flop to latch the status of the 8206 EDCU CE for systems with error logging capabilities. ESTB will not be issued during refresh cycles.                                                                                                                                                                                                                                                                             |  |  |  |  |

| LOCK            | 8                        | I    | <b>LOCK:</b> This input instructs the 8207 to lock out the port not being serviced at the time LOCK was issued.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| V <sub>CC</sub> | 9<br>43                  | I    | $\label{eq:constraint} \begin{array}{l} \textbf{DRIVER POWER:} + 5 \text{ volts. Supplies } V_{CC} \text{ for the output drivers.} \\ \textbf{LOGIC POWER:} + 5 \text{ volts. Supplies } V_{CC} \text{ for the internal logic circuits.} \end{array}$                                                                                                                                                                                                                                                                                               |  |  |  |  |

| CE              | 10                       | I    | <b>CORRECTABLE ERROR:</b> This is an ECC input from the 8206 EDCU which instructs the 8207 whether a detected error is correctable or not. A high input indicates a correctable error. A low input inhibits the 8207 from activating WE to write the data back into RAM. This should be connected to the CE output of the 8206.                                                                                                                                                                                                                     |  |  |  |  |

| Table 1. Pin Description (Continued) |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------------------------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                               | Pin            | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ERROR                                | 11             | Ι    | <b>ERROR:</b> This is an ECC input from the 8206 EDCU and instructs the 8207 that an error was detected. This pin should be connected to the ERROR output of the 8206.                                                                                                                                                                                                                                                                               |  |  |  |

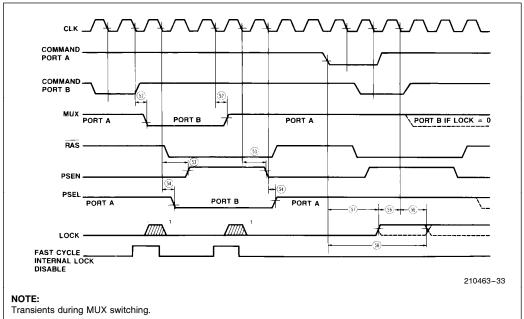

| MUX/<br>PCLK                         | 12             | 0    | <b>MULTIPLEXER CONTROL/PROGRAMMING CLOCK:</b> Immediately after a RESET this pin is used to clock serial programming data into the PDI pin. In normal two-port operation, this pin is used to select memory addresses from the appropriate port. When this signal is high, port A is selected and when it is low, port B is selected. This signal may change state before the completion of a RAM cycle, but the RAM address hold time is satisfied. |  |  |  |

| PSEL                                 | 13             | 0    | <b>PORT SELECT:</b> This signal is used to select the appropriate port for data transfer. When this signal is high port A is selected and when it is low port B is selected.                                                                                                                                                                                                                                                                         |  |  |  |

| PSEN                                 | 14             | 0    | <b>PORT SELECT ENABLE:</b> This signal used in conjunction with PSEL provides contention-free port exchange on the data bus. When PSEN is low, port selection is allowed to change state.                                                                                                                                                                                                                                                            |  |  |  |

| WE                                   | 15             | 0    | <b>WRITE ENABLE:</b> This signal provides the dynamic RAM array the write enable input for a write operation.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

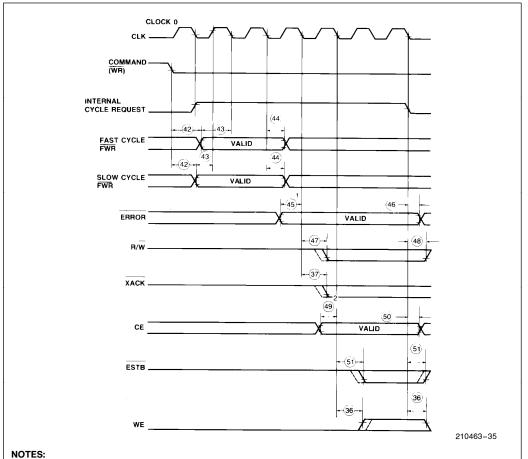

| FWR                                  | 16             | I    | <b>FULL WRITE:</b> This is an ECC input signal that instructs the 8207, in an ECC configuration, whether the present write cycle is normal RAM write (full write) or a RAM partial write (read-modify-write) cycle.                                                                                                                                                                                                                                  |  |  |  |

| RESET                                | 17             | I    | <b>RESET:</b> This signal causes all internal counters and state flip-flops to be reset<br>and upon release of RESET, data appearing at the PDI pin is clocked in by the<br>PCLK output. The states of the PDI, PCTLA, PCTLB and RFRQ pins are<br>sampled by RESET going inactive and are used to program the 8207. An 8-<br>cycle dynamic RAM warm-up is performed after clocking PDI bits into the<br>8207.                                        |  |  |  |

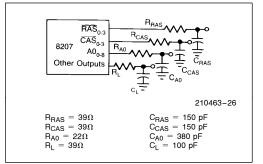

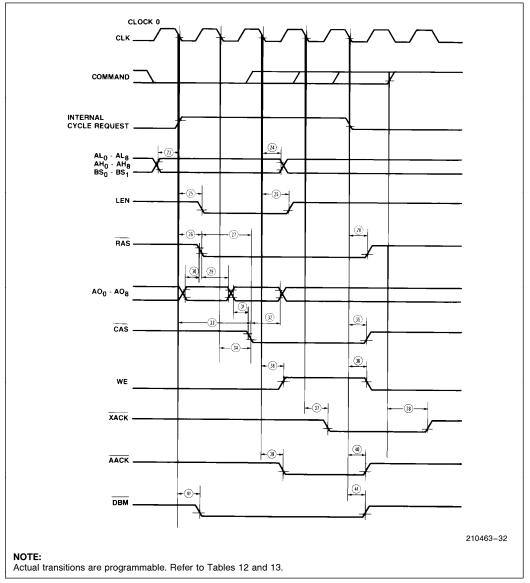

| CAS0-CAS3                            | 18–21          | 0    | <b>COLUMN ADDRESS STROBE:</b> These outputs are used by the dynamic RAM array to latch the column address, present on the AO0–8 pins. These outputs are selected by the BS0 and BS1 as programmed by program bits RB0 and RB1. These outputs drive the dynamic RAM array directly and need no external drivers.                                                                                                                                      |  |  |  |

| RAS0-RAS3                            | 22–25          | 0    | <b>ROW ADDRESS STROBE:</b> These outputs are used by the dynamic RAM array to latch the row address, present on the AO0–8 pins. These outputs are selected by the BS0 and BS1 as programmed by program bits RB0 and RB1. These outputs drive the dynamic RAM array directly and need no external drivers.                                                                                                                                            |  |  |  |

| V <sub>SS</sub>                      | 26<br>60       | I    | <b>DRIVER GROUND:</b> Provides a ground for the output drivers.<br><b>LOGIC GROUND:</b> Provides a ground for the remainder of the device.                                                                                                                                                                                                                                                                                                           |  |  |  |

| AO0-AO8                              | 35–27          | 0    | <b>ADDRESS OUTPUTS:</b> These outputs are designed to provide the row and column addresses of the selected port to the dynamic RAM array. These outputs drive the dynamic RAM array directly and need no external drivers.                                                                                                                                                                                                                           |  |  |  |

| BS0-BS1                              | 36–37          | I    | <b>BANK SELECT:</b> These inputs are used to select one of four banks of the dynamic RAM array as defined by the program bits RB0 and RB1.                                                                                                                                                                                                                                                                                                           |  |  |  |

| AL0-AL8                              | 38–42<br>44–47 | I    | <b>ADDRESS LOW:</b> These lower-order address inputs are used to generate the row address for the internal address multiplexer.                                                                                                                                                                                                                                                                                                                      |  |  |  |

| AH0-AH8                              | 48–56          | I    | ADDRESS HIGH: These higher-order address inputs are used to generate the column address for the internal address multiplexer.                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Table 1. Pin Description (Continued) |

|--------------------------------------|

|--------------------------------------|

| Symbol | Pin | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|--------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PDI    | 57  | I    | <b>PROGRAM DATA INPUT:</b> This input programs the various user-selectable options in the 8207. The PCLK pin shifts programming data into the PDI input from optional external shift registers. This pin may be strapped high or low to a default ECC (PDI = Logic "1") or non-ECC (PDI = Logic "0") mode configuration.                                                                                                                                                                                                                                                                  |  |  |  |  |

| RFRQ   | 58  | I    | <b>REFRESH REQUEST:</b> This input is sampled on the falling edge of RESET. If<br>t is high at RESET, then the 8207 is programmed for internal refresh request<br>or external refresh request with failsafe protection. If it is low at RESET, then<br>he 8207 is programmed for external refresh without failsafe protection or<br>purst refresh. Once programmed the RFRQ pin accepts signals to start an<br>external refresh with failsafe protection or external refresh without failsafe<br>protection or a burst refresh.                                                           |  |  |  |  |

| CLK    | 59  | I    | CLOCK: This input provides the basic timing for sequencing the internal logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| RDB    | 61  | I    | <b>READ FOR PORT B:</b> This pin is the read memory request command input for port B. This input also directly accepts the S1 status line from Intel processors.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| WRB    | 62  | I    | WRITE FOR PORT B: This pin is the write memory request command input for port B. This input also directly accepts the SO status line from Intel processors.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| PEB    | 63  | Ι    | <b>PORT ENABLE FOR PORT B:</b> This pin serves to enable a RAM cycle reques for port B. It is generally decoded from the port address.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| PCTLB  | 64  | I    | <b>PORT CONTROL FOR PORT B:</b> This pin is sampled on the falling edge of RESET. If Iow after RESET, the 8207 is programmed to accept memory read and write commands, Multibus commands or iAPX 286 status inputs. If high after RESET, the 8207 is programmed to accept status inputs from iAPX 86 or iAPX 186 processors. The S2 status line should be connected to this input if programmed to accept iAPX 86 or iAPX 186 status inputs. When programmed to accept commands or iAPX 286 status, it should be tied low or it may be used as a Multibus-compatible inhibit signal.      |  |  |  |  |

| RDA    | 65  | I    | <b>READ FOR PORT A:</b> This pin is the read memory request command input for port A. This input also directly accepts the S1 status line from Intel processors.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| WRA    | 66  | I    | WRITE FOR PORT A: This pin is the write memory request command input for port A. This input also directly accepts the S0 status line from Intel processors.                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| PEA    | 67  | I    | <b>PORT ENABLE FOR PORT A:</b> This pin serves to enable a RAM cycle request for port A. It is generally decoded from the port address.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| PCTLA  | 68  | I    | <b>PORT CONTROL FOR PORT A:</b> This pin is sampled on the falling edge of RESET. If Iow after RESET, the 8207 is programmed to accept memory read and write commands, Multibus commands or iAPX 286 status inputs. If high after RESET, the 8207 is programmed to accept status inputs from iAPX 86 or iAPX 186 processors. The S2 status line should be connected to this input if programmed to accept iAPX 86 or iAPX 186 status inputs. When programmed to accept commands or iAPX 286 status, it should be tied low or it may be connected to INHIBIT when operating with Multibus. |  |  |  |  |

### **GENERAL DESCRIPTION**

The Intel 8207 Dual-Port Dynamic RAM Controller is a microcomputer peripheral device which provides the necessary signals to address, refresh and directly drive 16K, 64K and 256K dynamic RAMs. This controller also provides the necessary arbitration circuitry to support dual-port access of the dynamic RAM array.

The 8207 supports several microprocessor interface options including synchronous and asynchronous connection to iAPX 86, iAPX 88, iAPX 186, iAPX 188, iAPX 286 and Multibus.

This device may be used with the 8206 Error Detection and Correction Unit (EDCU). When used with the 8206, the 8207 is programmed in the Error Checking and Correction (ECC) mode. In this mode, the 8207 provides all the necessary control signals for the 8206 to perform memory initialization and transparent error scrubbing during refresh.

#### FUNCTIONAL DESCRIPTION

#### **Processor Interface**

The 8207 has control circuitry for two ports each capable of supporting one of several possible bus

structures. The ports are independently configurable allowing the dynamic RAM to serve as an interface between two different bus structures.

Each port of the 8207 may be programmed to run synchronous or asynchronous to the processor clock. (See Synchronous/Asynchronous Mode.) The 8207 has been optimized to run synchronously with Intel's iAPX 86, iAPX 88, iAPX 186, iAPX 188, and iAPX 286. When the 8207 is programmed to run in asynchronous mode, the 8207 inserts the necessary synchronization circuitry for the RD, WR, PE, and PCTL inputs.

The 8207 achieves high performance (i.e., no wait states) by decoding the status lines directly from the iAPX 86, iAPX 88, iAPX 186, iAPX 188 and iAPX 286 processors. The 8207 can also be programmed to receive read or write Multibus commands or commands from a bus controller. (See Status/Command Mode.)

The 8207 may be programmed to accept the clock of the iAPX 86, 88, 186, 188 or 286. The 8207 adjusts its internal timing to allow for the different clock frequencies of these microprocessors. (See Microprocessor Clock Frequency Option.)

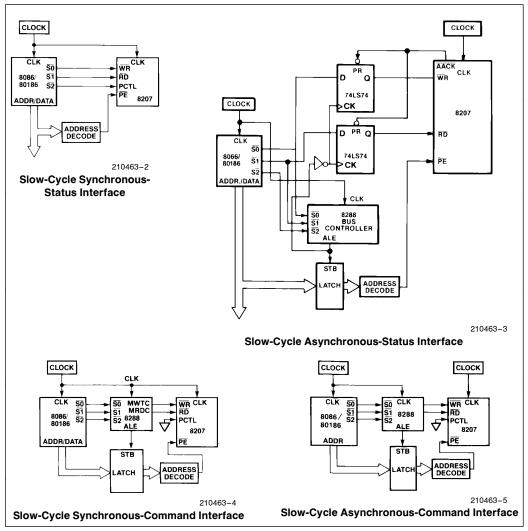

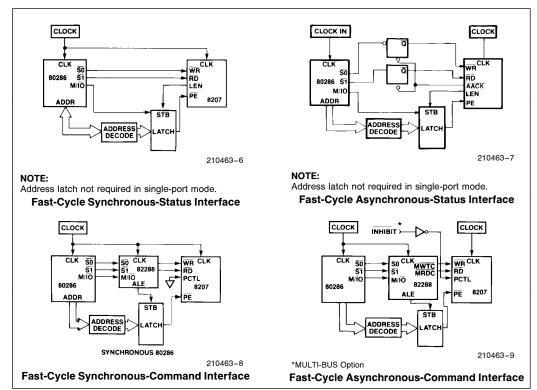

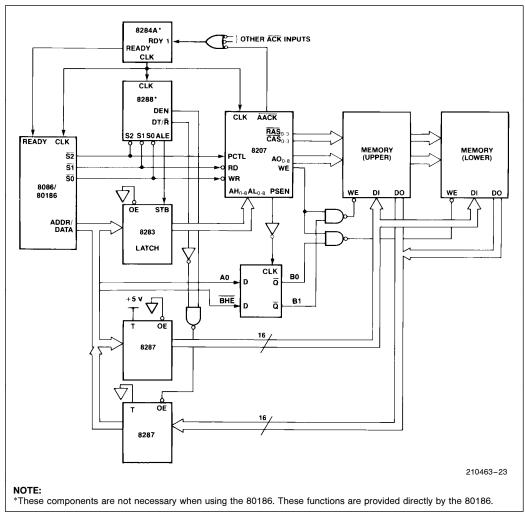

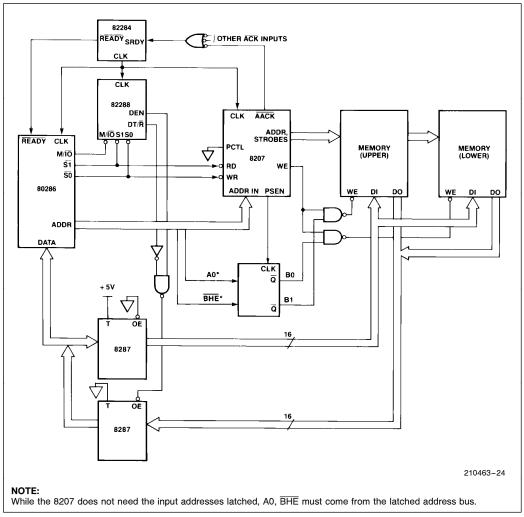

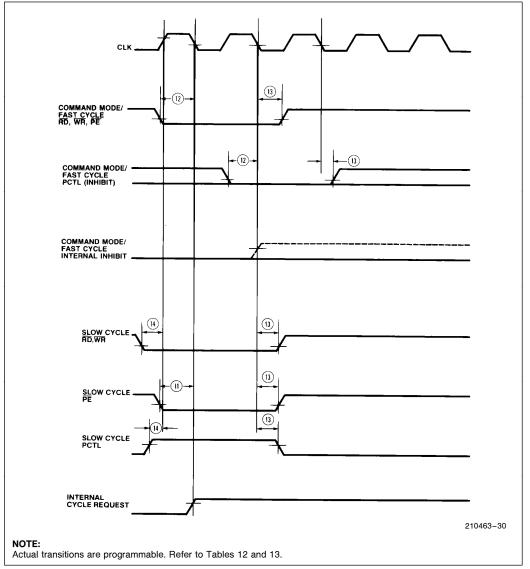

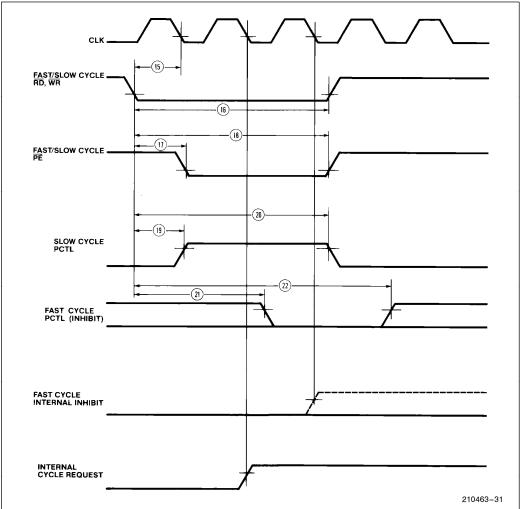

Figures 2A and 2B show the different processor interfaces to the 8207 using the synchronous or asynchronous mode and status or command interface.

Figure 2A. Slow-Cycle (CFS = 0) Port Interfaces Supported by the 8207

#### **Single-Port Operation**

The use of an address latch with the iAPX 286 status interface is not needed since the 8207 can internally latch the addresses with an internal signal similar in behavior to the LEN output. This operation is active only in single-port applications when the processor is interfaced to port A.

#### **Dual-Port Operation**

The 8207 provides for two-port operation. Two independent processors may access memory controlled by the 8207. The 8207 arbitrates between each of the processor requests and directs data to or from the appropriate port. Selection is done on a priority concept that reassigns priorities based upon past history. Processor requests are internally queued.

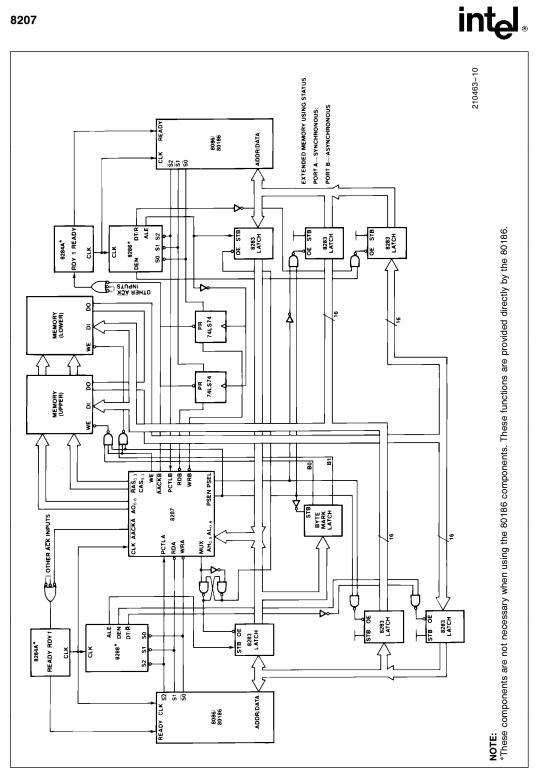

Figure 3 shows a dual-port configuration with two iAPX 86 systems interfacing to dynamic RAM. One of the processor systems is interfaced synchronously using the status interface and the other is interfaced asynchronously also using the status interface.

Figure 2B. Fast-Cycle (CFS = 1) Port Interfaces Supported by the 8207

#### **Dynamic RAM Interface**

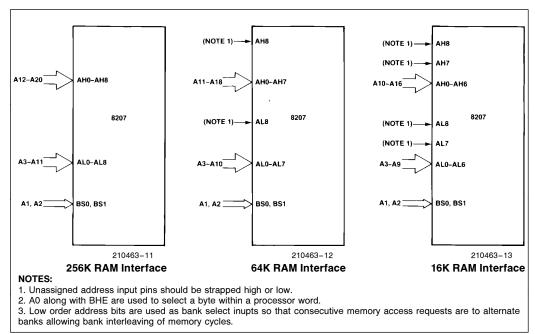

The 8207 is capable of addressing 16K, 64K and 256K dynamic RAMs. Figure 4 shows the connection of the processor address bus to the 8207 using the different RAMs.

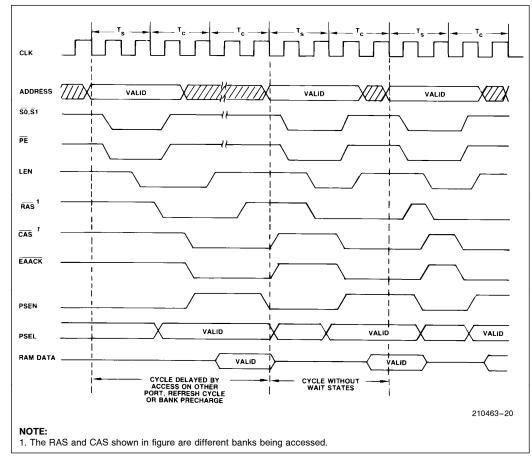

The 8207 divides memory into as many as four banks, each bank having its own Row (RAS) and Column (CAS) Address Strobe pair. This organization permits RAM cycle interleaving and permits er-

ror scrubbing during ECC refresh cycles. RAM cycle interleaving overlaps the start of the next RAM cycle with the RAM Precharge period of the previous cycle. Hiding the precharge period of one RAM cycle behind the data access period of the next RAM cycle optimizes memory bandwidth and is effective as long as successive RAM cycles occur in alternate banks.

Successive data access to the same bank will cause the 8207 to wait for the precharge time of the previous RAM cycle.

Figure 3. 8086/80186 Dual Port System

Figure 4. Processor Address Interface to the 8207 Using 16K, 64K, and 256K RAMs

If not all RAM banks are occupied, the 8207 reassigns the  $\overline{RAS}$  and  $\overline{CAS}$  strobes to allow using wider data words without increasing the loading on the RAS and  $\overline{CAS}$  drivers. Table 2 shows the bank selection decoding and the word expansion, including RAS and  $\overline{CAS}$  assignments. For example, if only two RAM banks are occupied, then two RAS and two  $\overline{CAS}$  strobes are activated per bank. Program bits RB1 and RB0 are not used to check the bank select inputs BS1 and BS0. The system design must protect from accesses to "illegal", non-existent banks of memory, by deactivating the PEA, PEB inputs when addressing an illegal bank.

The 8207 can interface to fast or slow RAMs. The 8207 adjusts and optimizes internal timings for either the fast or slow RAMs as programmed. (See RAM Speed Option.)

#### **Memory Initialization**

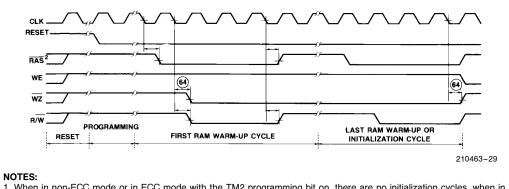

After programming, the 8207 performs eight RAM "warm-up" cycles to prepare the dynamic RAM for proper device operation. During "warm-up" some RAM parameters, such as tRAH, tASC, may not be met. This causes no harm to the dynamic RAM array. If configured for operation with error correction, the 8207 and 8206 EDCU will proceed to initialize all of memory (memory is written with zeros with corresponding check bits).

Table 2. Bank Selection Decoding and Word Expansion

| Decoding and word Expansion |             |               |     |                                                   |  |  |  |  |

|-----------------------------|-------------|---------------|-----|---------------------------------------------------|--|--|--|--|

| -                           | gram<br>Its | Bank<br>Input |     | RAS/CAS Pair<br>Allocation                        |  |  |  |  |

| RB1                         | RB0         | BS1           | BS0 | Allocation                                        |  |  |  |  |

| 0                           | 0           | 0             | 0   | $RAS_{0-3}$ , $CAS_{0-3}$ to Bank 0               |  |  |  |  |

| 0                           | 0           | 0             | 1   | lllegal                                           |  |  |  |  |

| 0                           | 0           | 1             | 0   | lllegal                                           |  |  |  |  |

| 0                           | 0           | 1             | 1   | lllegal                                           |  |  |  |  |

| 0                           | 1           | 0             | 0   | RAS <sub>0,1</sub> , CAS <sub>0,1</sub> to Bank 0 |  |  |  |  |

| 0                           | 1           | 0             | 1   | $RAS_{2,3}$ , $CAS_{2,3}$ to Bank 1               |  |  |  |  |

| 0                           | 1           | 1             | 0   | Illegal                                           |  |  |  |  |

| 0                           | 1           | 1             | 1   | lllegal                                           |  |  |  |  |

| 1                           | 0           | 0             | 0   | RAS <sub>0</sub> , CAS <sub>0</sub> to Bank 0     |  |  |  |  |

| 1                           | 0           | 0             | 1   | RAS <sub>1</sub> , CAS <sub>1</sub> to Bank 1     |  |  |  |  |

| 1                           | 0           | 1             | 0   | $RAS_2$ , $CAS_2$ to Bank 2                       |  |  |  |  |

| 1                           | 0           | 1             | 1   | lllegal                                           |  |  |  |  |

| 1                           | 1           | 0             | 0   | RAS <sub>0</sub> , CAS <sub>0</sub> to Bank 0     |  |  |  |  |

| 1                           | 1           | 0             | 1   | RAS <sub>1</sub> , CAS <sub>1</sub> to Bank 1     |  |  |  |  |

| 1                           | 1           | 1             | 0   | $RAS_2$ , $CAS_2$ to Bank 2                       |  |  |  |  |

| 1                           | 1           | 1             | 1   | $RAS_3$ , $CAS_3$ to Bank 3                       |  |  |  |  |

Because the time to initialize memory is fairly long, the 8207 may be programmed to skip initialization in ECC mode. The time required to initialize all of memory is dependent on the clock cycle time to the 8207 and can be calculated by the following equation:

$$T_{\rm INIT} = (2^{23}) T_{\rm CLCL} \tag{1}$$

if  $T_{CLCL} =$  125 ns then  $T_{INIT} \approx$  1 sec.

#### 8206 ECC Interface

For operation with Error Checking and Correction (ECC), the 8207 adjusts its internal timing and changes some pin functions to optimize performance and provide a clean dual-port memory interface between the 8206 EDCU and memory. The 8207 directly supports a master-only (16-bit word plus 6 check bits) system. Under extended operation and reduced clock frequency, the 8207 will support any ECC master-slave configuration up to 80 data bits, which is the maximum set by the 8206 EDCU. (See Extend Option.)

Correctable errors detected during memory read cycles are corrected immediately and then written back into memory.

In a synchronous bus environment, ECC system performance has been optimized to enhance processor throughput, while in an asynchronous bus environment (the Multibus), ECC performance has been optimized to get valid data onto the bus as quickly as possible. Performance optimization, processor throughput or quick data access may be selected via the Transfer Acknowledge Option.

The main difference between the two ECC implementations is that, when optimized for processor throughput, RAM data is always corrected and an advanced transfer acknowledge is issued at a point when, by knowing the processor characteristics, data is guaranteed to be valid by the time the processor needs it.

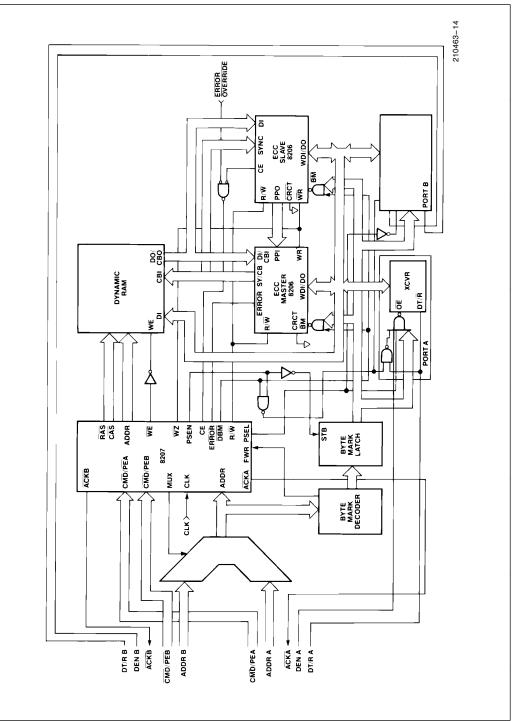

When optimized for quick data access, (valid for Multibus) the 8206 is configured in the uncorrecting mode where the delay associated with error correction circuitry is transparent, and a transfer acknowledge is issued as soon as valid data is known to exist. If the ERROR flag is activated, then the transfer acknowledge is delayed until after the 8207 has instructed the 8206 to correct the data and the corrected data becomes available on the bus. Figure 5 illustrates a dual-port ECC system.

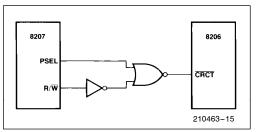

Figure 6 illustrates the interface required to drive the  $\overrightarrow{CRCT}$  pin of the 8206, in the case that one port (PORT A) receives an advanced acknowledge (not Multibus-compatible), while the other port (PORT B) receives  $\overrightarrow{XACK}$  (which is Multibus-compatible).

#### **Error Scrubbing**

The 8207/8206 performs error correction during refresh cycles (error scrubbing). Since the 8207 must refresh RAM, performing error scrubbing during refresh allows it to be accomplished without additional performance penalties.

Upon detection of a correctable error during refresh, the RAM refresh cycle is lengthened slightly to permit the 8206 to correct the error and for the corrected word to be rewritten into memory. Uncorrectable errors detected during scrubbing are ignored.

#### Refresh

The 8207 provides an internal refresh interval counter and a refresh address counter to allow the 8207 to refresh memory. The 8207 will refresh 128 rows every 2 milliseconds or 256 rows every 4 milliseconds, which allows all RAM refresh options to be supported. In addition, there exists the ability to refresh 256 row address locations every 2 milliseconds via the Refresh Period programming option.

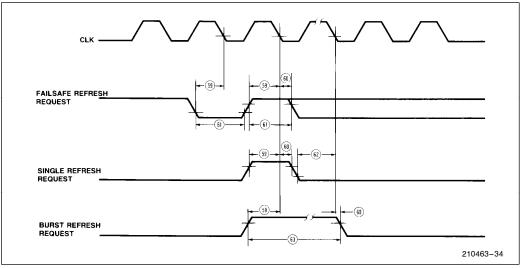

The 8207 may be programmed for any of four different refresh options: Internal refresh only, External refresh with failsafe protection, External refresh without failsafe protection, Burst Refresh mode, or no refresh. (See Refresh Options.)

It is possible to decrease the refresh time interval by 10%, 20% or 30%. This option allows the 8207 to compensate for reduced clock frequencies. Note that an additional 5% interval shortening is built-in in all refresh interval options to compensate for clock variations and non-immediate response to the internally generated refresh request. (See Refresh Period Options.)

#### External Refresh Requests after RESET

External refresh requests are not recognized by the 8207 until after it is finished programming and preparing memory for access. Memory preparation includes 8 RAM cycles to prepare and ensure proper

Figure 5. Two-Port ECC Implementation Using the 8207 and the 8206

11

11

Figure 6. Interface to 8206 CRCT Input when Port A Receives AACK and Port B Receives XACK

dynamic RAM operation, and memory initialization if error correction is used. Many dynamic RAMs require this warm-up period for proper operation. The time it takes for the 8207 to recognize a request is shown below.

Non-ECC Systems:

$$T_{RESP} = T_{PROG} + T_{PREP}$$

(2)

(3)

where:

$T_{PROG} = (66) (T_{CLCL})$  which is programming time

$T_{PREP} =$  (8) (32) ( $T_{CLCL}$ )

which is the RAM warm-up time

if  $T_{CLCL}$  = 125 ns then  $T_{RESP}$   $\approx$  41  $\mu$ s

ECC Systems:

$T_{RESP} = T_{PROG} + T_{PREP} + T_{INIT}$ (5)

if  $T_{CLCL}$  = 125 ns then  $T_{RESP}$   $\approx$  1 sec.

#### RESET

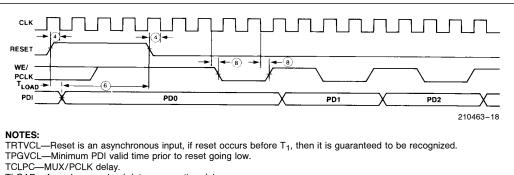

RESET is an asynchronous input, the falling edge of which is used by the 8207 to directly sample to logic levels of the PCTLA, PCTLB, RFRQ, and PDI inputs. The internally synchronized falling edge of RESET is used to begin programming operations (shifting in the contents of the external shift register into the PDI input).

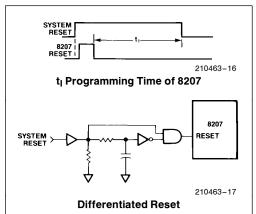

Until programming is complete the 8207 registers but does not respond to command or status inputs. A simple means of preventing commands or status from occurring during this period is to differentiate the system reset pulse to obtain a smaller reset pulse for the 8207. The total time of the reset pulse and the 8207 programming time must be less than the time before the first command in systems that alter the default port synchronization programming bits (default is Port A synchronous, Port B asynchronous). Differentiated reset is unnecessary when the default port synchronization programming is used.

The differentiated reset pulse would be shorter than the system reset pulse by at least the programming period required by the 8207. The differentiated reset pulse first resets the 8207, and system reset would reset the rest of the system. While the rest of the system is still in reset, the 8207 completes its programming. Figure 7 illustrates a circuit to accomplish this task.

Within four clocks after RESET goes active, all the 8207 outputs will go high, except for PSEN, WE, and AO0-2, which will go low.

#### **OPERATIONAL DESCRIPTION**

#### Programming the 8207

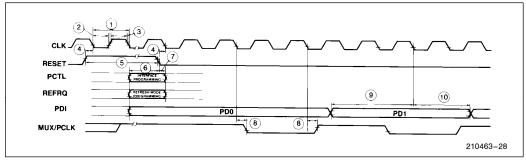

The 8207 is programmed after reset. On the falling edge of RESET, the logic states of several input pins are latched internally. The falling edge of RESET actually performs the latching, which means that the logic levels on these inputs must be stable prior to that time. The inputs whose logic levels are latched at the end of reset are the PCTLA, PCTLB, REFRQ, and PDI pins. Figure 8 shows the necessary timing for programming the 8207.

NOTES:

1. Required only when the port synchronization options (SA & SB) are altered from their initial default values. 2.  $V_{CC}$  must be stable before system reset is activated when using this circuit.

TLOAD—Asynchronous load data propagation delay.

Figure 8. Timing Illustrating External Shift Register Requirements for Programming the 8207

#### Status/Command Mode

The two processor ports of the 8207 are configured by the states of the PCTLA and PCTLB pins. Which interface is selected depends on the state of the individual port's PCTL pin at the end of reset. If PCTL is high at the end of the reset, the 8086 Status interface is selected; if it is low, then the Command interface is selected.

The status lines of the 80286 are similar in code and timing to the Multibus command lines, while the status code and timing of the 8086 and 8088 are identical to those of the 80186 and 80188 (ignoring the differences in clock duty cycle). Thus there exists two interface configurations, one for the 80286 status or Multibus memory commands, which is called the Command interface, and one for 8086, 8088, 80186 or 80188 status, called the 8086 Status interface. The Command interface can also directly interface to the command lines of the bus controllers for the 8086, 8088, 80186 and the 80286.

The 8086 Status interface allows direct decoding of the status of the iAPX 86, iAPX 88, iAPX 186 and the iAPX 188. Table 3 shows how the status lines are decoded. While in the Command mode the iAPX 286 status can be directly decoded. Microprocessor bus controller read or write commands or Multibus commands can also be directed to the 8207 when in Command mode.

#### **Refresh Options**

Immediately after system reset, the state of the REFRQ input pin is examined. If REFRQ is high, the 8207 provides the user with the choice between self-refresh or user-generated refresh with failsafe protection. Failsafe protection guarantees that if the

Table 3A. Status Coding of 8086, 80186 and 80286

| Sta | tus C     | ode           | Function          |              |  |

|-----|-----------|---------------|-------------------|--------------|--|

| S2  | <u>S1</u> | <del>S0</del> | 8086/80186        | 80286        |  |

| 0   | 0         | 0             | Interrupt         | Interrupt    |  |

| 0   | 0         | 1             | I/O Read          | I/O Read     |  |

| 0   | 1         | 0             | I/O Write         | I/O Write    |  |

| 0   | 1         | 1             | Halt              | ldle         |  |

| 1   | 0         | 0             | Instruction Fetch | Halt         |  |

| 1   | 0         | 1             | Memory Read       | Memory Read  |  |

| 1   | 1         | 0             | Memory Write      | Memory Write |  |

| 1   | 1         | 1             | Idle              | Idle         |  |

#### Table 3B. 8207 Response

|      | 8207<br>nmar | nd | Function                          |                                         |  |

|------|--------------|----|-----------------------------------|-----------------------------------------|--|

| PCTL | RD           | WR | 8086/80186<br>Status<br>Interface | 80286 Status or<br>Command<br>Interface |  |

| 0    | 0            | 0  | Ignore                            | Ignore*                                 |  |

| 0    | 0            | 1  | Ignore                            | Read                                    |  |

| 0    | 1            | 0  | Ignore                            | Write                                   |  |

| 0    | 1            | 1  | Ignore                            | Ignore*                                 |  |

| 1    | 0            | 0  | Read                              | Ignore                                  |  |

| 1    | 0            | 1  | Read                              | Inhibit                                 |  |

| 1    | 1            | 0  | Write                             | Inhibit                                 |  |

| 1    | 1            | 1  | Ignore                            | Ignore                                  |  |

\*Illegal with CFS = 0

user does not come back with another refresh request before the internal refresh interval counter times out, a refresh request will be automatically generated. If the REFRQ pin is low immediately after a reset, the 8207 is programmed in a non-failsafe refresh mode. In this mode the refresh cycle is initiated only upon receipt of an external refresh request. The user has the choice of a single external refresh cycle, burst refresh or no refresh.

#### **Internal Refresh Only**

For the 8207 to generate internal refresh requests, it is necessary only to strap the REFRQ input pin high.

#### **External Refresh with Failsafe**

To allow user-generated refresh requests with failsafe protection, it is necessary to hold the REFRQ input high until after reset. Thereafter, a low-to-high transition on this input causes a refresh request to be generated and the internal refresh interval counter to be reset. A high-to-low transition has no effect on the 8207. A refresh request is not recognized until a previous request has been serviced.

#### **External Refresh without Failsafe**

To generate single external refresh requests without failsafe protection, it is necessary to hold REFRQ low until after reset. Thereafter, bringing REFRQ high for one clock period causes refresh request to be generated. A refresh request is not recognized unit a previous request has been serviced.

#### **Burst Refresh**

Burst refresh is implemented through the same procedure as a single external refresh without failsafe (i.e., REFRQ is kept low until after reset). Thereafter, bringing REFRQ high for at least two clock periods causes a burst of up to 128 row address locations to be refreshed.

The ECC-configured systems, 128 locations are scrubbed. Any refresh request is not recognized until a previous request has been serviced (i.e., burst completed).

#### **No Refresh**

It is necessary to hold REFRQ low until after reset. This is the same as programming External Refresh without Failsafe. No refresh is accomplished by keeping REFRQ low.

#### **Option Program Data Word**

The program data word consists of 16 program data bits, PD0–PD15. If the first program data bit shifted into the 8207 (PD0) is set to logic 1, the 8207 is configured to support ECC. If it is logic 0, the 8207 is configured to support a non-ECC system. The remaining bits, PD1–PD15, may then be programmed to optimize a selected configuration. Figures 9 and 10 show the Program words for non-ECC and ECC operation.

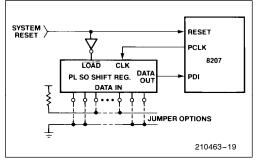

#### Using an External Shift Register

The 8207 may be configured to use an external shift register with asynchronous load capability such as a 74LS165. The reset pulse serves to parallel load the shift register and the 8207 supplies the clocking signal to shift the data in. Figure 11 shows a sample circuit diagram of an external shift register circuit.

Serial data is shifted into the 8207 via the PDI pin (57), and clock is provided by the MUX/PCLK pin (12), which generates a total of 16 clock pulses. After programming is complete, data appearing at the input of the PDI pin is ignored. MUX/PCLK is a dual-function pin. During programming, it serves to clock the external shift register, and after programming is completed, it reverts to a MUX conrol pin. As the pin changes state to select different port addresses, it continues to clock the shift register. This does not present a problem because data at the PDI pin is ignored after programming. Figure 8 illustrates the timing requirements of the shift register circuitry.

#### ECC Mode (ECC Program Bit)

The state of PDI (Program Data In) pin at reset determines whether the system is an ECC or non-ECC configuration. It is used internally by the 8207 to begin configuring timing circuits, even before programming is completely finished. The 8207 then begins programming the rest of the options.

#### **Default Programming Options**

After reset, the 8207 serially shifts in a program data word via the PDI pin. This pin may be strapped either high or low, or connected to an external shift register. Strapping PDI high causes the 8207 to default to a particular system configuration with error correction, and strapping it low causes the 8207 to default to a particular system configuration without error correction. Table 4 shows the default configurations.

| 15                  |            | PD8                                                                     | PD7                          |         |        |     |          | PD0 |

|---------------------|------------|-------------------------------------------------------------------------|------------------------------|---------|--------|-----|----------|-----|

| 0 TM 1              | PPR FFS E  | XT PLS CIO                                                              | CI1 RB                       | RB0     | RFS    | CFS | SB SA    | 0   |

| Program<br>Data Bit | Name       |                                                                         | Pola                         | rity/Fu | Inctio | n   |          |     |

| PD0                 | ECC        | ECC = 0                                                                 | ) For Non                    | -ECC N  | Node   |     |          |     |

| PD1                 | SA         | $\frac{\overline{SA}}{\overline{SA}} = 0$ $\frac{1}{\overline{SA}} = 1$ | Port A is<br>Port A is       |         |        |     |          |     |

| PD2                 | SB         |                                                                         | Port B is<br>Port B is       |         |        |     |          |     |

| PD3                 | CFS        |                                                                         | Fast-Cyo<br>Slow-Cy          |         |        |     | )        |     |

| PD4                 | RFS        |                                                                         | ) Fast RA                    |         |        |     |          |     |

| PD5<br>PD6          | RB0<br>RB1 | RAM Bar<br>See Tabl                                                     | nk Occupa<br>le 2            | incy    |        |     |          |     |

| PD7<br>PD8          | CI1<br>CI0 |                                                                         | terval Bit 1<br>terval Bit 0 | ·       |        |     |          |     |

| PD9                 | PLS        |                                                                         | Long Re                      |         |        |     |          |     |

| PD10                | EXT        |                                                                         | Not Exte<br>Extende          |         |        |     |          |     |

| PD11                | FFS        |                                                                         | Fast CP<br>Slow CF           | •       |        |     |          |     |

| PD12                | PPR        |                                                                         | ) Most Re<br>Port A P        | ,       |        |     | Priority |     |

| PD13                | TM1        |                                                                         | ) Test Mo<br>I Test Mo       |         | ••     | ł   |          |     |

| PD14                | 0          | Reserve                                                                 | d, Must be                   | Zero    |        |     |          |     |

| PD15                | 0          | Reserve                                                                 | d, Must be                   | Zero    |        |     |          |     |

Figure 9. Non-ECC Mode Program Data Word

| <b>D15</b><br>M2 RB1 RB | 0 PPR FFS  | PD8     PD7     PD0       EXT     PLS     CI0     CI1     XB     XA     RFS     CFS     SB     SA     1               |

|-------------------------|------------|-----------------------------------------------------------------------------------------------------------------------|

| Program<br>Data Bit     | Name       | Polarity/Function                                                                                                     |

| PD0                     | ECC        | ECC = 1 ECC Mode                                                                                                      |

| PD1                     | SA         | SA = 0 Port A Asynchronous<br>SA = 1 Port A Synchronous                                                               |

| PD2                     | SB         | $\frac{\overline{SB}}{\overline{SB}} = 0  \text{Port B Synchronous} \\ \overline{SB} = 1  \text{Port B Asynchronous}$ |

| PD3                     | CFS        | CFS = 0 Slow-Cycle iAPX 86 Mode<br>CFS = 1 Fast-Cycle iAPX 286 Mode                                                   |

| PD4                     | RFS        | RFS = 0 Slow RAM<br>RFS = 1 Fast RAM                                                                                  |

| PD5                     | XA         |                                                                                                                       |

| PD6                     | ХВ         | Advanced ACKB Not Multibus-Compatible $XB = 1$ Multibus-Compatible ACKB                                               |

| PD7<br>PD8              | CI1<br>CI0 | Count Interval Bit 1; see Table 6<br>Count Interval Bit 0; see Table 6                                                |

| PD9                     | PLS        | PLS = 0 Short Refresh Period<br>PLS = 1 Long Refresh Period                                                           |

| PD10                    | EXT        | $\overline{\text{EXT}} = 0$ Master and Slave EDCU<br>$\overline{\text{EXT}} = 1$ Master EDCU Only                     |

| PD11                    | FFS        | FFS = 0 Slow CPU Frequency<br>FFS = 1 Fast CPU Frequency                                                              |

| PD12                    | PPR        | PPR = 0 Port A Preferred Priority<br>PPR = 1 Most Recently Used Port Priority                                         |

| PD13<br>PD14            | RB0<br>RB1 | RAM Bank Occupancy<br>See Table 2                                                                                     |

| PD15                    | TM2        | $\overline{TM2} = 0$ Test Mode 2 Enabled<br>$\overline{TM1} = 1$ Test Mode 2 Off                                      |

Figure 10. ECC Mode Program Data Word

Figure 11. External Shift Register Interface

#### Table 4A. Default Non-ECC Programming, PDI Pin (57) Tied to Ground

| Port A is Synchronous ( $\overline{EAACKA}$ and $\overline{XACKA}$ ) |

|----------------------------------------------------------------------|

| Port B is Asynchronous (LAACKB and XACKB)                            |

| Fast-Cycle Processor Interface (iAPX 286)                            |

| Fast RAM                                                             |

| Refresh Interval uses 236 Clocks                                     |

| 128 Row Refresh in 2 ms; 256 Row Refresh in 4 ms                     |

| Fast Processor Clock Frequency (16 MHz)                              |

| "Most Recently Used" Priority Scheme                                 |

| 4 RAM banks occupied                                                 |

#### Table 4B. Default ECC Programming, PDI Pin (57) Tied to V<sub>CC</sub>

| Port A is Synchronous                            |  |  |  |  |  |

|--------------------------------------------------|--|--|--|--|--|

| Port B is Asynchronous                           |  |  |  |  |  |

| Fast-Cycle Processor Interface (iAPX 286)        |  |  |  |  |  |

| Fast RAM                                         |  |  |  |  |  |

| Port A has EAACKA strobe (non-multibus)          |  |  |  |  |  |

| Port B has XACKB strobe (multibus)               |  |  |  |  |  |

| Refresh interval uses 236 clocks                 |  |  |  |  |  |

| 128 Row refresh in 2 ms; 256 Row refresh in 4 ms |  |  |  |  |  |

| Master EDCU only (16-bit system)                 |  |  |  |  |  |

| Fast Processor Clock Frequency (16 MHz)          |  |  |  |  |  |

| "Most Recently Used" Priority Scheme             |  |  |  |  |  |

| 4 RAM banks ocuppied                             |  |  |  |  |  |

If further system flexibility is needed, one or two external shift registers can be used to tailor the 8207 to its operating environment.

### Synchronous/Asynchronous Mode (SA and SB Program Bits)

Each port of the 8207 may be independently configured to accept synchronous or asynchronous port commands (RD, WR, PCTL) and Port Enable (PE) via the program bits SA and SB. The state of the SA and SB programming bits determine whether their associated ports are synchronous or asynchronous.

While a port may be configured with either the Status or Command interface in the synchronous mode, certain restrictions exist in the asynchronous mode. An asynchronous Command interface using the control lines of the Multibus is supported, and an asynchronous 8086 interface using the control lines of the 8086 is supported, with the use of TTL gates as illustrated in Figure 2. In the 8086 case, the TTL gates are needed to guarantee that status does not appear at the 8207's inputs too much before address, so that a cycle would start before address was valid.

#### Microprocessor Clock Frequency Option (CFS and FFS Program Bits)

The 8207 can be programmed to interface with slow-cycle microprocessors like the 8086, 8088, 81088 and 80186 or fast-cycle microprocessors like the 80286. The CFS bit configures the microprocessor interface to accept slow or fast cycle signals from either microprocessor group.

The FFS bit is used to select the speed of the microprocessor clock. Table 5 shows the various microprocessor clock frequency options that can be programmed.

#### Table 5. Microprocessor Clock Frequency Options

| Progra | m Bits | Processor                | Clock<br>Frequency |  |  |

|--------|--------|--------------------------|--------------------|--|--|

| CFS    | FFS    | 110000001                |                    |  |  |

| 0      | 0      | iAPX 86,<br>88, 186, 188 | $\leq$ 6 MHz       |  |  |

| 0      | 1      | iAPX 86,<br>88, 186, 188 | > 6 MHz            |  |  |

| 1      | 0      | iAPX 286                 | $\leq$ 12 MHz      |  |  |

| 1      | 1      | iAPX 286                 | >12 MHz            |  |  |

The external clock frequency must be programmed so that the failsafe refresh repetition circuitry can adjust its internal timing accordingly to produce a refresh request as programmed.

#### **RAM Speed Option (RFS Program Bit)**

The RAM Speed programming option determines whether RAM timing will be optimized for a fast or slow RAM.

#### Refresh Period Options (CI0, CI1 and PLS Program Bits)

The 8207 refreshes with either 128 rows every 2 milliseconds or 256 rows every 4 milliseconds. This translates to one refresh cycle being executed approximately once every 15.6 microseconds. This rate can be changed to 256 rows every 2 milliseconds or a refresh approximately once every 7.8 microseconds via the Period Long/Short, program bit PLS, programming option. The 7.8 microsecond refresh request rate is intended for those RAMs, 64K and above, which may require a faster refresh rate.

In addition to PLS program option, two other programming bits for refresh exist: Count Interval 0 (Cl0) and Count Interval 1 (Cl1). These two programming bits allow the rate at which refresh requests are generated to be increased in order to permit refresh requests to be generated close to the same 15.6 or 7.8 microsecond period when the 8207 is operating at reduced frequencies. The interval between refreshes is decreased by 0%, 10%, 20%, or 30% as a function of how the count interval bits are programmed. A 5% guardband is built-in to allow for any clock frequency variations. Table 6 shows the refresh period options available.

The numbers tabulated under Count Interval represent the number of clock periods between internal refresh requests. The percentages in parentheses represent the decrease in the interval between refresh requests. Note that all intervals have a built-in 5% (approximately) safety factor to compensate for minor clock frequency deviations and non-immediate response to internal refresh requests.

### **Extend Option (EXT Program Bit)**

The Extend option lengthens the memory cycle to allow longer access time which may be required by the system. Extend alters the RAM timing to compensate for increased loading on the Row and Column Address Strobes, and in the multiplexed Address Out lines.

### Port Priority Option and Arbitration (PPR Program Bit)

The 8207 has to internally arbitrate among three ports: Port A, Port B and Port C—the refresh port. Port C is an internal port dedicated to servicing refresh requests, whether they are generated internally by the refresh interval counter, or externally by the user. Two arbitration approaches are available via

| Ref.<br>Period<br>(µs) | 050 | DI O |     | Count Interval CI1, CI0<br>(8207 Clock Periods) |             |             |             |  |

|------------------------|-----|------|-----|-------------------------------------------------|-------------|-------------|-------------|--|

|                        | CFS | PLS  | FFS | 00<br>(0%)                                      | 01<br>(10%) | 10<br>(20%) | 11<br>(30%) |  |

| 15.6                   | 1   | 1    | 1   | 236                                             | 212         | 188         | 164         |  |

| 7.8                    | 1   | 0    | 1   | 118                                             | 106         | 94          | 82          |  |

| 15.6                   | 1   | 1    | 0   | 148                                             | 132         | 116         | 100         |  |

| 7.8                    | 1   | 0    | 0   | 74                                              | 66          | 58          | 50          |  |

| 15.6                   | 0   | 1    | 1   | 118                                             | 106         | 94          | 82          |  |

| 7.8                    | 0   | 0    | 1   | 59                                              | 53          | 47          | 41          |  |

| 15.6                   | 0   | 1    | 0   | 74                                              | 66          | 58          | 50          |  |

| 7.8                    | 0   | 0    | 0   | 37                                              | 33          | 29          | 25          |  |

#### Table 6. Refresh Count Interval Table

NOTE:

Refresh period = clock period  $\times$  refresh count interval.

the Port Priority programming option, program bit PPR. PPR determines whether the most recently used port will remain selected (PPR = 1) or whether Port A will be favored or preferred over Port B (PPR = 0).

A port is selected if the arbiter has given the selected port direct access to the timing generators. The front-end logic, which includes the arbiter, is designed to operate in parallel with the selected port. Thus a request on the selected port is serviced immediately. In contrast, an unselected port only has access to the timing generators through the frontend logic. Before a RAM cycle can start for an unselected port, that port must first become selected (i.e., the MUX output now gates that port's address into the 8207 in the case of Port A or B). Also, in order to allow its address to stabilize, a newly selected port's first RAM cycle is started by the front-end logic. Therefore, the selected port has direct access to the timing generators. What all this means is that a request on a selected port is started immediately. while a request on an unselected port is started two to three clock periods after the request, assuming that the other two ports are idle. Under normal operating conditions, this arbitration time is hidden behind the RAM cycle of the selected port so that as soon as the present cycle is over a new cycle is started. Table 7 lists the arbitration rules for both options.

#### **Port LOCK Function**

The LOCK function provides each port with the ability to obtain uninterrupted access to a critical region of memory and, thereby, to guarantee that the opposite port cannot "sneak in" and read from or write to the critical region prematurely.

Only one LOCK pin is present and is multiplexed between the two ports as follows: when MUX is high, the 8207 treats the LOCK input as originating at PORT A, while when MUX is low, the 8207 treats LOCK as originating at PORT B. When the 8207 recognizes a LOCK, the MUX output will remain pointed to the locking port until LOCK is deactivated. Refresh is not affected by LOCK and can occur during a locked memory cycle.

#### Table 7. The Arbitration Rules for the Most Recently Used Port Priority and for Port A Priority Options Are As Follows:

| 1.  | If only one port requests service, then that port—if not already selected—becomes selected.                                                                                                                                                 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2a. | When no service requests are pending, the last selected processor port (Port A or B) will remain selected. (Most Recently Used Port Priority Option.)                                                                                       |

| 2b. | When no service requests are pending, Port A is selected whether it requests service or not. (Port A Priority Option.)                                                                                                                      |

| 3.  | During reset initialization only Port C, the refresh port, is selected.                                                                                                                                                                     |

| 4.  | If no processor requests are pending after reset initialization, Port A will be selected.                                                                                                                                                   |

| 5b. | If Ports A and B simultaneously(*) request service while Port C is selected, then the next port to be selected is Port A. (Port A Priority Option.)                                                                                         |

| 6.  | If a port simultaneously requests service with the currently selected port, service is granted to the selected port.                                                                                                                        |

| 7.  | The MUX output remains in its last state whenever Port C is selected.                                                                                                                                                                       |

| 8.  | If Port C and either Port A or Port B (or both) simultaneously request service, then service is granted to the requester whose port is already selected. If the selected port is not requesting service, then service is granted to Port C. |

| 9.  | If during the servicing of one port, the other port requests service before or simultaneously with the refresh port, the refresh port is selected. A new port is not selected before the presently selected port is deactivated.            |

| 10. | Activating LOCK will mask off service requests from Port B if the MUX output is high, or from Port A if the MUX output is low.                                                                                                              |

#### NOTE:

\*By "simultaneous" it is meant that two or more requests are valid at the clock edge at which the internal arbiter samples them.

#### **Dual-Port Considerations**

For both ports to be operated synchronously, several conditions must be met. The processors must be the same type (Fast or Slow Cycle) as defined by Table 8 and they must have synchronized clocks. Also when processor types are mixed, even though the clocks may be in phase, one frequency may be twice that of the other. So to run both ports synchronous using the status interface, the processors must have related timings (both phase and frequency). If these conditions cannot be met, then one port must run synchronous and the other asynchronous.

Figure 3 illustrates an example of dual-port operation using the processors in the slow cycle group. Note the use of cross-coupled NAND gates at the MUX output for minimizing contention between the two latches, and the use of flip flops on the status lines of the asynchronous processor for delaying the status and thereby guaranteeing RAS will not be issued, even in the worst case, until address is valid.

#### **Processor Timing**

In order to run without wait states, AACK must be used and connected to the SRDY input of the appropriate bus controller. AACK is issued relative to a point within the RAM cycle and has no fixed relationship to the processor's request. The timing is such, however, that the processor will run without wait states, barring refresh cycles, bank precharge, and RAM accesses from the other port. In non-ECC fast cycle, fast RAM, non-extended configurations (80286), AACK is issued on the next falling edge of

Figure 14. iAPX 286/8207 Synchronous-Status Timing Programmed in non-ECC Mode, C0 Configuration (Read Cycle)

the clock after the edge that issues RAS. In non-ECC, slow cycle, non-extended, or extended with fast RAM cycle configurations (8086, 80188, 80186), AACK is issued on the same clock cycle that issues RAS. Figure 14 illustrates the timing relationship between AACK, the RAM cycle, and the processor cycle for several different situations.

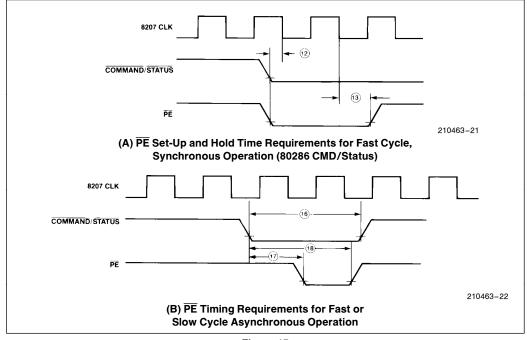

Port Enable ( $\overline{\text{PE}}$ ) setup time requirements depend on whether the associated port is configured for synchronous or asynchronous fast or slow cycle operation. In a synchronous fast cycle configuration,  $\overline{\text{PE}}$  is required to be setup to the same clock edge as the status or commands. If  $\overline{\text{PE}}$  is true (low), a RAM cycle is started; if not, the cycle is aborted. The memory cycle will only begin when both valid signals ( $\overline{\text{PE}}$  and  $\overline{\text{RD}}$  or WR) are recognized at a particular clock edge. In asynchronous operation.  $\overline{\text{PE}}$  is required to be setup to the same clock edge as the internally synchronized status or commands. Externally, this allows the internal synchronization delay to be added to the status (or command)-to-PE delay time, thus allowing for more external decode time that is available in synchronous operation.

The minimum synchronization delay is the additional amount that  $\overline{PE}$  must be held valid. If  $\overline{PE}$  is not held valid for the maximum synchronization delay time, it is possible that  $\overline{PE}$  will go invalid prior to the status or command being synchronized. In such a case the 8207 aborts the cycle. If a memory cycle intended for the 8207 is aborted, then no acknowledge (AACK or XACK) is issued and the processor locks up in endless wait states. Figure 15 illustrates the status (command) timing requirements for synchronous and asynchronous systems. Figures 16 and 17 show a more detailed hook-up of the 8207 to the 8086 and the 80286, respectively.

Figure 15

Figure 16. 8086/80186, 8207 Single Port Non-ECC Synchronous Systems

### Memory Acknowledge (AACK, XACK)

In system configurations without error correction, two memory acknowledge signals per port are supplied by the 8207. They are the Advanced Acknowledge strobe ( $\overline{AACK}$ ) and the Transfer Acknowledge strobe ( $\overline{XACK}$ ). The CFS programming bit determines for which processor  $\overline{AACKA}$  and  $\overline{AACKB}$  are optimized, either 80286 (CFS = 1) or 8086/186

(CFS = 0), while the SA and SB programming bits optimize  $\overrightarrow{AACK}$  for synchronous operation ("early"  $\overrightarrow{AACK}$ ) or asynchronous operation ("late"  $\overrightarrow{AACK}$ ).

Both the early and late  $\overline{AACK}$  strobes are three clocks long for CFS = 1 and two clocks long for CFS = 0. The XACK strobe is asserted when data is valid (for reads) or when data may be removed (for writes) and meets the Multibus requirements. XACK is removed asynchronously by the command going

Figure 17. 80286 Hook-Up to 8207 Non-ECC Synchronous System-Single Port

inactive. Since in asynchronous operation the 8207 removes read data before late AACK or XACK is recognized by the CPU, the user must provide for data latching in the system until the CPU reads the data. In synchronous operation, data latching is unnecessary since the 8207 will not remove data until the CPU has read it.

In ECC-based systems there is one memory acknowledge (XACK or AACK) per port and a programming bit associated with each acknowledge. If the X programming bit is active, the strobe is configured as  $\overline{XACK}$ , while if the bit is inactive, the strobe is configured as  $\overline{AACK}$ . As in non-ECC, the SA and SB programming bits determine whether the  $\overline{AACK}$  strobe is early or late ( $\overline{EAACK}$  or  $\overline{LAACK}$ ).

Data will always be valid a fixed time after the occurrence of the advanced acknowledge. Table 9 summarizes the various transfer acknowledge options.

| Cycle | Processor  | Request Type | Sync/Async<br>Interface | Acknowledge<br>Type |

|-------|------------|--------------|-------------------------|---------------------|

|       | 80286      | Status       | Sync                    | EAACK               |

|       | 80286      | Status       | Async                   | LAACK               |

| Fast  | 80286      | Command      | Sync                    | EAACK               |

| Cycle | 80286      | Command      | Async                   | LAACK               |

| CFS=1 | 8086/80186 | Status       | Async                   | LAACK               |

|       | 8086/80186 | Command      | Async                   | LAACK               |

|       | Multibus   | Command      | Async                   | XACK                |

|       | 8086/80186 | Status       | Sync                    | EAACK               |

| Slow  | 8086/80186 | Status       | Async                   | LAACK               |

| Cycle | 8086/80186 | Command      | Sync                    | EAACK               |

| CFS=0 | 8086/80186 | Command      | Async                   | LAACK               |

|       | Multibus   | Command      | Async                   | XACK                |

Table 8. Processor Interface/Acknowledge Summary

#### Table 9. Memory Acknowledge Option Summary

|            | Synchronous                          | Asynchronous                          | ХАСК                |

|------------|--------------------------------------|---------------------------------------|---------------------|

| Fast Cycle | AACK Optimized<br>for Local 80286    | AACK Optimized for<br>Remote 80286    | Multibus Compatible |

| Slow Cycle | AACK Optimized<br>for Local 8086/186 | AACK Optimized for<br>Remote 8086/186 | Multibus Compatible |

#### **Test Modes**

Two special test modes exist in the 8207 to facilitate testing. Test Mode 1 (non-ECC mode) splits the refresh address counter into two separate counters and Test Mode 2 (ECC mode) presets the refresh address counter to a value slightly less than rollover.

Test Mode 1 splits the address counter into two, and increments both counters simultaneously with each refresh address update. By generating external refresh requests, the tester is able to check for proper operation of both counters. Once proper individual counter operation has been established, the 8207 must be returned to normal mode and a second test performed to check that the carry from the first counter increments the second counter. The outputs of the counters are presented on the address out bus with the same timing as the row and column addresses of a normal scrubbing operation. During Test Mode 1, memory initialization is inhibited, since the 8207, be definition, is in non-ECC mode.

Test Mode 2 sets the internal refresh counter to a value slightly less than rollover. During functional