# intel

## iSBC® 88/45 ADVANCED DATA COMMUNICATIONS PROCESSOR BOARD

- Three HDLC/SDLC Half/Full-Duplex Communication Channels—Optional ASYNC/SYNC on Two Channels

- Supports RS232C (Including Modem Support), CCITT V.24, or RS422A/449 Interfaces

- On-Board DMA Supports 800K Baud Operation

- Self-Clocking NRZI SDLC Loop Data Link Interface

- Point-to-Point

- Multidrop

- Software Programmable Baud Rate Generation

- 8088 (8088-2) Microprocessor Operates at 8 MHz

- iSBC<sup>®</sup> 337 Numeric Data Processor Option Supported

- 16K Bytes Static RAM (12K Bytes Dual-Ported)

- Four 28-Pin JEDEC Sites for EPROM/ RAM Expansion; Four Additional 28-Pin JEDEC Sites Added with iSBC<sup>®</sup> 341 Board

- Two iSBX<sup>™</sup> Bus Connectors

- MULTIBUS<sup>®</sup> Interface Supports Multimaster Configuration

The iSBC 88/45 Advanced Data Communications Processor (ADCP) Board adds 8 MHz, 8088 (8088-2) 8-bit microprocessor-based communications flexibility to the Intel line of OEM microcomputer systems. The iSBC 88/45 ADCP board offers asynchronous, synchronous, SDLC, and HDLC serial interfaces for gateway networking or general purpose solutions. The iSBC 88/45 ADCP board provides the CPU, system clock, EPROM/RAM, serial I/O ports, priority interrupt logic, and programmable timers to facilitate higher-level application solutions.

210372-1

## FUNCTIONAL DESCRIPTION

#### **Three Communication Channels**

Three programmable HDLC/SDLC serial interfaces are provided on the iSBC 88/45 ADCP board. The SDLC interface is familiar to IBM system and terminal equipment users. The HDLC interface is known by users of CCITT's X.25 packet switching interface.

One channel utilizes an Intel 8273 controller to manage the serial data transfers. Accepting the 8-bit data bytes from the local bus, the 8273 controller translates the data into the HDLC/SDLC format. The channel operates in half/full-duplex mode.

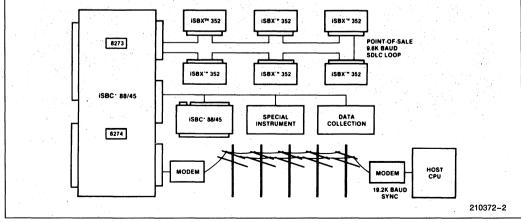

In addition to the synchronous mode, the 8273 controller operates asynchronously with NRZI encoded data which is found in systems such as the IBM 3650 Retail Store System. An SDLC loop configuration using iSBX 352 and iSBC 88/45 products is shown in Figure 1.

The two additional channels utilize the Intel 8274 Multi-Protocol Serial Controller (MPSC). The MPSC provides two independent half/full-duplex serial channels which provide asynchronous, synchronous, HDLC or SDLC protocol operations. The sync and async protocol operations are commonly used to communicate with inexpensive terminals and systems.

The three serial channels of the iSBC 88/45 ADCP board offer communications capability to manage a gateway application. The gateway application, as shown in Figure 1, manages diverse protocol requirements for data movement between channels. Typical protocol management software layers implemented by the user include SNA terminal interfaces to IBM systems.

#### **On-Board DMA**

For high-speed communications, one MPSC channel has a DMA capacity to support an 800K baud rate. The second channel attached to the MPSC is capable of simultaneous 800K baud operation when configured with DMA capability, but is connected to an RS232C interface which is defined as 20K baud maximum. Figure 2 shows an RS422A/449 multidrop application which supports high-speed operation.

#### **Interfaces Supported**

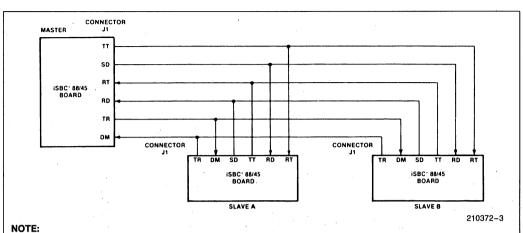

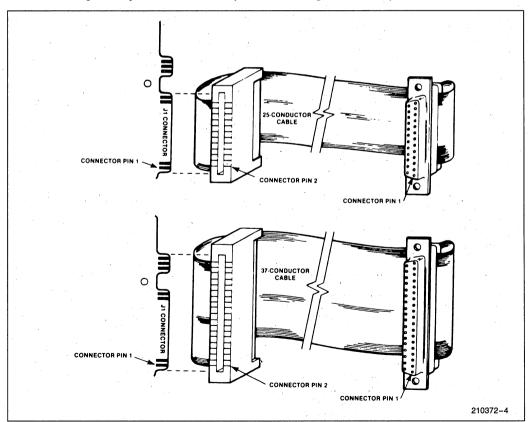

The iSBC 88/45 ADCP board provides an excellent foundation to support these electrical and diverse software drivers protocol interfaces. The control lines, serial data lines, and signal ground lines are brought out to the three double-edge connectors. Figure 3 shows the cable to connector construction. Two connectors are pre-configured for RS422A/ 449. All three channels are configurable for RS232C/CCITT V.24 interfaces as shown in Table 1.

Table 1. iSBC® 88/45 Supported Configurations

| Connection     | Synchronous |        | Asynchronous |             |

|----------------|-------------|--------|--------------|-------------|

| Connection     | Modem       | Direct | Modem*       | Direct      |

| Point-to-Point | X**         | Х      | X            | ΎΧ          |

| Multidrop      | х           | X      | Х            | Х           |

| Loop           | N.A.        | N.A.   | C<br>(Only)  | C<br>(Only) |

\*Modem should not respond to break. \*\*Channels A, B, and C denoted by X.

#### Figure 1. iSBC® 88/45 Gateway Processor Example

The last slave device in the system must contain termination resistors on all signal lines received by the slave board. The master device contains bias resistors on all signal lines.

Figure 2. Synchronous Multidrop Network Configuration Example—RS422A

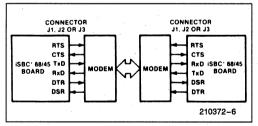

## Self Clocking Point-to-Point Interface

The iSBC 88/45 ADCP board is used in an asynchronous mode interface when configured as shown in Figure 4. The point-to-point RS232C example uses the self-clocking mode interface for NRZI encoding/decoding of data. The digital phase-lock loop allows operation of the interface in either halfduplex or full/duplex implementation with or without modems.

Figure 4. Self-Clocking or Asynchronous Pointto-Point Modem Interface Configuration Example—RS232C

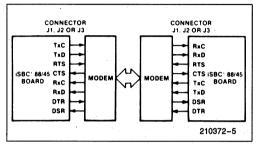

## Synchronous Point-to-Point Interface

Figure 5 shows a synchronous point-to-point mode of operation for the iSBC 88/45 ADCP board. This RS232C example uses a modem to generate the receive clock for coordination of the data transfer. The iSBC 88/45 ADCP board generates the transmit synchronizing clock for synchronous transmission.

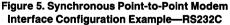

## **Central Processing Unit**

The central processor for the iSBC 88/45 Advanced Data Communications Processor board is Intel's iAPX 8088 microprocessor operating at 8 MHz. The microprocessor interface to other functions is illustrated in Figure 6. The microprocessor architecture is designed to effectively execute the application and networking software written in higher-level languages.

This architectural support includes four 16-bit byte addressable data registers, two 16-bit memory base pointer registers and two 16-bit index registers. These registers are addressable through 24 different operand addressing modes for comprehensive memory addressing and for high-level language data structure manipulation.

The stack-oriented architecture readily supports Intel's iRMX executives and iMMX multiprocessing software. Both software packages are designed for modular application programming. Facilitating the fast inter-module communications, the 4-byte instruction queue supports program constructs needed for real-time systems.

Since programs are segmented between pure procedure and data, four segment registers (code, stack, data, extra) are available for addressing 1 megabyte of memory space. These registers contain the offset values used to address a 64K byte segment. The registers are controlled explicitly through program control or implicitly by high-level language functions and instructions.

The real-time system software can also utilize the programmable timers as shown in Table 2 and various interrupt control modes available on the ADCP board to have responsive and effective application solutions.

| Function                       | Operation                                                                                                                          |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt on Terminal<br>Count | An interrupt is generated on<br>terminal count being reached.<br>This function is useful for<br>generation of real-time<br>clocks. |

| Rate Generator                 | Divide by N counter. Based<br>on the input clock period, the<br>output pulse remains low until<br>the count is expired.            |

| Square Wave<br>Generator       | Output remains high for one-<br>half the count, goes low for<br>the remainder of the count.                                        |

| Software Triggered<br>Strobe   | Output remains high until<br>count expires, then goes low<br>for one clock period.                                                 |

**Table 2. Programmable Timer Functions**

#### **Numeric Data Processor Extension**

The 8088 instruction set includes 8-bit and 16-bit signed and unsigned arithmetic operators for binary, BCD, and unpacked ASCII data. For enhanced numerics processing capability, the iSBC 337 MULTI-MODULE Numeric Data Processor extends the 8088 architecture and data set.

The extended numerics capability includes over 60 numeric instructions offering arithmetic, trigonometric, transcendental, logarithmic, and exponential instructions. Many math-oriented applications utilize the 16-, 32-, and 64-bit integer, 32- and 64-bit floating point, 18-digit packed BCD, and 80-bit temporary data types.

## **16K Bytes Static Ram**

The iSBC 88/45 ADCP board contains 16K bytes of high-speed static RAM, with 12K bytes dual-ported which is addressable from other MULTIBUS devices. When coupled with the high-speed DMA capability of the iSBC 88/45 ADCP board, the dual-ported memory provides effective data communication buffers. The dual-ported memory is useful for interprocessor message transfers.

#### Interrupt Capability

The iSBC 88/45 ADCP board provides nine vectored interrupt levels. The highest level is the NMI (Non-Maskable Interrupt) line. The additional eight interrupt levels are vectored via the Intel 8259A Programmable Interrupt Controller (PIC). As shown in Table 3, four priority processing modes are available to match interrupt servicing requirements. These modes and priority assignments are dynamically configurable by the system software.

| Mode              | Operation                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------|

| Nested            | Interrupt request line priorities fixed; interrupt 0 is the highest and 7 is the lowest.                            |

| Auto-Rotating     | The interrupt priority rotates;<br>once an interrupt is serviced it<br>becomes the lowest priority.                 |

| Specific Priority | System software assigns<br>lowest level priority. The other<br>levels are sequenced based on<br>the level assigned. |

| Polled            | System software examines<br>priority interrupt via interrupt<br>status register.                                    |

| Т | ab | le | 3. | Prog | gram | mable | Interru | pt Modes |

|---|----|----|----|------|------|-------|---------|----------|

|   |    |    |    |      |      |       |         |          |

Figure 6. Block Diagram of the iSBC® 88/45 ADCP Board

#### Interrupt Request Generation

Listed in Table 4 are the devices and functions supported by interrupts on the iSBC 88/45 ADCP board. All interrupt signals are brought to the interrupt jumper matrix. Any of the 23 interrupt sources are strapped to the appropriate 8259A PIC request level. The PIC resolves requests according to the software selected mode and, if the interrupt is unmasked, issues an interrupt to the CPU.

## **EPROM/RAM Expansion**

In addition to the on-board RAM, the iSBC 88/45 ADCP board provides four 28-pin JEDEC sockets for EPROM expansion. By using 2764 EPROMs, the board has 32K bytes of program storage. Three of the JEDEC standard sockets also support byte-wide static RAMs or iRAMs; using 8K x 8 static RAMs provides an additional 24K bytes of RAM.

Inserting the optional iSBC 341 MULTIMODULE EPROM expansion board onto the iSBC 88/45 ADCP board provides four additional 28-pin JEDEC sites. This expansion doubles the available program storage or extends the RAM capability by 32K bytes.

## **ISBX™ MULTIMODULE™ Expansion**

Two 8-bit iSBX MULTIMODULE connectors are provided on the iSBC 88/45 microcomputer. Through these connectors, additional iSBX functions extend the I/O capability of the microcomputer. The iSBX connectors provide the necessary signals to interface to the local bus. In addition to specialized or custom designed iSBX boards, the customer has a broad range of Intel iSBC MULTIMODULEs available, including parallel I/O, analog I/O, iEEE 488 GPIB, floppy disk, magnetic bubbles, video, and serial I/O boards.

The serial I/O MULTIMODULE boards include the iSBX 351 (one ASYNC/SYNC serial channel) the ISBX 352 (one HDLC/SDLC serial channel) and the ISBX 354 (two SYNC/ASYNC, HDLC/SDLC serial channels) boards. Adding two ISBX 352 MULTI-MODULE boards to the ISBC 88/45 ADCP provides a total of five HDLC/SDLC channels.

## **MULTIBUS®** Multimaster Capabilities

#### OVERVIEW

The MULTIBUS system is Intel's industry standard microcomputer bus structure. Both 8- and 16-bit single board computers are supported on the MULTI-BUS structure with 24 address and 16 data lines. In addition to expanding functions contained on a single board computer (e.g., memory and digital I/O), the MULTIBUS structure allows very powerful distributed processing configurations with multiple processors, intelligent slaves, and peripheral boards.

#### **Multimaster Capability**

The iSBC 88/45 ADCP board provides full MULTI-BUS arbitration control logic. This control

| Device                                  | Function                                                                              | No. of<br>Interrupts |

|-----------------------------------------|---------------------------------------------------------------------------------------|----------------------|

| MULTIBUS Interface                      | Select 1 interrupt from MULTIBUS resident peripherals<br>or other CPU boards.         | 8                    |

| 8273 HDLC/SDLC<br>Controller            | Transmit buffer empty and receive buffer full                                         | 2                    |

| 8274 HDLC/SDLC<br>SYNC/ASYNC Controller | Software examines register for status of communication operation                      | 1                    |

| 8254-Timer                              | Counter 2 of both PIT devices                                                         | 2                    |

| iSBX Connectors                         | Function determined by iSBX MULTIMODULE Board<br>(2 interrupts per socket)            | 4                    |

| Bus Fail Safe Timer                     | Indicates MULTIBUS addressed device has not<br>responded to command within 4 msec     | 1                    |

| Power Line Clock                        | Source of 60 MHz signal from power supply                                             | 1                    |

| Bus Flag Interrupt                      | Flag interrupt in byte location 1000H signals board reset<br>or data handling request | 2                    |

| iSBC 337A Board                         | Numeric Data Processor generated status information 1                                 |                      |

| 8237A-5                                 | Signals end of 8237 DMA operation                                                     |                      |

#### Table 4. Interrupt Request Sources

logic allows up to three iSBC 88/45 ADCP boards or other bus masters, including iSBC 286, iSBC 86 and iSBC 86 family boards to share the system bus using a serial (daisy chain) priority scheme. By using an external parallel priority decoder, the MULTIBUS system bus could be shared among sixteen masters.

The Intel standard MULTIBUS Interprocessor Protocol (MIP) software, implemented as the Intel iMMX 800 package for iRMX 86 and iRMX 88 Real-Time Executives, fully supports multiple 8- and 16-bit distributed processor functions. The software manages the message passing protocol between microprocessors.

#### System Development Capabilities

The application development cycle for an iSBC 88/45 ADCP board is reduced and simplified through the usage of several Intel tools. The tools include the Intellec Series Microcomputer Development System, the ICE-88 In-Circuit Emulator, the iSDM 86 debug monitor software, and the iRMX 86 and iRMX 88 run-time support packages.

The Intellec Series Microcomputer Development System offers a complete development environment for the ISBC 88/45 software. In addition to the operating system, assembler, utilities and application debugger features provided with the system, the user optionally can utilize higher-level languages like PL/M, PASCAL, and FORTRAN.

The ICE-88 In-Circuit Emulator provides a link between the Intellec system and the target iSBC 88/45-based system for code loading and execution. The ICE-88 package assists the developer with the debugging and system integrating processes.

## **Run-Time Building Blocks**

Intel offers run-time foundation software to support applications which range from general purpose to high-performance solutions. The iRMX 88 Real-time Multitasking Executive provides a multitasking structure which includes task scheduling, task management, intertask communications, and interrupt servicing for high-performance applications. The highly configurable modules make the system tailoring job easier whether one uses the compact executive or the complete executive with its variety of peripheral devices supported.

The iRMX 86 Operating System provides a very rich set of features and options to support sophisticated applications solutions. In addition to supporting realtime requirements, the iRMX 86 Operating System has a powerful, but easy-to-use human interface. When added to the sophisticated I/O system, the iRMX 86 Operating System is readily extended to support assembler, PL/M, PASCAL, and FOR-TRAN software development environments. The modular building block software lends itself well to customized application solutions.

#### SPECIFICATIONS

#### **Word Size**

Instruction: 8, 16, 24, or 32 bits Data: 8 or 16 bits

#### System Clock

8 MHz: ±0.1%

#### NOTE:

Jumper selectable for 4 MHz operation with iSBC 337 Numeric Data Processor module or ICE-88 product.

#### **Cycle Time**

Basic Instruction Cycle at 8.00 MHz: 1.25  $\mu$ s, 250 ns (assumes instruction in the queue)

#### NOTE:

Basic instruction cycle is defined as the fastest instruction time (i.e., two clock cycles).

## **Memory Cycle Time**

RAM: 500 ns (no wait states) EPROM: jumper selectable from 500 ns to 625 ns.

#### **On-Board RAM\***

| K Bytes          | Hex Address<br>Range |

|------------------|----------------------|

| 16 (total)       | 0000-3FFF            |

| 12 (dual-ported) | 1000-3FFF            |

\*Four iSBC 88/45 EPROM sockets support JEDEC 24/28pin standard EPROMs and RAMs (3 sockets); iSBC 341 (4 sockets)

## **Environmental Characteristics**

Temperature:  $0^{\circ}$ C to  $+55^{\circ}$ C, free moving air across the base board and MULTIMODULE board

Humidity: 90%, non-condensing

## **Physical Characteristics**

Width: 30.48 cm (12.00 in) Length: 17.15 cm (6.75 in) Height: 1.50 cm (0.59 in) Weight: 6.20 gm (22 oz)

## Memory Capacity/Addressing

#### **On-Board EPROM\***

| Device | Total<br>K Bytes | Hex Address<br>Range |

|--------|------------------|----------------------|

| 2716   | 8                | FE000-FFFFF          |

| 2732A  | 16               | FC000-FFFFF          |

| 2764   | 32               | F8000-FFFFF          |

| 27128  | 64               | F0000-FFFFF          |

#### With optional iSBC® 341 MULTIMODULE™ EPROM

| Total<br>K Bytes | Hex Address<br>Range      |

|------------------|---------------------------|

| 16               | FC000-FFFFF               |

| 32               | F8000-FFFFF               |

| 64               | F0000-FFFFF               |

| 128              | E0000-FFFFF               |

|                  | K Bytes<br>16<br>32<br>64 |

\*Four iSBC 88/45 EPROM sockets support JEDEC 24/28pin standard EPROMs and RAMs (static and iRAM, 3 sockets); iSBC 341 sockets also support EPROMs and RAMs.

Timer Input Frequency-8.00 MHz ±0.1%

## Interfaces

iSBX™ Bus—All signals TTL compatible

#### Serial RS232C Signals-

| CTS     | CLEAR TO SEND       |  |

|---------|---------------------|--|

| DSR     | DATA SET READY      |  |

| DTE TXC | TRANSMIT CLOCK      |  |

| DTR     | DATA TERMINAL READY |  |

| FG      | FRAME GROUND        |  |

| RTS     | REQUEST TO SEND     |  |

| RXC     | RECEIVE CLOCK       |  |

| RXD     | RECEIVE DATA        |  |

| SG      | SIGNAL GROUND       |  |

| TXD     | TRANSMIT DATA       |  |

Serial RS422A/449 Signals-

| CS<br>DM | CLEAR TO SEND   |

|----------|-----------------|

| BC ·     | RECEIVE COMMON  |

| HU I     | RECEIVE COMMON  |

| RD       | RECEIVE DATA    |

| RS       | REQUEST TO SEND |

| RT       | RECEIVE TIMING  |

| SC       | SEND COMMON     |

| SD       | SEND DATA       |

| SG       | SIGNAL GROUND   |

| TR       | TERMINAL READY  |

| TT       | TERMINAL TIMING |

## **Electrical Characteristics**

DC Power Dissipation-28.3 Watts

#### **DC Power Requirements**

| Configuration                   | (All Vo | Require<br>Ditages ±<br>+ 12V | 5%)     |

|---------------------------------|---------|-------------------------------|---------|

| Without EPROM <sup>(1)</sup>    | 5.1A    | 20 mA                         | 20 mA   |

| With 8K EPROM<br>(Using 2716)   | +0.14A  | *.<br>                        |         |

| With 16K EPROM<br>(Using 2732A) | +0.20A  | _                             | <u></u> |

| With 32K EPROM<br>(Using 2764)  | +0.24A  |                               |         |

| With 64K EPROM<br>(Using 27128) | +0.24A  | <br>                          |         |

| NOTE:                           | · •     |                               |         |

1. AS SHIPPED—no EPROMs in sockets, no iSBC 341 module. Configuration includes terminators for two RS422A/449 and one RS232C channels.

## **Serial Communication Characteristics**

| Channel  | Device  | Supported<br>Interface             | Max. Baud<br>Rate                                      |

|----------|---------|------------------------------------|--------------------------------------------------------|

| <b>A</b> | 8274(1) | RS232C                             | 800K SDLC/HDLC<br>125K Synchronous<br>50K Asynchronous |

| В        | 8274    | RS232C<br>CCITT V.24               | 125K Synchronous <sup>(2)</sup><br>50K Asynchronous    |

| С        | 8273(3) | RS442A/449<br>RS232C<br>CCITT V.24 | 64K SDLC/HDLC <sup>(3)</sup><br>9.6K SELF CLOCKING     |

#### NOTES:

1. 8274 supports HDLC/SDLC/SYNC/ASYNC multiprotocol

2. Exceed RS232C/CCITT V.24 rating of 20K baud 3. 8273 supports HDLC/SDLC

#### BAUD RATE EXAMPLES (Hz)

| 8254<br>Timer Divide<br>Count N | Synchronous<br>K Baud | Asynchronous<br>÷ 16 ÷ 32 ÷ 64<br>K Baud |                   |          |

|---------------------------------|-----------------------|------------------------------------------|-------------------|----------|

| 10                              | 800                   | 50.0                                     | 25.0              | 12.5     |

| 26                              | 300                   | 19.2                                     | 9.6               | 4.8      |

| 31                              | 256                   | 16.1                                     | 8.06              | 4.03     |

| 52                              | 154                   | 9.6                                      | 4.8               | 2.4      |

| 104                             | 76.8                  | 4.8                                      | 2.4               | 1.2      |

| 125                             | 64                    | 4.0                                      | 2.0               | 1.0      |

| 143                             | 56                    | 3.5                                      | 1.7               | 0.87     |

| 167                             | 48                    | 3.0                                      | 1.5               | 0.75     |

| 417                             | 19.2                  | · · · · · ·                              | <u>ا کې ا</u> ر ۲ | * ,      |

| 833                             | 9.6                   | * <u> </u>                               | · · · · · ·       | <u> </u> |

| EQUATION                        | 8,000,000             | 500K                                     | 250K              | 125K     |

| EQUATION                        | N                     | N                                        | N                 | N        |

| Interface | Mode <sup>(1)</sup> | MULTIMODULE™<br>Edge Connector       | Cable                      | Connector                            |  |

|-----------|---------------------|--------------------------------------|----------------------------|--------------------------------------|--|

| RS232C    | DTE                 | 26-pin <sup>(4)</sup> , 3M-3462-0001 | 3M <sup>(2)</sup> -3349/25 | 25-pin <sup>(6)</sup> , 3M-3482-1000 |  |

| RS232C    | DCE                 | 26-pin <sup>(4)</sup> , 3M-3462-0001 | 3M <sup>(2)</sup> -3349/25 | 25-pin <sup>(6)</sup> , 3M-3483-1000 |  |

| RS449     | DTE                 | 40-pin <sup>(5)</sup> , 3M-3464-0001 | 3M <sup>(3)</sup> -3349/37 | 37-pin <sup>(7)</sup> , 3M-3502-1000 |  |

| RS449     | DCE                 | 40-pin <sup>(5)</sup> , 3M-3464-0001 | 3M(3)-3349/37              | 37-pin <sup>(7)</sup> , 3M-3503-1000 |  |

#### SERIAL INTERFACE CONNECTORS

#### NOTES:

1. DTE-Data Terminal Equipment Mode (male connector); DCE-Data Circuit Equipment mode (female connector) requires line swaps.

2. Cable is tapered at one end to fit the 3M-3462 connector.

3. Cable is tapered to fit 3M-3464 connector.

4. Pin 26 of the edge connector is not connected to the flat cable.

5. Pins 38, 39, and 40 of the edge connector are not connected to the flat cable.

6. May be used with the cable housing 3M-3485-1000.

7. Cable housing 3M-3485-4000 may be used wih the connector.

#### Line Drivers (Supplied)

| Device | Characteristic | Qty | Installed |

|--------|----------------|-----|-----------|

| 1488   | RS232C         | 3   | 1         |

| 1489   | RS232C         | 3   | 1         |

| 3486   | RS422A         | 2   | 2         |

| 3487   | RS422A         | 2   | 2         |

#### **Reference Manual**

**143824**—iSBC 88/45 Advanced Data Communications Processor Board Hardware Reference Manual (not supplied).

Reference manuals may be ordered from any Intel sales representative, distributor office or from Intel Literature Department, 3065 Bowers Avenue, Santa Clara, CA 95051.

## **ORDERING INFORMATION**

#### Part Number Description

SBC 88/45

8-bit 8088-based Single Board Computer with 3 HDLC/SDLC serial channels