# 8206 ERROR DETECTION AND CORRECTION UNIT

- Detects All Single Bit, and Double Bit and Most Multiple Bit Errors

- Corrects All Single Bit Errors

| <b>3 Selections</b> | 8206-1 | 8206  |

|---------------------|--------|-------|

| Detection           | 35 ns  | 42 ns |

| Correction          | 55 ns  | 67 ns |

- Syndrome Outputs for Error Logging

- Automatic Error Scrubbing with 8207

- Expandable to Handle 80 Bit Memories

- Separate Input and Output Busses—No Timing Strobes Required

- Supports Read With and Without Correction, Writes, Partial (Byte) Writes, and Read-Modify-Writes

- HMOS III Technology for Low Power

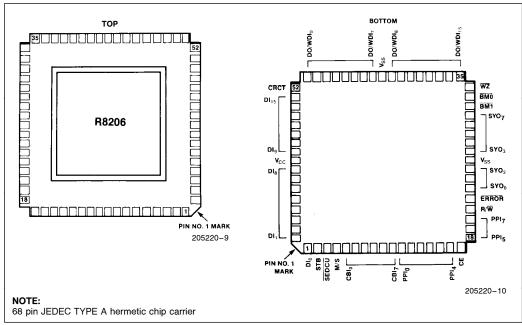

- 68 Pin Leadless JEDEC Package

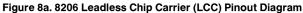

- 68 Pin Grid Array Package

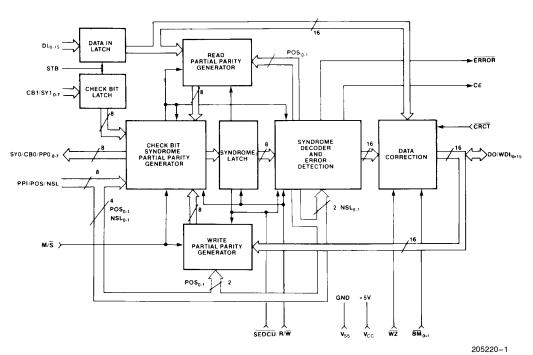

The HMOS 8206 Error Detection and Correction Unit is a high-speed device that provides error detection and correction for memory systems (static and dynamic) requiring high reliability and performance. Each 8206 handles 8 or 16 data bits and up to 8 check bits. 8206's can be cascaded to provide correction and detection for up to 80 bits of data. Other 8206 features include the ability to handle byte writes, memory initialization, and error logging.

Figure 1. 8206 Block Diagram

September 1987

Order Number: 205220-008

|                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |                                                                    | Table 1. 8206 Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                            | Pin No.                                                                                      | Туре                                                               | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DI <sub>0-15</sub>                                                                                                                                                                                                                                                                                                                                                                                                                | 1, 68-61,<br>59-53                                                                           | I                                                                  | <b>DATA IN:</b> These inputs accept a 16 bit data word from RAM for error detection and/or correction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CBI/SYI0<br>CBI/SYI1<br>CBI/SYI2<br>CBI/SYI3<br>CBI/SYI4<br>CBI/SYI5<br>CBI/SYI6<br>CBI/SYI7                                                                                                                                                                                                                                                                                                                                      | 5<br>6<br>7<br>8<br>9<br>10<br>11<br>12                                                      |                                                                    | <b>CHECK BITS IN/SYNDROME IN:</b> In a single 8206 system, or in the master in a multi-8206 system, these inputs accept the check bits (5 to 8) from the RAM. In a single 8206 16 bit system, $CBI_{0-5}$ are used. In slave 8206's these inputs accept the syndrome from the master.                                                                                                                                                                                                                                                                                                                                                                                                   |

| DO/WDI <sub>0</sub><br>DO/WDI <sub>1</sub><br>DO/WDI <sub>2</sub><br>DO/WDI <sub>3</sub><br>DO/WDI <sub>5</sub><br>DO/WDI <sub>5</sub><br>DO/WDI <sub>6</sub><br>DO/WDI <sub>7</sub><br>DO/WDI <sub>7</sub><br>DO/WDI <sub>8</sub><br>DO/WDI <sub>9</sub><br>DO/WDI <sub>10</sub><br>DO/WDI <sub>11</sub><br>DO/WDI <sub>12</sub><br>DO/WDI <sub>12</sub><br>DO/WDI <sub>13</sub><br>DO/WDI <sub>14</sub><br>DO/WDI <sub>15</sub> | 51<br>50<br>49<br>48<br>47<br>46<br>45<br>44<br>42<br>41<br>40<br>39<br>38<br>37<br>36<br>35 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | <b>DATA OUT/WRITE DATA IN:</b> In a read cycle, data accepted by $DI_{0-15}$ appears at these outputs corrected if CRCT is low, or uncorrected if CRCT is high. The BM inputs must be high to enable the output buffers during the read cycle. In a write cycle, data to be written into the RAM is accepted by these inputs for computing the write check bits. In a partial-write cycle, the byte not to be modified appears at either $DO_{0-7}$ if $\overline{BM}_0$ is high, or $DO_{8-15}$ if $\overline{BM}_1$ is high, for writing to the RAM. When $\overline{WZ}$ is active, it causes the 8206 to output all zeros at $DO_{0-15}$ , with the proper write check bits on CBO. |

| SYO/CBO/PPO0<br>SYO/CBO/PPO1<br>SYO/CBO/PPO2<br>SYO/CBO/PPO3<br>SYO/CBO/PPO4<br>SYO/CBO/PPO5<br>SYO/CBO/PPO6<br>SYO/CBO/PPO7                                                                                                                                                                                                                                                                                                      | 23<br>24<br>25<br>27<br>28<br>29<br>30<br>31                                                 | 00000000                                                           | SYNDROME OUT/CHECK BITS OUT/PARTIAL PARITY OUT: In a single 8206 system, or in the master in a multi-8206 system, the syndrome appears at these outputs during a read. During a write, the write check bits appear. In slave 8206's the partial parity bits used by the master appear at these outputs. The syndrome is latched (during read-modify-writes) by R/W going low.                                                                                                                                                                                                                                                                                                           |

| PPI <sub>0</sub> /POS <sub>0</sub><br>PPI <sub>1</sub> /POS <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                          | 13<br>14                                                                                     |                                                                    | <b>PARTIAL PARITY IN/POSITION:</b> In the master in a multi-8206 system, these inputs accept partial parity bits 0 and 1 from the slaves. In a slave 8206 these inputs inform it of its position within the system (1 to 4). Not used in a single 8206 system.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PPI <sub>2</sub> /NSL <sub>0</sub><br>PPI <sub>3</sub> /NSL <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                          | 15<br>16                                                                                     | l                                                                  | <b>PARTIAL PARITY IN/NUMBER OF SLAVES:</b> In the master in a multi-8206 system, these inputs accept partial parity bits 2 and 3 from the slaves. In a multi-8206 system these inputs are used in slave number 1 to tell it the total number of slaves in the system (1 to 4). Not used in other slaves or in a single 8206 system.                                                                                                                                                                                                                                                                                                                                                     |

| PPI <sub>4</sub> CE                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                                                           | Ι/Ο                                                                | <b>PARTIAL PARITY IN/CORRECTABLE ERROR:</b> In the master in a multi-8206 system this pin accepts partial parity bit 4. In slave number 1 only, or in a single 8206 system, this pin outputs the correctable error flag. CE is latched by R/W going low. Not used in other slaves.                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 1. 8206 Pin Description

| Table 1. 8206 Pin Descrip | otion (Continued) |

|---------------------------|-------------------|

|---------------------------|-------------------|

| [                                                        |                |      |                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                                   | Pin No.        | Туре | Name and Function                                                                                                                                                                                                                                                                                   |

| PPI <sub>5</sub><br>PPI <sub>6</sub><br>PPI <sub>7</sub> | 18<br>19<br>20 |      | <b>PARTIAL PARITY IN:</b> In the master in a multi-8206 system these pins accept partial parity bits 5 to 7. The number of partial parity bits equals the number of check bits. Not used in single 8206 systems or in slaves.                                                                       |

| ERROR                                                    | 22             | 0    | <b>ERROR:</b> This pin outputs the error flag in a single 8206 system or in the master of a multi-8206 system. It is latched by $R/W$ going low. Not used in slaves.                                                                                                                                |

| CRCT                                                     | 52             | I    | <b>CORRECT:</b> When low this pin causes data correction during a read or read-modify-write cycle. When high, it causes error correction to be disabled, although error checking is still enabled.                                                                                                  |

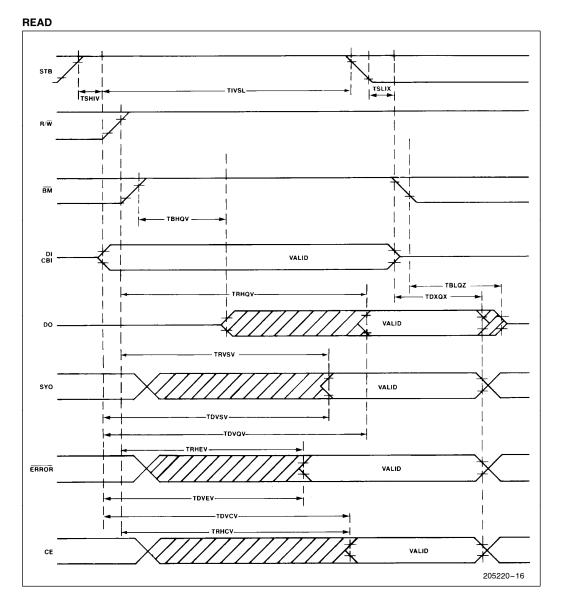

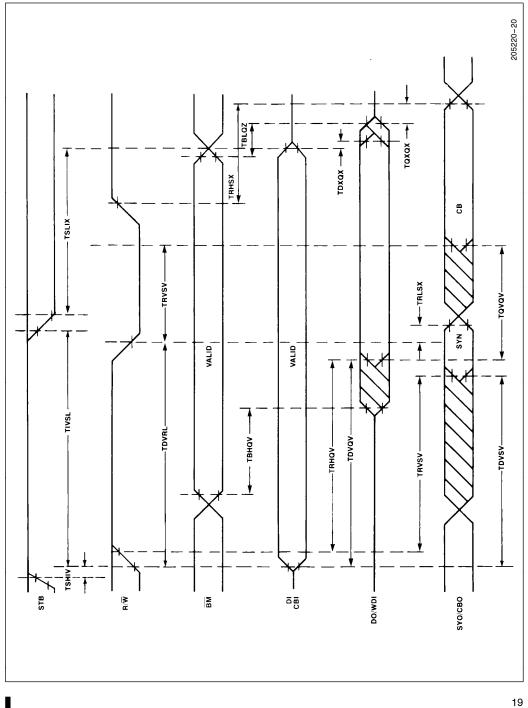

| STB                                                      | 2              | Ι    | <b>STROBE:</b> STB is an input control used to strobe data at the DI inputs and check-bits at the CBI/SYI inputs. The signal is active high to admit the inputs. The signals are latched by the high-to-low transition of STB.                                                                      |

| BM <sub>0</sub><br>BM <sub>1</sub>                       | 33<br>32       |      | <b>BYTE MARKS:</b> When high, the Data Out pins are enabled for a read cycle. When low, the Data Out buffers are tristated for a write cycle. $BM_0$ controls $DO_{0-7}$ , while $BM_1$ controls $DO_{8-15}$ . In partial (byte) writes, the byte mark input is low for the new byte to be written. |

| R/₩                                                      | 21             | I    | <b>READ/WRITE:</b> When high this pin causes the 8206 to perform detection and correction (if $\overline{CRCT}$ is low). When low, it causes the 8206 to generate check-bits. On the high-to-low transition the syndrome is latched internally for read-modify-write cycles.                        |

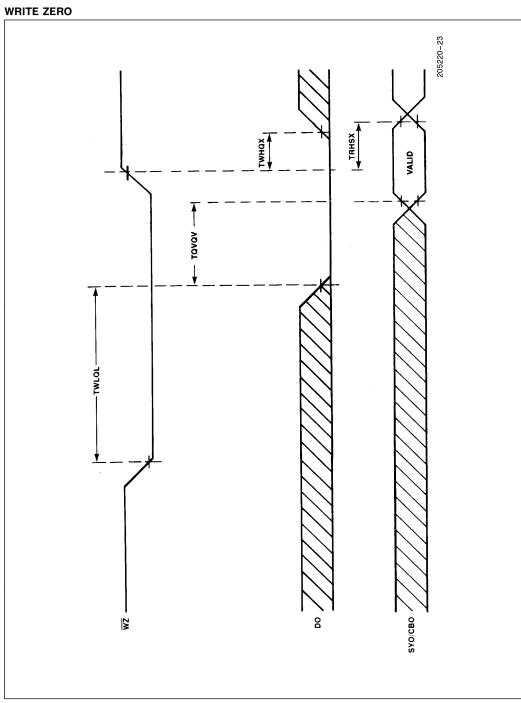

| WZ                                                       | 34             | I    | <b>WRITE ZERO:</b> When low this input overrides the $\overline{BM}_{0-1}$ and $R/\overline{W}$ inputs to cause the 8206 to output all zeros at DO <sub>0-15</sub> with the corresponding check-bits at CBO <sub>0-7</sub> . Used for memory initialization.                                        |

| M/S                                                      | 4              | I    | <b>MASTER/SLAVE:</b> Input tells the 8206 whether it is a master (high) or a slave (low).                                                                                                                                                                                                           |

| SEDCU                                                    | 3              | I    | <b>SINGLE EDC UNIT:</b> Input tells the master whether it is operating as a single 8206 (low) or as the master in a multi-8206 system (high). Not used in slaves.                                                                                                                                   |

| V <sub>CC</sub>                                          | 60             | I    | POWER SUPPLY: +5V                                                                                                                                                                                                                                                                                   |

| V <sub>SS</sub>                                          | 26             | I    | LOGIC GROUND                                                                                                                                                                                                                                                                                        |

| V <sub>SS</sub>                                          | 43             | I    | OUTPUT DRIVER GROUND                                                                                                                                                                                                                                                                                |

### FUNCTIONAL DESCRIPTION

The 8206 Error Detection and Correction Unit provides greater memory system reliability through its ability to detect and correct memory errors. It is a single chip device that can detect and correct all single bit errors and detect all double bit and some higher multiple bit errors. Some other odd multiple bit errors (e.g., 5 bits in error) are interpreted as single bit errors, and the CE flag is raised. While some even multiple bit errors (e.g., 4 bits in error) are interpreted as no error, most are detected as double bit errors. This error handling is a function of the number of check bits used by the 8206 (see Figure 2) and the specific Hamming code used. Errors in a word.

For more information on error correction codes, see Intel Application Notes AP-46 and AP-73.

A single 8206 handles 8 or 16 bits of data, and up to 5 8206's can be cascaded in order to handle data paths of 80 bits. For a single 8206 8 bit system, the  $DI_{8-15}$ ,  $DO/WDI_{8-15}$  and  $\overline{BM}_1$  inputs are grounded. See the Multi-Chip systems section for information on 24-80 bit systems.

The 8206 has a "flow through" architecture. It supports two kinds of error correction architecture: 1) Flow-through, or correct-always; and 2) Parallel, or check-only. These are two separate 16-pin busses,

| Data Word Bits | Check Bits |

|----------------|------------|

| 8              | 5          |

| 16             | 6          |

| 24             | 6          |

| 32             | 7          |

| 40             | 7          |

| 48             | 8          |

| 56             | 8          |

| 64             | 8          |

| 72             | 8          |

| 80             | 8          |

### Figure 3. Number of Check Bits Used by 8206

one to accept data from the RAM (DI) and the other to deliver corrected data to the system bus (DO/ WDI). The logic is entirely combinatorial during a read cycle. This is in contrast to an architecture with only one bus, with bidirectional bus drivers that must first read the data and then be turned around to output the corrected data. The latter architecture typically requires additional hardware (latches and/or transceivers) and may be slower in a system due to timing skews of control signals. With the  $R/\overline{W}$  pin high, data is received from the RAM outputs into the DI pins where it is optionally latched by the STB signal. Check bits are generated from the data bits and compared to the check bits read from the RAM into the CBI pins. If an error is detected the ERROR flag is activated and the correctable error flag (CE) is used to inform the system whether the error was correctable or not. With the BM inputs high, the word appears corrected at the DO pins if the error was uncorrectable.

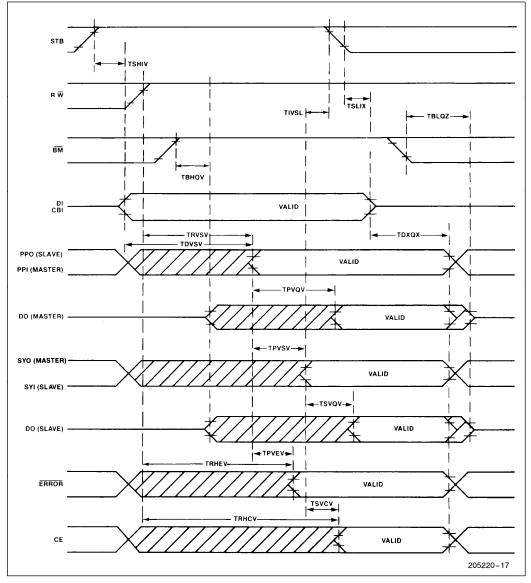

If more than one 8206 is being used, then the check bits are read by the master. The slaves generate a partial parity output (PPO) and pass it to the master. The master 8206 then generates and returns the syndrome to the slaves (SYO) for correction of the data.

The 8206 may alternatively be used in a "checkonly" mode with the  $\overline{CRCT}$  pin left high. With the correction facility turned off, the propagation delay from memory outputs to 8206 outputs is significantly shortened. In this mode the 8206 issues an ERROR flag to the CPU, which can then perform one of several options: lengthen the current cycle for correction, restart the instruction, perform a diagnostic routine, etc.

A syndrome word, five to eight bits in length and containing all necessary information about the existence and location of an error, is made available to the system at the  $SYO_{0-7}$  pins. Error logging may be accomplished by latching the syndrome and the memory address of the word in error.

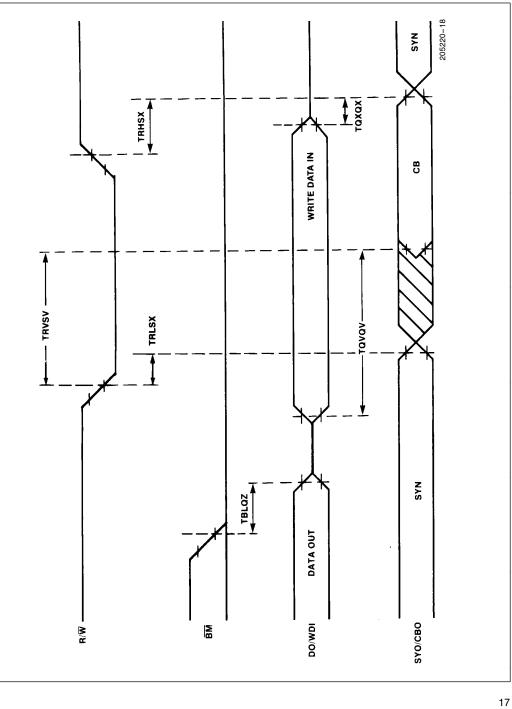

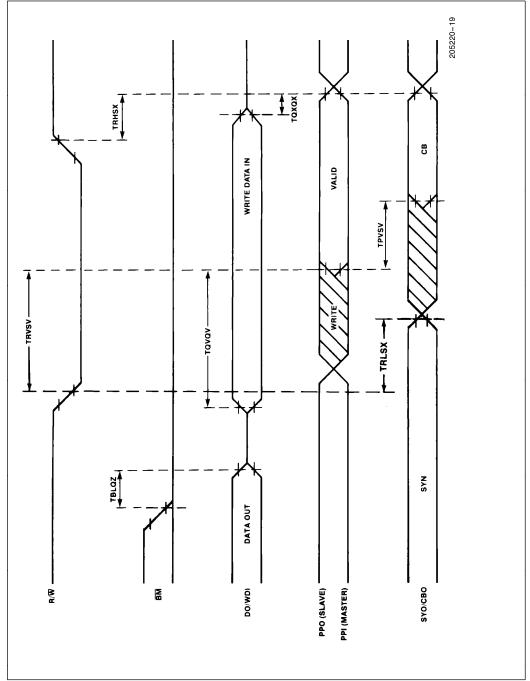

## WRITE CYCLE

For a full write, in which an entire word is written to memory, the data is written directly to the RAM, bypassing the 8206. The same data enters the 8206 through the WDI pins where check bits are generated. The Byte Mark inputs must be low to tristate the DO drivers. The check bits, 5 to 8 in number, are then written to the RAM through the CBO pins for storage along with the data word. In a multi-chip system, the master writes the check bits using partial parity information from the slaves.

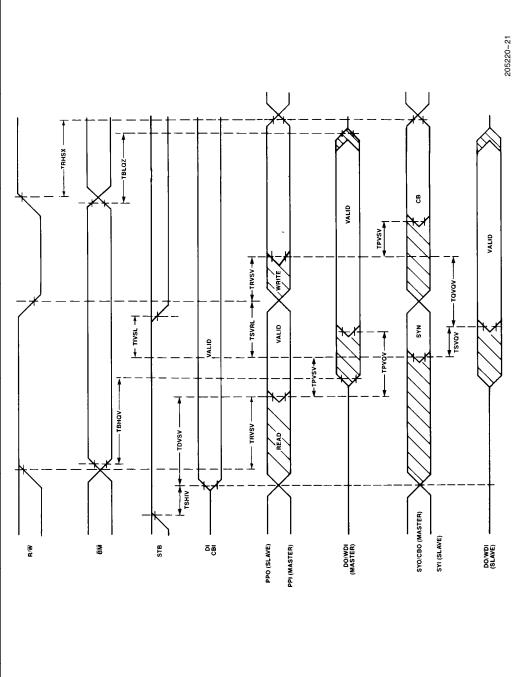

In a partial write, part of the data word is overwritten, and part is retained in memory. This is accomplished by performing a read-modify-write cycle. The complete old word is read into the 8206 and corrected, with the syndrome internally latched by R/W going low. Only that part of the word not to be modified is output onto the DO pins, as controlled by the Byte Mark inputs. That portion of the word to be overwrit-

ten is supplied by the system bus. The 8206 then calculates check bits for the new word, using the byte from the previous read and the new byte from the system bus, and writes them to the memory.

### **READ-MODIFY-WRITE CYCLES**

Upon detection of an error the 8206 may be used to correct the bit in error in memory. This reduces the probability of getting multiple-bit errors in subsequent read cycles. This correction is handled by executing read-modify-write cycles.

The read-modify-write cycle is controlled by the  $R/\overline{W}$  input. After (during) the read cycle, the system dynamic RAM controller or CPU examines the 8206 ERROR and CE outputs to determine if a correctable error occurred. If it did, the dynamic RAM controller or CPU forces  $R/\overline{W}$  low, telling the 8206 to latch the generated syndrome and drive the corrected check bits onto the CBO outputs. The corrected ler then writes the corrected data and corresponding check bits into memory.

The 8206 may be used to perform read-modifywrites in one or two RAM cycles. If it is done in two cycles, the 8206 latches are used to hold the data and check bits from the read cycle to be used in the following write cycle. The Intel 8207 Dual Port Dynamic RAM controller allows read-modify-write cycles in one memory cycle. See the System Environment section.

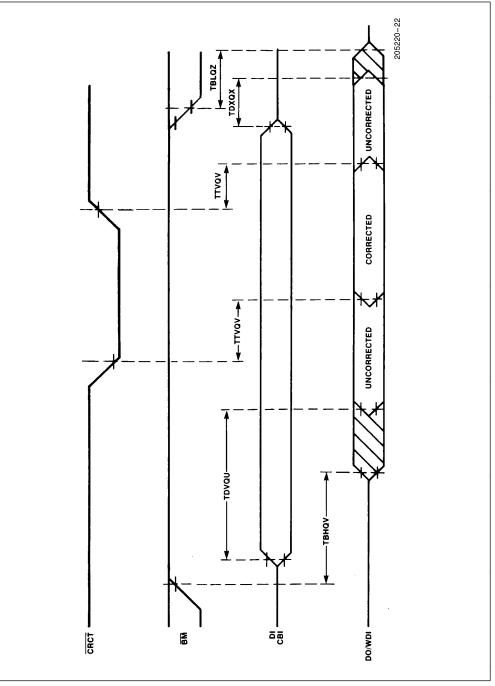

## INITIALIZATION

A memory system operating with ECC requires some form of initialization at system power-up in order to set valid data and check bit information in memory. The 8206 supports memory initialization by the write zero function. By activating the  $\overline{WZ}$  pin, the 8206 will write a data pattern of zeros and the associated check bits in the current write cycle. By thus writing to all memory at power-up, a controller can set memory to valid data and check bits. Massive memory failure, as signified by both data and check bits all ones or zeros, will be detected as an uncorrectable error.

### **MULTI-CHIP SYSTEMS**

A single 8206 handles 8 or 16 bits of data and 5 or 6 check bits, respectively. Up to 5 8206's can be cascaded for 80 bit memories with 8 check bits.

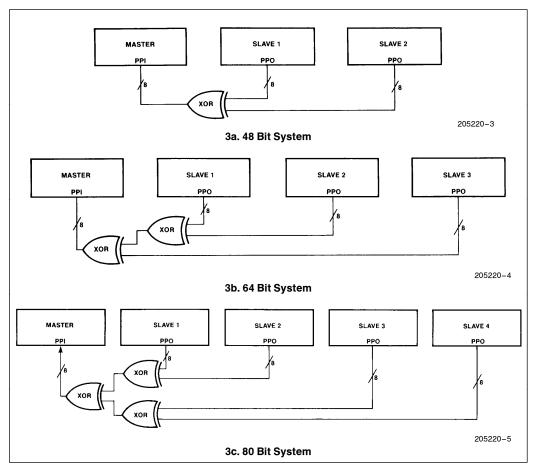

When cascaded, one 8206 operates as a master, and all others as slaves. As an example, during a read cycle in a 32 bit system with one master and one slave, the slave calculates parity on its portion master through the PPO pins. The master combines the partial parity from the slave with the parity it calculated from its own portion of the word to generate the syndrome. The syndrome is then returned by the master to the slave for error correction. In systems with more than one slave the above description continues to apply, except that the partial parity outputs of the slaves must be XOR'd externally. Figure 4 shows the necessary external logic for multi-chip systems. Write and read-modify-write cycles are carried out analogously. See the System Operation section for multi-chip wiring diagrams.

There are several pins used to define whether the 8206 will operate as a master or a slave. Tables 3 and 4 illustrate how these pins are tied.

6

Figure 4. External Logic for Multi-Chip Sytems

| Pin No. | Pin Name                           | Master | Slave 1 | Slave 2 | Slave 3 | Slave 4 |

|---------|------------------------------------|--------|---------|---------|---------|---------|

| 4       | M/S                                | + 5V   | gnd     | gnd     | gnd     | gnd     |

| 3       | SEDCU                              | + 5V   | + 5V    | + 5V    | + 5V    | + 5V    |

| 13      | PPI0/POS0                          | PPI    | gnd     | + 5V    | gnd     | + 5V    |

| 14      | PPI1/POS1                          | PPI    | gnd     | gnd     | + 5V    | + 5V    |

| 15      | PPI <sub>2</sub> /NSL <sub>0</sub> | PPI    | *       | + 5V    | + 5V    | + 5V    |

| 16      | PPI3/NSL1                          | PPI    | *       | + 5V    | + 5V    | + 5V    |

NOTE:

Pins 13, 14, 15, 16 have internal pull-up resistors and may be left as N.C. where specified as connecting to +5V.

Table 4. NSL Pin Assignments for Slave 1

|                                                                          | N          | umber of Slaves |             |              |

|--------------------------------------------------------------------------|------------|-----------------|-------------|--------------|

| Pin                                                                      | 1          | 2               | 3           | 4            |

| PPI <sub>2</sub> /NSL <sub>0</sub><br>PPI <sub>3</sub> /NSL <sub>1</sub> | GND<br>GND | + 5V<br>GND     | GND<br>+ 5V | + 5V<br>+ 5V |

The timing specifications for multi-chip systems must be calculated to take account of the external XOR gating in 3, 4 and 5-chip systems. Let tXOR be the delay for a single external TTL XOR gate. Then the following equations show how to calculate the relevant timing parameters for 2-chip (n = 0), 3-chip (n = 1), 4-chip (n = 2), and 5-chip (n = 2) systems:

Data-in to corrected data-out (read cycle) =

TDVSV + TPVSV + TSVQV + ntXOR

Data-in to error flag (read cycle) =

TDVSV + TPVEV + ntXOR

Data-in to correctable error flag (read cycle) =

TDVSV + TPVSV + TSVCV + ntXOR

Write data to check-bits valid (full write cycle) =

TQVQV + TPVSV + ntXOR

Data-in to check-bits valid (read-mod-write cycle) =

TDVSV + TPVSV + TSVQV + TQVQV + TPVSV + 2ntXOR

Data-in to check-bits valid (non-correcting readmodify-write cycle) =

TDVQU + TQVQV + TPVSV + ntXOR

### HAMMING CODE

The 8206 uses a modified Hamming code which was optimized for multi-chip EDCU systems. The code is

such that partial parity is computed by all 8206's in parallel. No 8206 requires more time for propagation through logic levels than any other one, and hence no one device becomes a bottleneck in the parity operation. However, one or two levels of external TTL XOR gates are required in systems with three to five chips. The code appears in Table 5. The check bits are derived from the table by XORing or XNORing together the bits indicated by 'X's in each row corresponding to a check bit. For example, check bit 0 in the MASTER for data word 10001101110111 will be "0". It should be noted that the 8206 will detect the gross-error condition of all lows or all highs.

Error correction is accomplished by identifying the bad bit and inverting it. Table 5 can also be used as an error syndrome table by replacing the 'X's with '1's. Each column then represents a different syndrome word, and by locating the column corresponding to a particular syndrome the bit to be corrected may be identified. If the syndrome cannot be located then the error cannot be corrected. For example, if the syndrome word is 00110111, the bit to be corrected is bit 5 in the slave one data word (bit 21).

The syndrome decoding is also summarized in Tables 6 and 7 which can be used for error logging. By finding the appropriate syndrome word (starting with bit zero, the least significant bit), the result is either: 1) no error; 2) an identified (correctable) single bit error; 3) a double bit error; or 4) a multi-bit uncorrectable error.

Table 5. Modified Hamming Code Check Bit Generation

8

Check bits are generated by XOR'ing (except for the CB0 and CB1 data bits, which are XNOR'ed in the Master) the data bits in the rows corresponding to the check bits. Note there are 6 check bits in a 16-bit system, 7 in a 32-bit system, and 8 in 48-or-more-bit systems.

| 0       1       2       3       4       5       6       7       0       1       2       3       4       5       6       7         -       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BYTE N | BYTE NUMBER |   |   |   | 0 |   |     |   |   |    |     |   | ÷ |         |   |   | OPERATION |   |   |   |   | N  |   |    |     |        |   |   | ო        |   |    |    | ODERATION |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|---|---|---|---|---|-----|---|---|----|-----|---|---|---------|---|---|-----------|---|---|---|---|----|---|----|-----|--------|---|---|----------|---|----|----|-----------|

| x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x       x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BIT NL |             |   | - | 2 | e | 4 |     | 9 | ~ |    | -   |   |   |         |   | - |           | 0 | - | 2 | e | 4  | ß | 9  | 2   | 0      | - | N | ,<br>,   | 4 |    | 2  |           |

| X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | CB0 =       | × |   |   | × |   | ×   | × |   | ×  |     |   | ' | ×       |   | ' | XNOR      | ' | × | × | × | 1  | × | ×  | 1   | <br>-  | × | × |          | Î | ļ  |    | XOR       |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | CB1 =       | × | , | × |   |   | ×   |   | × | -  | ×   | Â | Ĵ |         | × | ' | XNOR      | × | × | × | ' | '  | × | ·  | ×   | ×      | × |   |          | ÷ | ÷  | ×  | XOR       |

| X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | CB2 =       | • | × | × |   | × |     | × |   |    |     | × | , | י<br>ער | • | × | XOR       | 1 | × | × | × | •  | × | ×  | ×   | ,      |   | × | ×        |   |    |    | XOR       |

| CB4 =       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       ·       · <th>CHECK</th> <td>CB3 =</td> <td>×</td> <td>×</td> <td>×</td> <td>×</td> <td>×</td> <td></td> <td></td> <td>1</td> <td>×</td> <td>×</td> <td>×</td> <td></td> <td>'</td> <td>'</td> <td>'</td> <td>XOR</td> <td>×</td> <td>×</td> <td>•</td> <td>•</td> <td>×</td> <td></td> <td>×</td> <td>×</td> <td>×</td> <td></td> <td>-</td> <td>Ŷ</td> <td>×</td> <td></td> <td></td> <td>XOR</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CHECK  | CB3 =       | × | × | × | × | × |     |   | 1 | ×  | ×   | × |   | '       | ' | ' | XOR       | × | × | • | • | ×  |   | ×  | ×   | ×      |   | - | Ŷ        | × |    |    | XOR       |

| 1       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BITS   |             | • | ŀ |   | × | × | ×   | × | × |    |     |   |   | ×       | × | × | XOR       | × | × | • | • | ×  | × | ×  | ×   | ,      |   |   | <u>,</u> | × | ĵ. | Ċ  | XOR       |

| =       -       -       -       -       -       -       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×       ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | CB5 =       | · | ŀ |   |   |   |     |   | 1 | ×  | ×   | × | Ç | ×       | × | × | XOR       | 1 | ' | ' | × | ×  | × | ×  | ×   |        |   |   |          | Ŷ | Ç  | ×  | XOR       |

| =       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | CB6 =       | · | · |   |   |   |     |   |   |    |     |   |   | '       | ' | ' | XOR       | ' | ' | ' | • | •  |   | ı  | •   | ×      | × | × | ×        | Ŷ | Ç  | ×  | XOR       |

| 0       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        | CB7 =       | ı | · | ī | ī | ī |     |   | ı |    |     |   |   | '       | ' | ' | XOR       | ı | ' | 1 | ľ | ı. | ī | ,  | ī   | т      |   |   |          |   | ;  |    | XOR       |

| 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 1 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 1 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | DATA   | A RITS      | 0 | 0 | 0 | 0 | 0 |     | 0 | 0 |    | 0   | - | - | -       | - | - |           | - | - | - | - | N  | N | N  | N   | 2      | N | 2 | 2        | 2 | 0  | 33 |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |             | 0 | - | N | e |   |     | 9 | ~ |    | -   | 0 | - | ຕ<br>ເ  | 4 | 2 |           | 9 | ~ | 8 | റ | 0  | - | N  | ო   |        | - | 9 | ~        | 8 | 6  | -  |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |             |   |   |   |   | ÷ | 6 B | Ĕ | Я | MA | STI | Ë |   |         |   |   |           |   |   |   |   |    |   | SL | AVI | Щ<br>Ш | - |   |          |   |    |    |           |

| <b>0</b> 4 ×× × × × 4 4 | BYTE NUMBER         A         A           BIT NUMBER         0         1         2         3         4         5         6         7         0         1         2         3           BIT NUMBER         0         1         2         3         4         5         6         7         0         1         2         3           CB0         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         ×         × <t< th=""></t<> |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

8

Table 6. 8206 Syndrome Decoding

|   |     |     |    |   |     |     |     |    | 02003 | ,  |    |    | <u> </u> |    |    |    |    |    |    |    |

|---|-----|-----|----|---|-----|-----|-----|----|-------|----|----|----|----------|----|----|----|----|----|----|----|

|   |     |     |    | 0 | 0   | 1   | 0   | 1  | 0     | 1  | 0  | 1  | 0        | 1  | 0  | 1  | 0  | 1  | 0  | 1  |

| S | ynd | rom | ie | 1 | 0   | 0   | 1   | 1  | 0     | 0  | 1  | 1  | 0        | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

|   |     | its |    | 2 | 0   | 0   | 0   | 0  | 1     | 1  | 1  | 1  | 0        | 0  | 0  | 0  | 1  | 1  | 1  | 1  |

| 7 | 6   | 5   | 4  | 3 | 0   | 0   | 0   | 0  | 0     | 0  | 0  | 0  | 1        | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| 0 | 0   | 0   | 0  |   | Ν   | CB0 | CB1 | D  | CB2   | D  | D  | 18 | CB3      | D  | D  | 0  | D  | 1  | 2  | D  |

| 0 | 0   | 0   | 1  |   | CB4 | D   | D   | 5  | D     | 6  | 7  | D  | D        | D  | 16 | D  | 4  | D  | D  | 17 |

| 0 | 0   | 1   | 0  |   | CB5 | D   | D   | 11 | D     | 19 | 12 | D  | D        | 8  | 9  | D  | 10 | D  | D  | 67 |

| 0 | 0   | 1   | 1  |   | D   | 13  | 14  | D  | 15    | D  | D  | 21 | 20       | D  | D  | 66 | D  | 22 | 23 | D  |

| 0 | 1   | 0   | 0  |   | CB6 | D   | D   | 25 | D     | 26 | 49 | D  | D        | 48 | 24 | D  | 27 | D  | D  | 50 |

| 0 | 1   | 0   | 1  |   | D   | 52  | 55  | D  | 51    | D  | D  | 70 | 28       | D  | D  | 65 | D  | 53 | 54 | D  |

| 0 | 1   | 1   | 0  |   | D   | 29  | 31  | D  | 64    | D  | D  | 69 | 68       | D  | D  | 32 | D  | 33 | 34 | D  |

| 0 | 1   | 1   | 1  |   | 30  | D   | D   | 37 | D     | 38 | 39 | D  | D        | 35 | 71 | D  | 36 | D  | D  | U  |

| 1 | 0   | 0   | 0  |   | CB7 | D   | D   | 43 | D     | 77 | 44 | D  | D        | 40 | 41 | D  | 42 | D  | D  | U  |

| 1 | 0   | 0   | 1  |   | D   | 45  | 46  | D  | 47    | D  | D  | 74 | 72       | D  | D  | U  | D  | 73 | U  | D  |

| 1 | 0   | 1   | 0  |   | D   | 59  | 75  | D  | 79    | D  | D  | 58 | 60       | D  | D  | 56 | D  | U  | 57 | D  |

| 1 | 0   | 1   | 1  |   | 63  | D   | D   | 62 | D     | U  | U  | D  | D        | U  | U  | D  | 61 | D  | D  | U  |

| 1 | 1   | 0   | 0  |   | D   | U   | U   | D  | U     | D  | D  | U  | 76       | D  | D  | U  | D  | U  | U  | D  |

| 1 | 1   | 0   | 1  |   | 78  | D   | D   | U  | D     | U  | U  | D  | D        | U  | U  | D  | U  | D  | D  | U  |

| 1 | 1   | 1   | 0  |   | U   | D   | D   | U  | D     | U  | U  | D  | D        | U  | U  | D  | U  | D  | D  | U  |

| 1 | 1   | 1   | 1  |   | D   | U   | U   | D  | U     | D  | D  | U  | U        | D  | D  | U  | D  | U  | U  | D  |

N = No Error

CBX = Error in Check Bit X

X = Error in Data Bit X

D = Double Bit Error

U = Uncorrectable Multi-Bit Error

### SYSTEM ENVIRONMENT

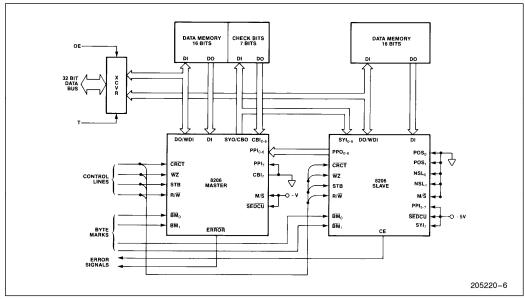

The 8206 interface to a typical 32 bit memory system is illustrated in Figure 5. For larger systems, the partial parity bits from slaves two to four must be XOR'ed externally, which calls for one level of XOR gating for three 8206's and two levels for four or five 8206's.

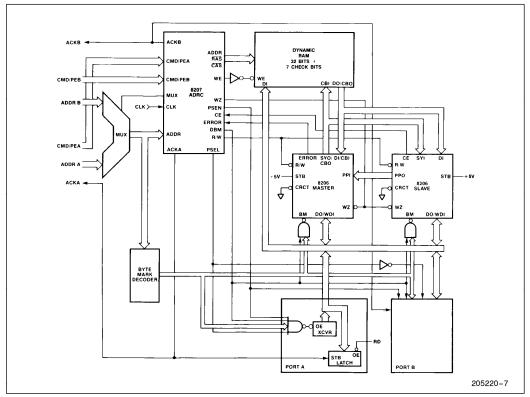

The 8206 is designed for direct connection to the Intel 8207 Dynamic RAM Controller. The 8207

has the ability to perform dual port memory control, and Figure 6 illustrates a highly integrated dual port RAM implementation using the 8206 and 8207. The 8206/8207 combination permits such features as automatic scrubbing (correcting errors in memory during refresh), extending RAS and CAS timings for Read-Modify-Writes in single memory cycles, and automatic memory initialization upon reset. Together these two chips provide a complete dual-port, errorcorrected dynamic RAM subsystem.

Figure 5. 32-Bit 8206 System Interface

Figure 6. Dual Port RAM Subsystem with 8206/8207 (32-bit bus)

## **MEMORY BOARD TESTING**

The 8206 lends itself to straightforward memory board testing with a minimum of hardware overhead. The following is a description of four common test modes and their implementation.

- Mode 0— Read and write with error correction. Implementation: This mode is the normal 8206 operating mode.

- Mode 1— Read and write data with error correction disabled to allow test of data memory. Implementation: This mode is performed with CRCT deactivated.

- Mode 2— Read and write check bits with error correction disabled to allow test of check bits memory.

Implementation: Any pattern may be written into the check bits memory by judiciously choosing the proper data word to generate the desired check bits, through the use of the 8206 Hamming code. To read out the check bits it is first necessary to fill the data memory with all zeros, which may be done by activating  $\overline{WZ}$  and incrementing memory addresses with  $\overline{WE}$ to the check bits memory held inactive, and then performing ordinary reads. The check bits will then appear directly at the SYO outputs, with bits CB0 and CB1 inverted.

Mode 3—Write data, without altering or writing check bits, to allow the storage of bit combinations to cause error correction and detection.

Implementation: This mode is implemented by writing the desired word to memory with  $\overline{\text{WE}}$  to the check bits array held inactive.

Figure 8b. 8206 Pin Grid Array (PGA) Package and Pinout Diagram

## **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias0°C to 70°C                   |

|-------------------------------------------------------------|

| Storage Temperature $\dots -65^{\circ}C$ to $+150^{\circ}C$ |

| Voltage On Any Pin with Respect to Ground                   |

| Power Dissipation                                           |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

| D.C. | <b>CHARACTERISTICS</b> | $T_{A}$ = 0°C to 70°C, $V_{CC}$ = 5.0V $\pm$ 10%, $V_{SS}$ = | GND |

|------|------------------------|--------------------------------------------------------------|-----|

|------|------------------------|--------------------------------------------------------------|-----|

| Symbol              | Parameter                                                                                                                  | Min        | Max                       | Units    | Test Conditions                                                 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------|------------|---------------------------|----------|-----------------------------------------------------------------|

| ICC                 | Power Supply Current<br>—Single 8206 or<br>Slave #1                                                                        |            | 270                       | mA       |                                                                 |

|                     | —Master in Multi-Chip<br>or Slaves #2, 3, 4                                                                                |            | 230                       | mA       |                                                                 |

| V <sub>IL</sub> (1) | Input Low Voltage                                                                                                          | -0.5       | 0.8                       | V        |                                                                 |

| V <sub>IH</sub> (1) | Input High Voltage                                                                                                         | 2.0        | V <sub>CC</sub> +<br>0.5V | V        |                                                                 |

| V <sub>OL</sub>     | Output Low Voltage<br>—DO<br>—All Others                                                                                   |            | 0.45<br>0.45              | V<br>V   | $I_{OL} = 8 \text{ mA}$<br>$I_{OL} = 2.0 \text{ mA}$            |

| V <sub>OH</sub>     | Output High Voltage<br>—DO, CBO<br>—All Other Outputs                                                                      | 2.6<br>2.4 |                           | V<br>V   | $I_{OH} = -2 \text{ mA}$<br>$I_{OH} = -0.4 \text{ mA}$          |

| I <sub>LO</sub>     | I/O Leakage Current<br>—PPI <sub>4</sub> /CE<br>—DO/WDI <sub>0-15</sub>                                                    |            | ±20<br>±10                | μΑ<br>μΑ | $0.45V \leq V_{I/O} \leq V_{CC}$                                |

| ILI                 | Input Leakage Current<br>—PPI <sub>0-3, 5-7,</sub> CBI <sub>6-7</sub> , <del>SEDCU</del> (2)<br>—All Other Input Only Pins |            | ±20<br>±10                | μΑ<br>μΑ | $\text{ov} \leq \text{v}_{\text{IN}} \leq \text{v}_{\text{CC}}$ |

### NOTES:

1. SEDCU (pin 3) and M/S (pin 4) are device strapping options and should be tied to  $V_{CC}$  or GND.  $V_{IH}$  min =  $V_{CC}$  -0.5V and  $V_{IL}$  max = 0.5V.

2. PPI0-7 (pins 13-20) and CBI6-7 (pins 11, 12) have internal pull-up resistors and if left unconnected will be pulled to V<sub>CC</sub>.

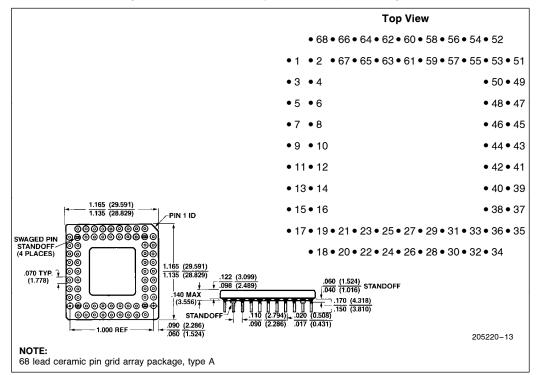

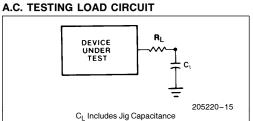

### A.C. TESTING INPUT, OUTPUT WAVEFORM

A.C. CHARACTERISTICS  $T_A$  = 0°C to 70°C,  $V_{CC}$  =  $\,+\,5V\,\pm\,$  10%,  $V_{SS}$  = 0V,  $R_L$  = 22 $\Omega,\,C_L$  = 50 pF; all times are in ns

| Symbol            | Parameter                                                    | 8206-1 |     | 8206 |     | Notes |  |

|-------------------|--------------------------------------------------------------|--------|-----|------|-----|-------|--|

| Symbol            | Falameter                                                    | Min    | Max | Min  | Max | Notes |  |

| T <sub>RHEV</sub> | ERROR Valid from R/₩↑                                        |        | 20  |      | 25  |       |  |

| T <sub>RHCV</sub> | CE Valid from $R/W \uparrow$ (Single 8206)                   |        | 34  |      | 44  |       |  |

| T <sub>RHQV</sub> | Corrected Data Valid from $R\overline{W}$ $\uparrow$         |        | 44  |      | 54  | 1     |  |

| T <sub>RVSV</sub> | SYO/CBO/PPO Valid from R/W                                   |        | 32  |      | 42  | 1     |  |

| T <sub>DVEV</sub> | ERROR Valid from Data/Check Bits In                          |        | 35  |      | 42  |       |  |

| T <sub>DVCV</sub> | CE Valid from Data/Check Bits In                             |        | 50  |      | 70  |       |  |

| T <sub>DVQV</sub> | Corrected Data Valid from Data/Check Bits In                 |        | 55  |      | 67  |       |  |

| T <sub>DVSV</sub> | SYO/PPO Valid from Data/Check Bits In                        |        | 40  |      | 55  |       |  |

| T <sub>BHQV</sub> | Corrected Data Access Time                                   |        | 35  |      | 37  |       |  |

| T <sub>BXQX</sub> | Hold Time from Data/Check Bits In                            | 0      |     | 0    |     | 1     |  |

| T <sub>BLQZ</sub> | Corrected Data Float Delay                                   | 0      | 25  | 0    | 28  | 1     |  |

| T <sub>SHIV</sub> | STB High to Data/Check Bits In Valid                         | 30     |     | 30   |     | 2     |  |

| T <sub>IVSL</sub> | Data/Check Bits In to STB↓ Set-Up                            | 5      |     | 5    |     |       |  |

| T <sub>SLIX</sub> | Data/Check Bits In from STB $\downarrow$ Hold                | 15     |     | 25   |     |       |  |

| T <sub>PVEV</sub> | ERROR Valid from Partial Parity In                           |        | 21  |      | 30  | 3     |  |

| T <sub>PVQV</sub> | Corrected Data (Master) from Partial Parity In               |        | 46  |      | 61  | 1, 3  |  |

| T <sub>PVSV</sub> | Syndrome/Check Bits Out from Partial Parity In               |        | 32  |      | 43  | 1, 3  |  |

| T <sub>SVQV</sub> | Corrected Data (Slave) Valid from Syndrome                   |        | 41  |      | 51  | 3     |  |

| T <sub>SVCV</sub> | CE Valid from Syndrome (Slave Number 1)                      |        | 43  |      | 48  | 3     |  |

| TQVQV             | Check Bits/Partial Parity Out from Write Data In             |        | 44  |      | 64  | 1     |  |

| T <sub>RHSX</sub> | Check Bits/Partial Parity Out from R/W, $\overline{WZ}$ Hold | 0      |     | 0    |     | 1     |  |

| T <sub>RLSX</sub> | Syndrome Out from $R/\overline{W}$ Hold                      | 0      |     | 0    |     |       |  |

| T <sub>QXQX</sub> | Hold Time from Write Data In                                 | 0      |     | 0    |     | 1     |  |

| T <sub>SVRL</sub> | Syndrome Out to $R/\overline{W} \downarrow$ Set-Up           | 5      |     | 17   |     | 3     |  |

| T <sub>DVRL</sub> | Data/Check Bits to $R/\overline{W}$ Set-Up                   | 24     |     | 39   |     | 1     |  |

| T <sub>DVQU</sub> | Uncorrected Data Out from Data In                            |        | 29  |      | 32  |       |  |

| T <sub>TVQV</sub> | Corrected Data Out from $\overline{CRCT}\downarrow$          |        | 25  |      | 30  |       |  |

| T <sub>WLQL</sub> | WZ ↓ to Zero Out                                             |        | 25  |      | 30  |       |  |

| T <sub>WHQX</sub> | Zero Out from WZ↑ Hold                                       | 0      |     | 0    |     | 0     |  |

### NOTES:

NOTES:

1. A.C. Test Levels for CBO and DO are 2.4V and 0.8V.