# **iSBC 215™ WINCHESTER DISK CONTROLLER** HARDWARE REFERENCE MANUAL

Order Number: 121593-002

SBC-215B-1 uses 144580-001 in U87 and 144581-001 in U88

> iSBC-215B-1 is special version for MDX-750 Winchester Peripheral for MDS Series-II/III. Also,

SYP86384AA, 144856.U87, 144587.U88

| REVISION HISTORY                      | PRINT<br>DATE  |

|---------------------------------------|----------------|

| Original Issue                        | 1/81           |

| Manual updated for minor corrections. | 9/81           |

|                                       |                |

|                                       |                |

|                                       |                |

|                                       |                |

|                                       |                |

|                                       |                |

|                                       | Original Issue |

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BXP    | Intelevision    | Micromap      |

|--------|-----------------|---------------|

| CREDIT | Intellec        | Multibus      |

| i      | iRMX            | Multimodule   |

| ICE    | iSBC            | Plug A-Bubble |

| iCS    | iSBX            | PROMPT        |

| im     | Library Manager | Promware      |

| INSITE | MCS             | RMX/80        |

| Intel  | Megachassis     | System 2000   |

| Intel  | Micromainframe  | ŬРІ           |

| 50     |                 | (Scope        |

and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or RMX and a numerical suffix.

# **PREFACE**

This manual provides information regarding the installation, programming, operation, and servicing of the iSBC 215™ Winchester Disk Controller.

## Related documents include:

- The 8086 Family User's Manual, Order No. 9800722

- Intel MULTIBUS™ Specifications, Order No. 9800683

- Intel 8080/8085 Assembly Language Reference Manual, Order No. 9800301

- MCS-86™ MACRO Assembly Language Reference Manual, Order No. 900640

- MCS-86/85™ Family User's Manual, Order No. 121506

- 8089 Assembler User's Guide, Order No. 9800938

- *iSBX*<sup>TM</sup> Bus Specification, Order No. 142686

- iSBX 218<sup>™</sup> Flexible Disk Controller Hardware Reference Manual, Order No. 121583

# **CONTENTS**

| CHAPTER 1                                  |                               | -                                                                       |

|--------------------------------------------|-------------------------------|-------------------------------------------------------------------------|

| GENERAL INFORMATION                        | Page                          | Page                                                                    |

| Introduction                               | 1-1                           | Execute iSBX I/O Program 3-16                                           |

| Description                                | 1-2                           | I/O Transfer Through iSBX Bus 3-16                                      |

| Specifications                             | 1-3                           | Buffer I/O 3-17                                                         |

|                                            |                               | Diagnostic 3-18                                                         |

| CHAPTER 2                                  |                               | Posting Status 3-18                                                     |

| PREPARATION FOR USE                        |                               | Transfer Error Status 3-19                                              |

| Introduction                               | 2-1                           | Interrupts 3-20                                                         |

| Unpacking and Inspection                   | 2-1                           | Controlling Data Transfer                                               |

| Board Installation Considerations          | 2-1                           | Through the iSBX Bus 3-20                                               |

| Power Requirement                          | 2-2                           | I/O Transfers Using iSBC 215                                            |

| Cooling Requirement                        |                               | Controller Resident Firmware 3-20                                       |

| Multibus Connector                         |                               | Data Transfer Using User Written                                        |

| Switch/Jumper Configurations               |                               | I/O Transfer Programs 3-20                                              |

| Wake-Up Address Selection                  |                               | Example Controller I/O Program 3-23                                     |

| Wake-Up I/O Port Address Selection         |                               | Enample Convious 17 C 1 regram (VIIII) C 10                             |

| System Data Bus Selection                  |                               | CHAPTER 4                                                               |

| Interrupt Priority Level                   |                               | PRINCIPLES OF OPERATION                                                 |

| Any Request Selection                      |                               | Introduction 4-1                                                        |

| Common Bus Request                         |                               | Schematic Interpretation 4-1                                            |

| Winchester Drive Interface                 |                               | Functional Overview 4-2                                                 |

| -5-Volt Selection                          |                               | Detailed Functional Description                                         |

| (8" Shugart/Quantum Drives Only)           | 2.8                           | Controller to Host Communications 4-6                                   |

| Cabling Requirements                       |                               | Multibus Interface                                                      |

| Drive Installation                         |                               | 8089 I/O Processor (IOP)                                                |

| iSBX Multimodule Interface                 |                               | Clock Circuit                                                           |

| iSBX 218 Board Installation                |                               | Bus Arbiter 4-7                                                         |

| Power Up/Down Considerations               |                               | Bus Controller Logic 4-8                                                |

| Diagnostic Check                           |                               | Multibus Interface                                                      |

| Diagnostic Oneck                           |                               | Data Transfer Logic 4-8                                                 |

| CHAPTER 3                                  |                               | Controller Initialization 4-8                                           |

| PROGRAMMING INFORMATIO                     | N                             | Wake-Up Address Comparator 4-9                                          |

| Introduction                               |                               | Controller Reset and Clear                                              |

| Programming Options                        |                               | Establishing A Link With                                                |

| Disk Organization                          |                               | I/O Communications Blocks 4-10                                          |

| Track Sectoring Format                     |                               | Interrupt Priority Logic                                                |

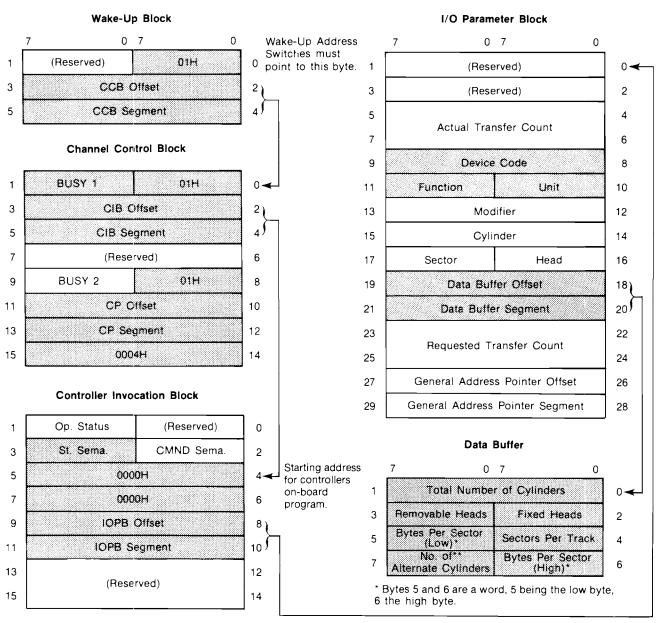

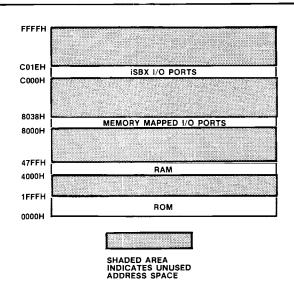

| Controller I/O Communications Blocks       |                               | Local Memory Map 4-11                                                   |

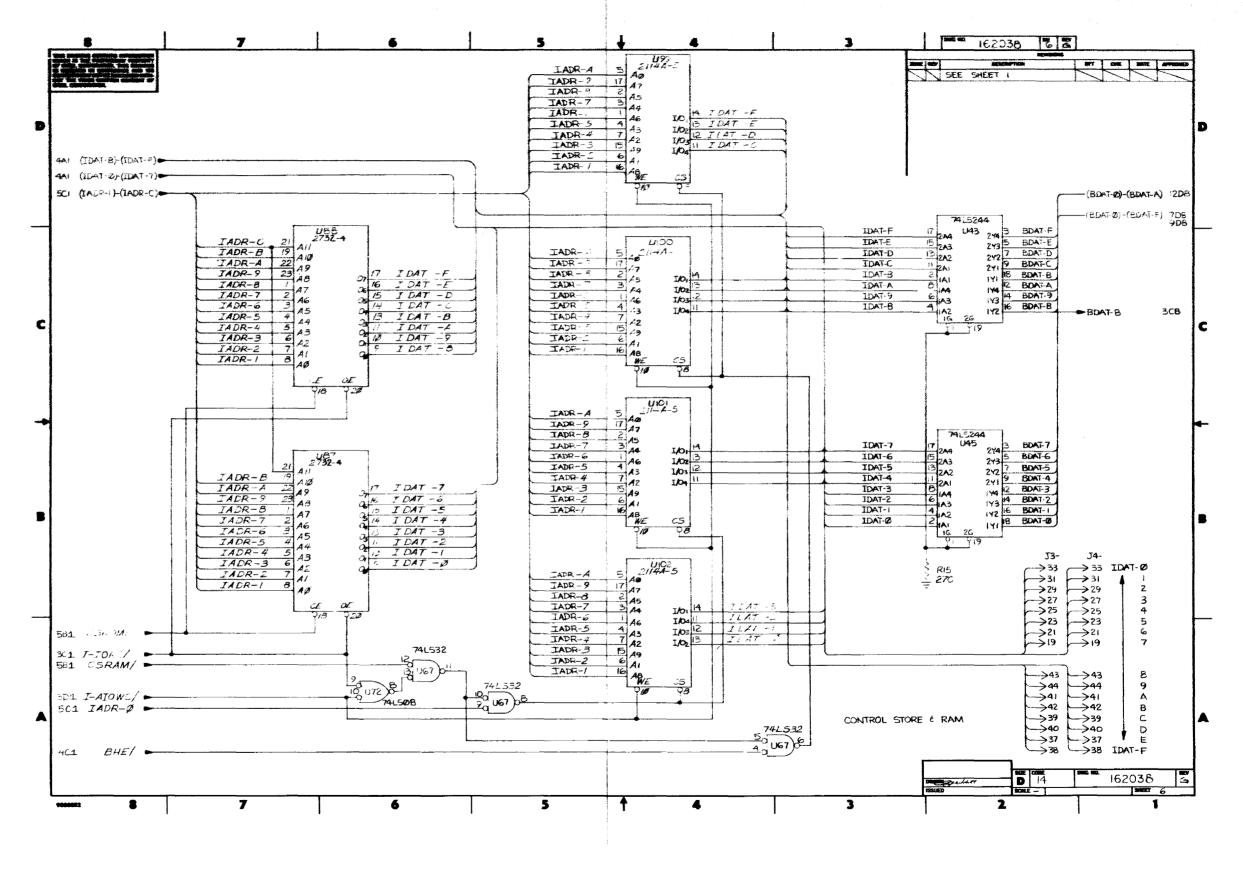

| Host CPU-Controller-Disk Drive Interaction |                               | ROM 4-11                                                                |

| Wake-Up I/O Port                           |                               | RAM 4-11                                                                |

| Wake-Up Block                              |                               | Local Memory Mapped I/O Ports                                           |

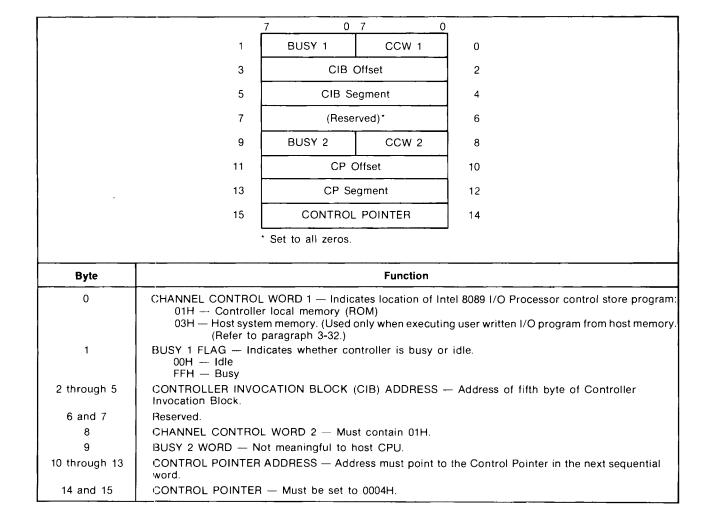

| Channel Control Block                      |                               | and iSBX I/O Ports 4-11                                                 |

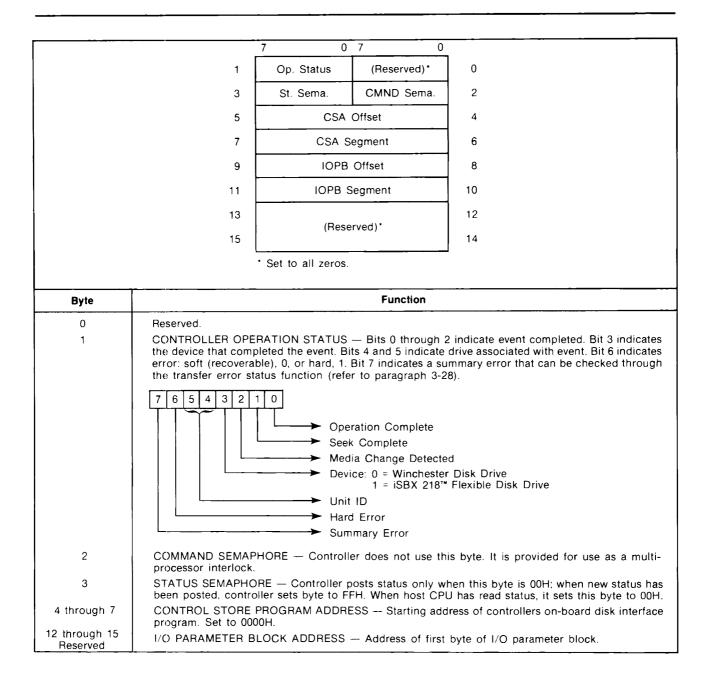

| Controller Invocation Block                |                               | Controller to Disk Drive Communications 4-12                            |

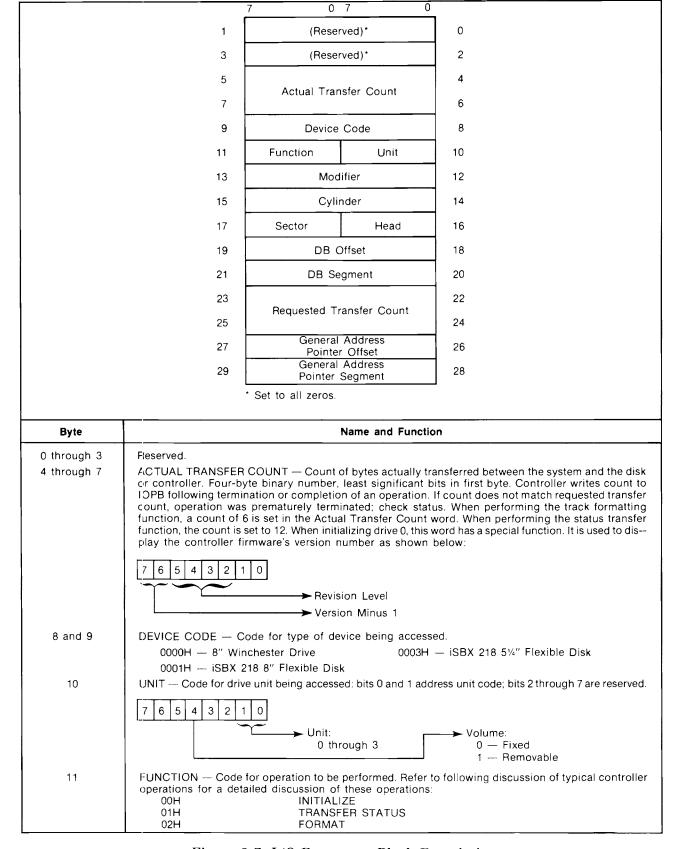

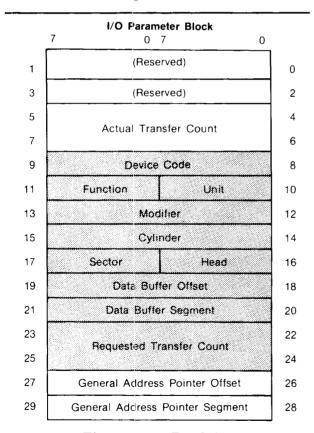

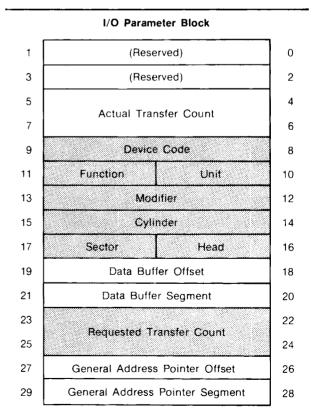

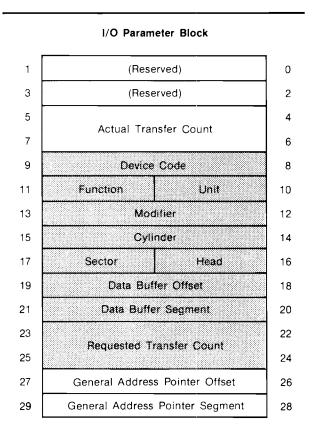

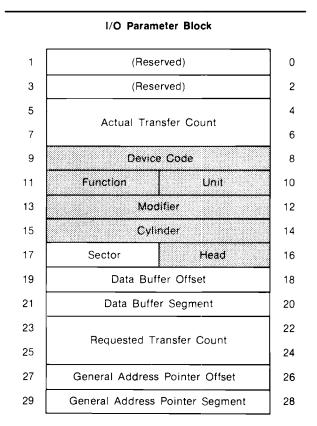

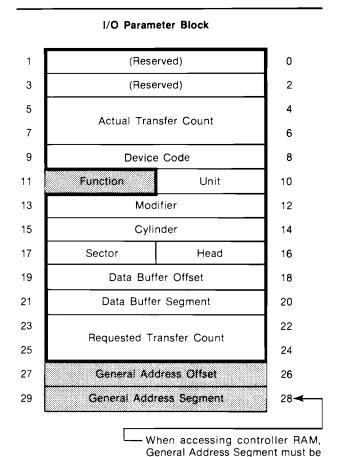

| I/O Parameter Block                        |                               | Controller to Winchester                                                |

| Typical Controller Operations              |                               | Disk Drive Interface 4-12                                               |

| Initializing the Controller                |                               | Control Cable Signals 4-13                                              |

|                                            |                               | Read/Write Cable Signals                                                |

| Track Formatting                           |                               | Controller to iSBX Connector Interface 4-14                             |

| Data Transfer and Verification             |                               | Controller to Disk Drive Interface Timing 4-15                          |

| Read Sector ID                             |                               | DMA Mode                                                                |

| Read Data                                  | · · · · · · · · · · · · · · · |                                                                         |

| Read Data Into Controller Buffer and V     |                               | Disk Formatting         4-16           Write Data Transfer         4-18 |

| Write Data                                 |                               | Read Data Transfers                                                     |

| Write Data from Controller Buffer to Di    |                               | SER/DES Logic 4-20                                                      |

| Initiate Track Seek                        |                               | Sync Byte Comparator Logic                                              |

| IIIIIIaic Hack Deek                        | 9-19                          | bytic byte Comparator Logic 4-21                                        |

# **CONTENTS (Continued)**

| Page                                                                                                         | Page                                                                                    |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

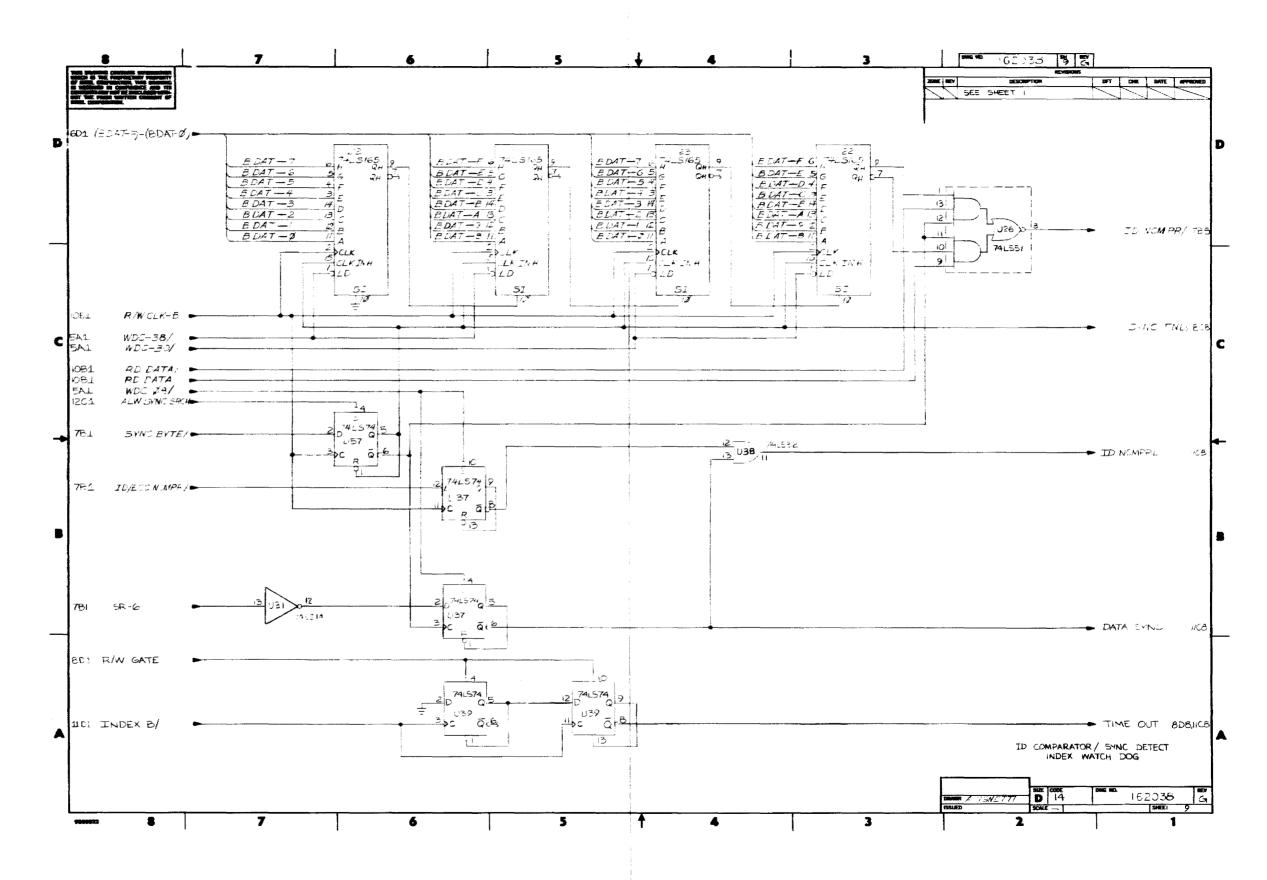

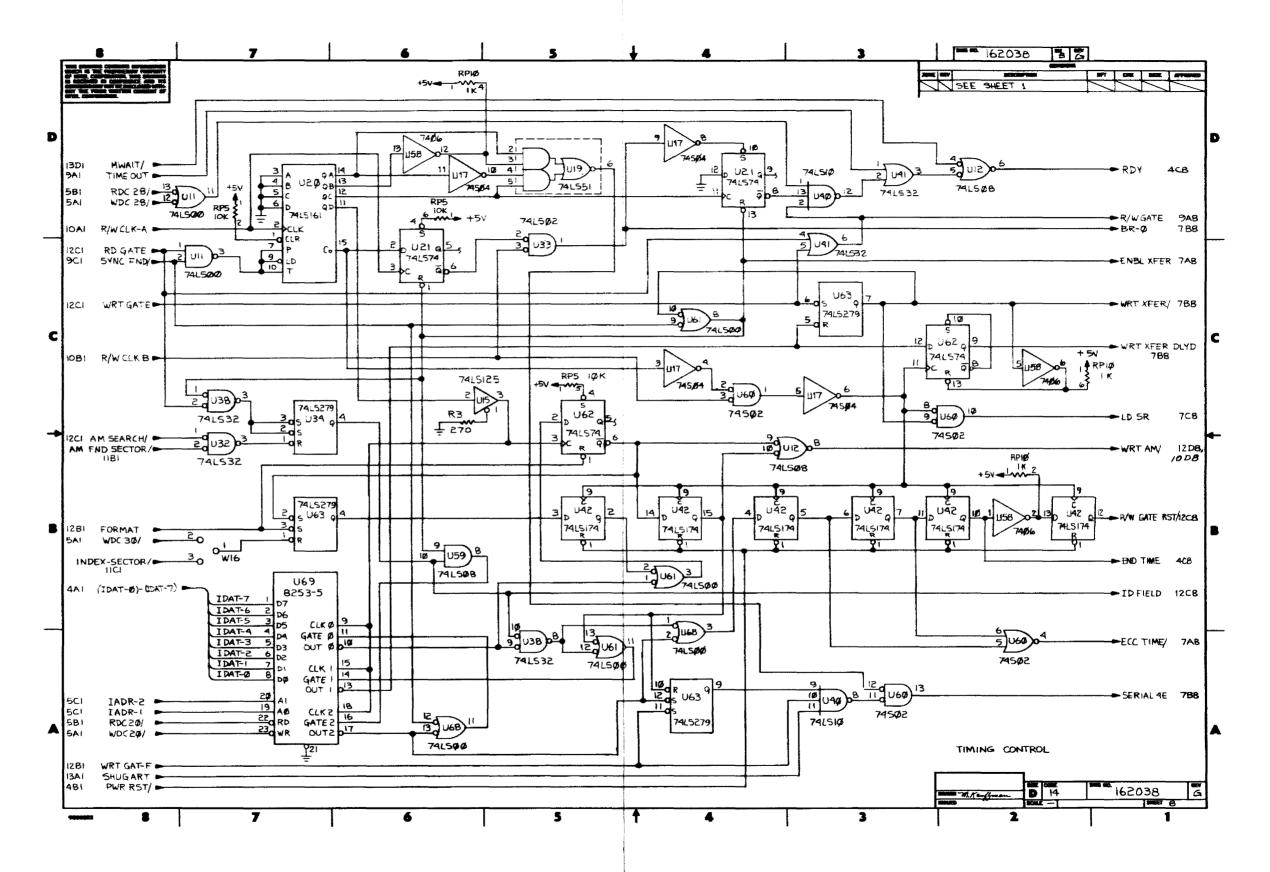

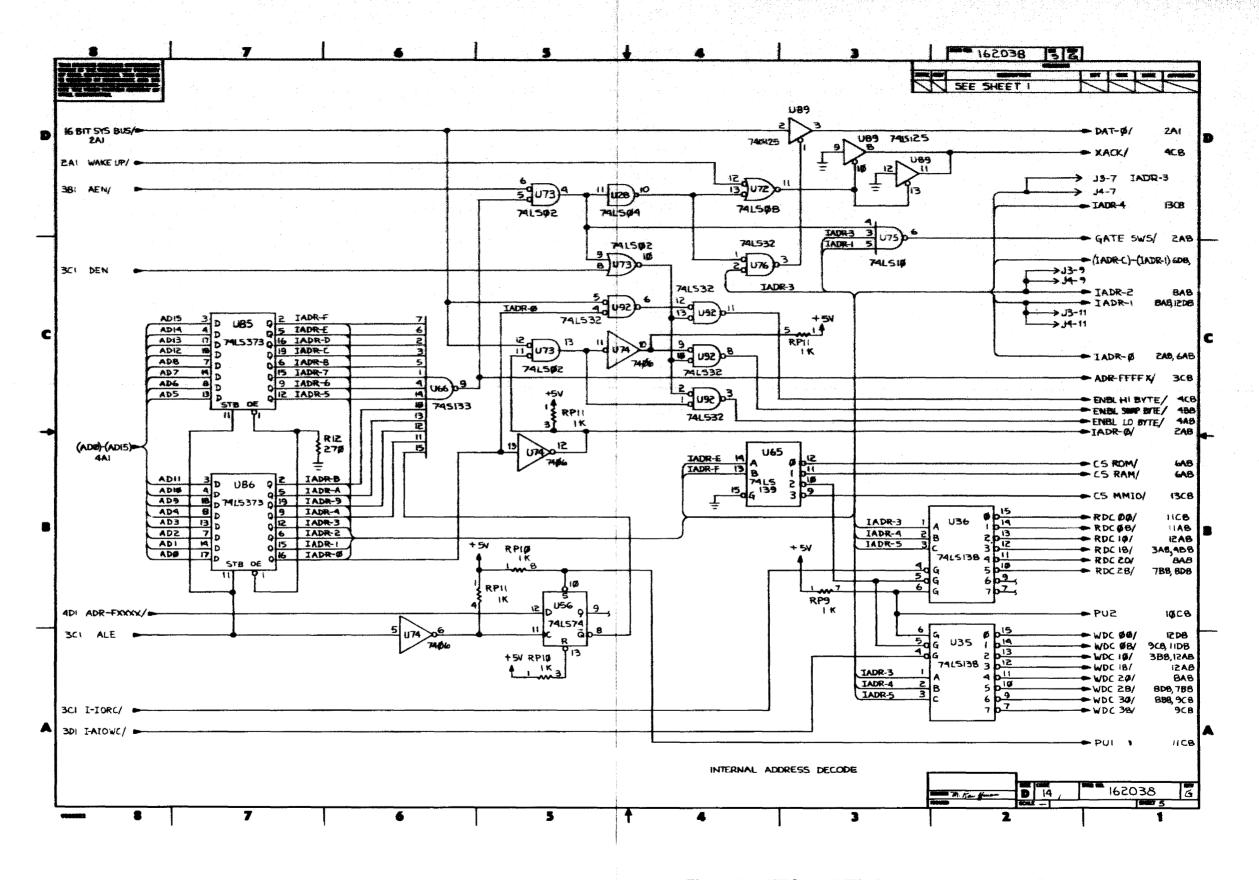

| 32-Bit ID Comparator Logic4-21ECC Generator Logic4-21Status Register Logic4-21Line Drivers and Receivers4-22 | Service and Repair Assistance5-1Self Diagnostic5-1Replaceable Components5-1             |

| CHAPTER 5 SERVICE INFORMATION Introduction                                                                   | APPENDIX A<br>HANDSHAKE SEQUENCES AND<br>EXAMPLE HOST PROCESSOR<br>DISK CONTROL PROGRAM |

# **TABLES**

| Table | Title                              | Page   | Table | Title                                | Page |

|-------|------------------------------------|--------|-------|--------------------------------------|------|

| 1-1.  | Board Specifications               |        | 3-4.  | iSBC 215 Controller RAM              |      |

| 1-2.  | Winchester Disk Drive              |        |       | Available for Program and            |      |

|       | Characteristics                    | 1-5    |       | Parameter Storage                    | 3-22 |

| 2-1.  | Multibus Connector P1              |        | 3-5.  | 8089 Handshake and Control Lines     |      |

|       | Pin Assignment                     | 2-2    |       | on the iSBX Bus                      | 3-22 |

| 2-2.  | iSBC 215 Controller/Multibus       |        | 3-6.  | Control and Status Lines             |      |

|       | Interface P1 Signal Descriptions   | 2-3    |       | on the iSBX Interface                | 3-23 |

| 2-3.  | iSBC 215 Controller/Multibus       |        | 3-7.  | Jumper Connections Allowing Optic    | on   |

|       | Interface Signal Characteristics   | 2-6    |       | Lines to be Driven                   | 3-23 |

| 2-4.  | Configuration Jumpers and Switches | 2-7    | 4-1.  | 8089 Status Line Decodes             | 4-8  |

| 2-5.  | Interrupt Priority Level Selection | 2-7    | 4-2.  | Host Wake-Up Commands                | 4-9  |

| 2-6.  | Winchester Drive                   |        | 4-3.  | Local I/O Ports                      | 4-12 |

|       | Manufacturer Selection             | 2-8    | 4-4.  | iSBX Bus I/O Port Addresses          | 4-12 |

| 2-7.  | -5-Volt Selection                  | 2-9    | 4-5.  | Control Cable Line Functions         | 4-13 |

| 2-8.  | J3 and J4 Pin Assignments          | . 2-22 | 4-6.  | Read/Write Cable Line Functions .    | 4-14 |

| 2-9.  | iSBX Bus Control Jumper Pins       | . 2-24 | 4-7.  | iSBX Bus Mnemonics-to-Controller     |      |

| 3-1.  | Error Status Buffer                | . 3-20 |       | Line Name                            | 4-15 |

| 3-2.  | Bit Functions in Hard and          |        | 4-8.  | Status Register Bits                 | 4-22 |

|       | Soft Error Bytes                   | . 3-21 | 5-1.  | Code for Manufacturers               |      |

| 3-3.  | iSBX Bus I/O Port Addresses        | . 3-22 | 5-2.  | Controller Board Electrical Parts Li |      |

# **ILLUSTRATIONS**

| Figure | e Title                               | Page   | Figur | e Title                          | Page        |

|--------|---------------------------------------|--------|-------|----------------------------------|-------------|

| 1-1.   | Typical Multiple Drive System         |        | 3-12. | Read Data                        |             |

|        | Using Winchester Disk Drives          | 1-1    | 3-13. | Read Data into Controller Buffer |             |

| 1-2.   | Typical Multiple Drive System         |        |       | and Verify                       | 3-14        |

|        | Using Flexible Disk Drives and        |        | 3-14. | Write Data                       | 3-15        |

|        | iSBX 218 Flexible Disk Controller     | 1-2    | 3-15. | Write Data from Controller Buffe | r           |

| 1-3.   | Automatic Error Checking              |        |       | to Disk                          | 3-15        |

|        | and Correction,                       | 1-3    | 3-16. | Initiate Track Seek              | 3-16        |

| 2-1.   | Serial Priority Resolution            |        | 3-17. | Execute iSBX Interface I/O Prog  | ram . 3-16  |

| 2-2.   | Master Command Access Timing          | 2-4    | 3-18. | I/O Transfers Through iSBX Into  | erface 3-17 |

| 2-3.   | 8" Shugart/Quantum Drive Interconne   | cting  | 3-19. | Buffer I/O                       | 3-18        |

|        | Cable Requirements                    |        | 3-20. | Diagnostic                       | 3-19        |

| 2-4.   | Fujitsu 2300/Memorex/14" Shugart Dr   |        | 3-21. | Transfer Error Status            | 3-19        |

|        | Interconnecting Cable Requirements    | 2-12   | 3-22. | Execution of iSBX Bus            |             |

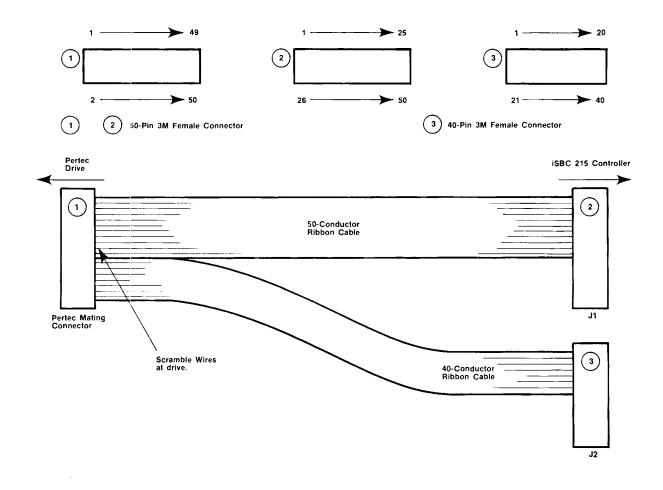

| 2-5.   | Pertec Drive Interconnecting          |        |       | I/O Program from RAM             | 3-23        |

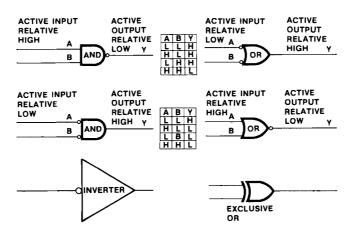

|        | Cable Requirements                    | . 2-14 | 4-1.  | Logic Conventions                | 4-1         |

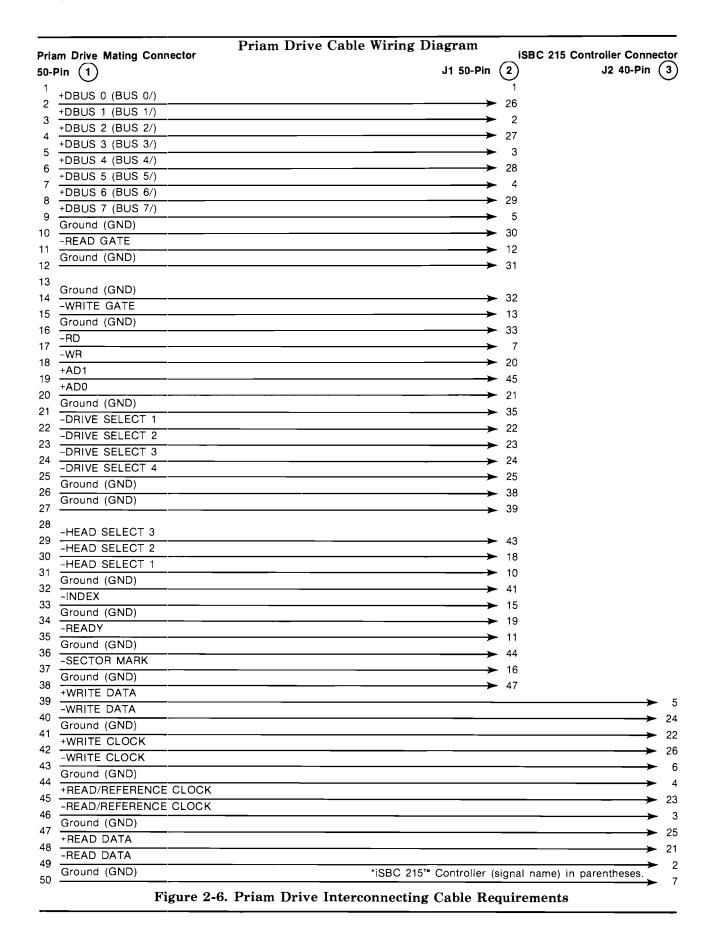

| 2-6.   | Priam Drive Interconnecting           |        | 4-2.  | Simplified Block Diagram         |             |

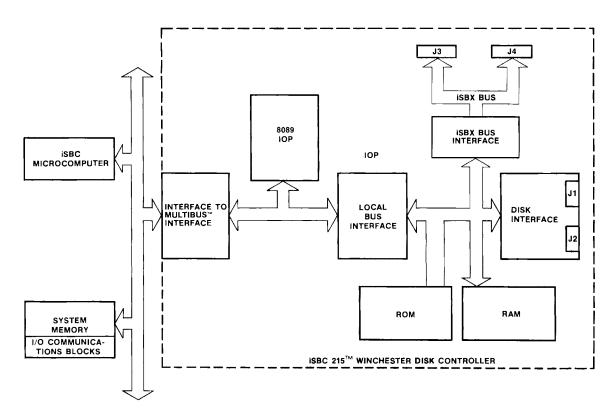

|        | Cable Requirements                    | . 2-16 |       | of iSBC 215 Controller           | 4-2         |

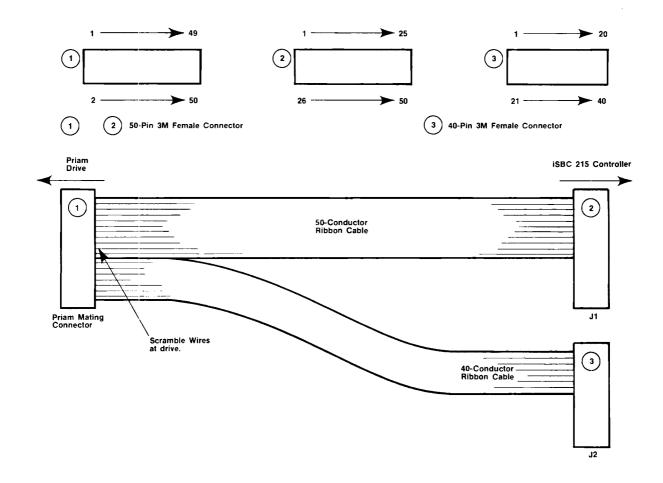

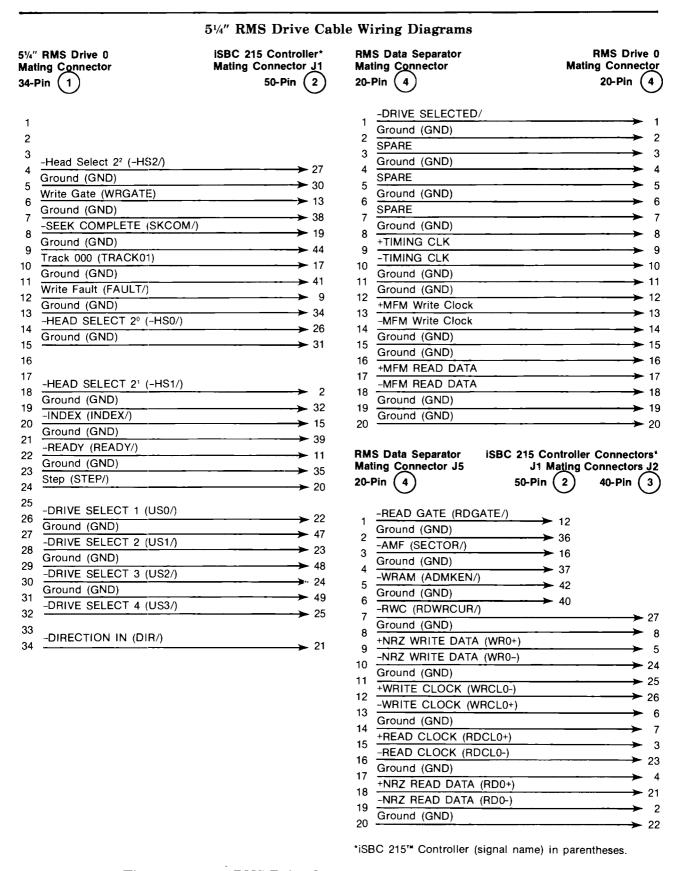

| 2-7.   | 5¼" RMS Drive Interconnecting         |        | 4-3.  | iSBC 215 Controller Functional   |             |

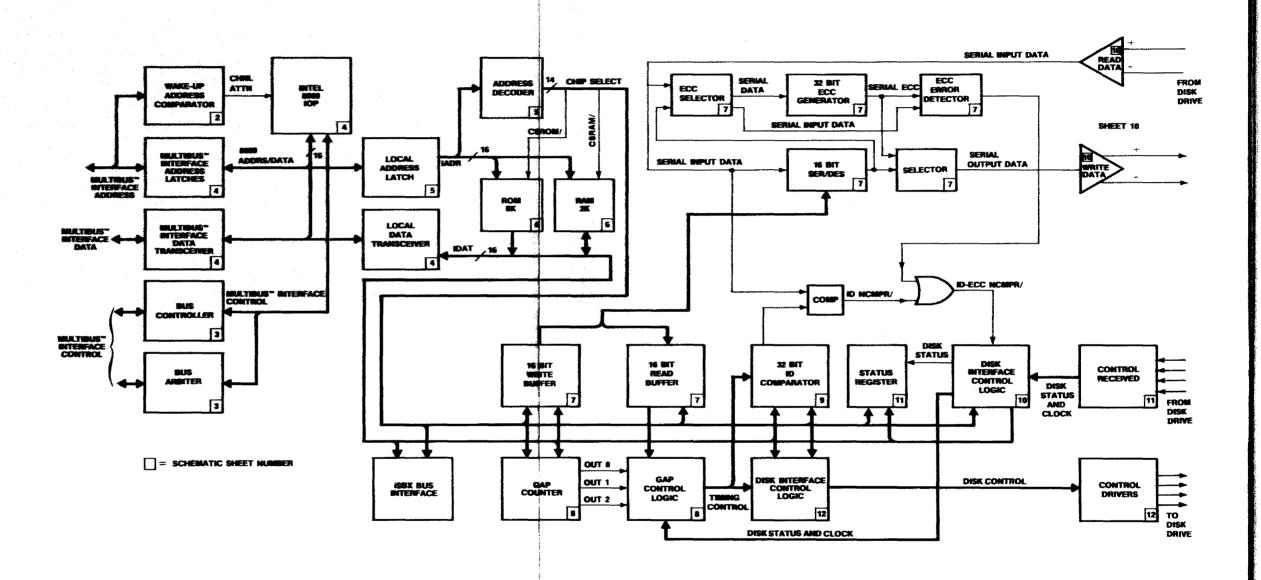

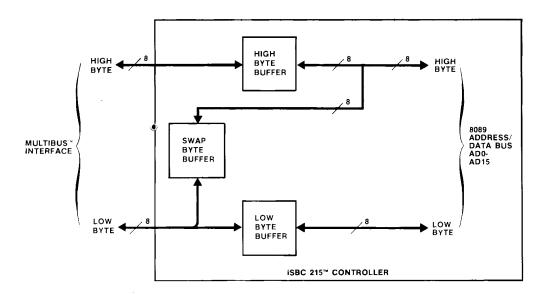

|        | Cable Requirements                    | . 2-18 |       | Block Diagram                    | 4-3         |

| 2-8.   | Control Data Corporation Drive Inter- |        | 4-4.  | Bus Arbitor and Bus Controller I | Logic 4-7   |

|        | connecting Cable Requirements         | . 2-19 | 4-5.  | Data Transmission Between Mult   | tibus       |

| 2-9.   | Control Data Corporation Drive Inter- |        |       | Interface and Controller Data    |             |

|        | connecting Cable Requirements         | . 2-20 |       | Transceivers                     | 4-9         |

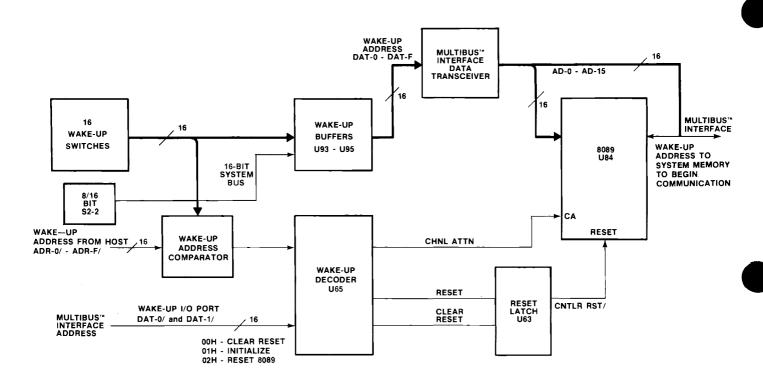

| 2-10.  | Controller to Drive Interfacing       | . 2-21 | 4-6.  | Wake-Up Address Logic            | 4-10        |

| 2-11.  | Installing the iSBX 218 Board on      |        | 4-7.  | Address Fetches in               |             |

|        | the iSBC 215 Controller Board         | . 2-23 |       | Initialization Sequence          | 4-11        |

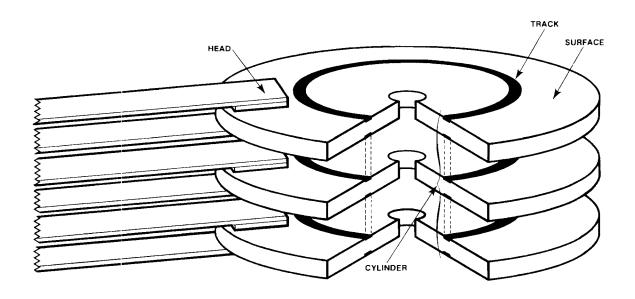

| 3-1.   | Disk Drive Organization and           |        | 4-8.  | Local Memory Map                 | 4-11        |

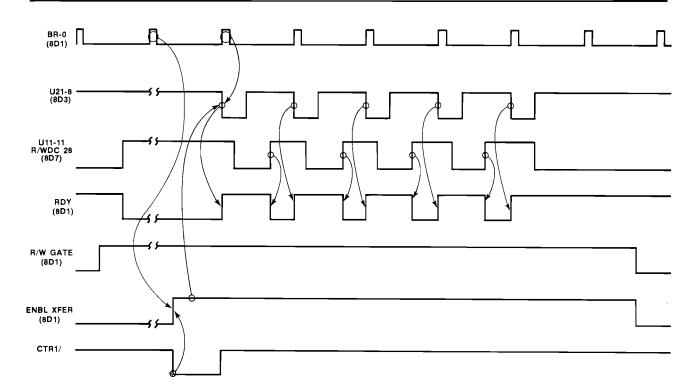

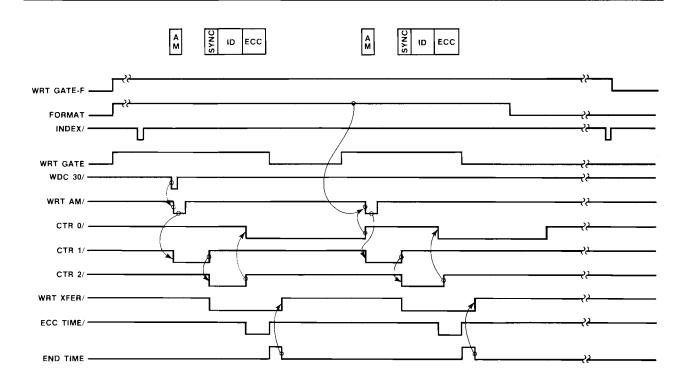

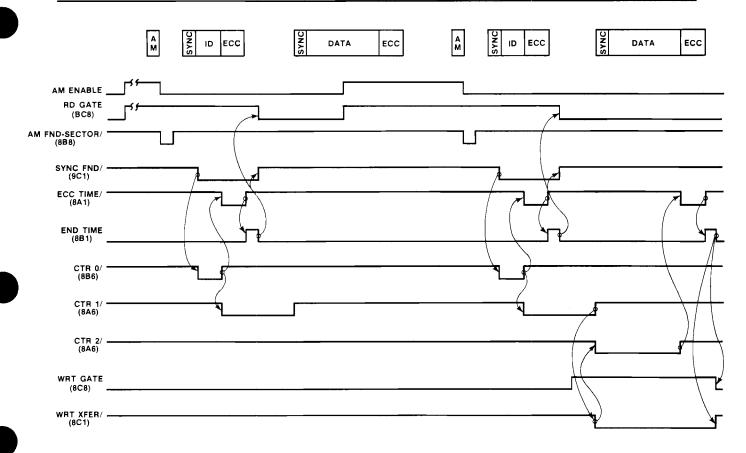

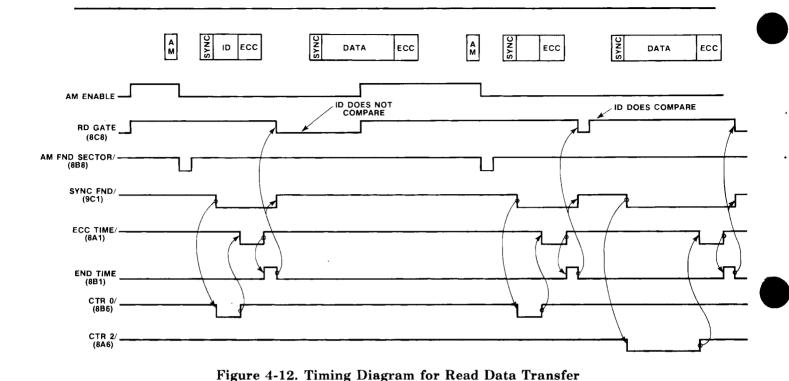

|        | Terminology                           | 3-1    | 4-9.  | Timing Diagram for RDY Signal    | 4-16        |

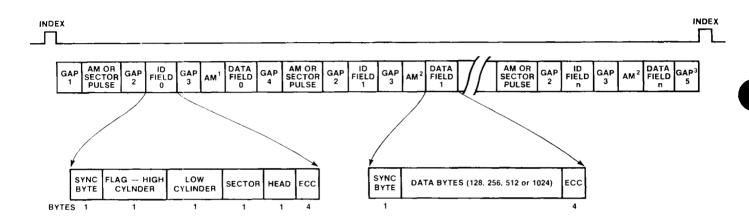

| 3-2.   | Sector Data Format                    | 3-2    | 4-10. | Timing Diagram for Disk          |             |

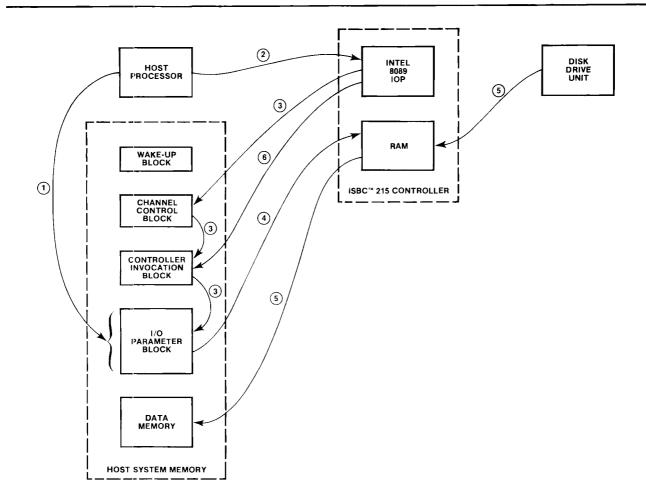

| 3-3.   | Host CPU-Disk Controller-             |        |       | Formatting Sequence              | 4-17        |

|        | Interaction Through the               |        | 4-11. | Timing Diagram for Write Data    |             |

|        | I/O Communications Block              | 3-3    | 4-12. | Timing Diagram for               |             |

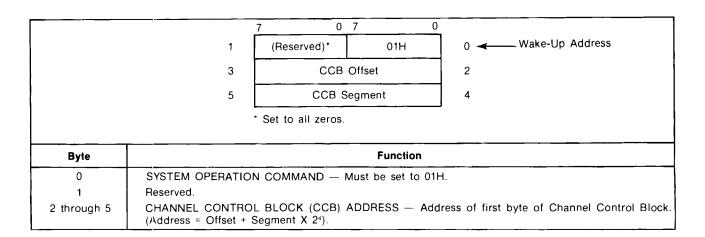

| 3-4.   | Wake-Up Block                         | 3-5    |       | Read Data Transfer               | 4-20        |

| 3-5.   | Channel Control Block                 | 3-5    | 5-1.  | iSBC 215 Controller Jumpers      |             |

| 3-6.   | Controller Invocation Block           | 3-6    |       | and Switch Locations             | 5-5         |

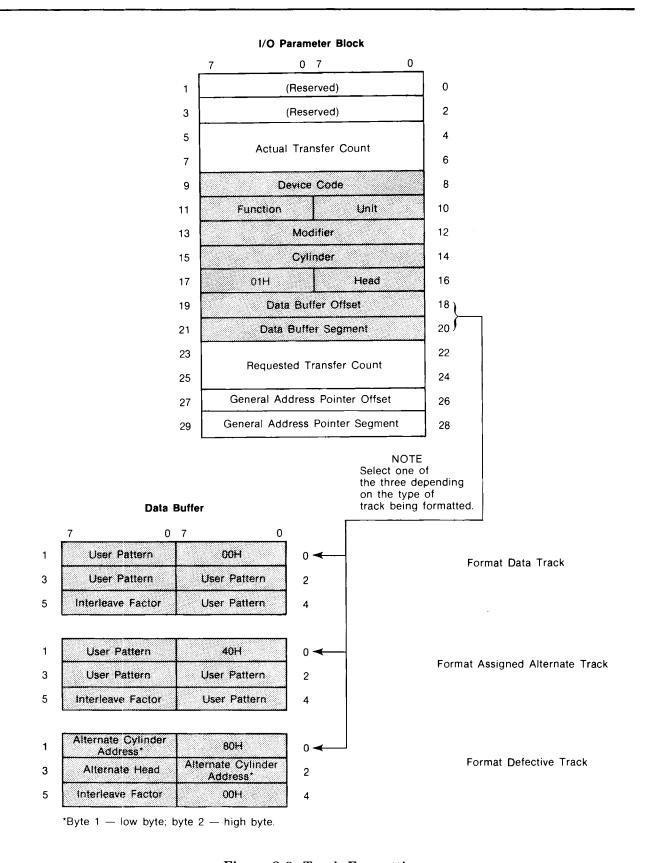

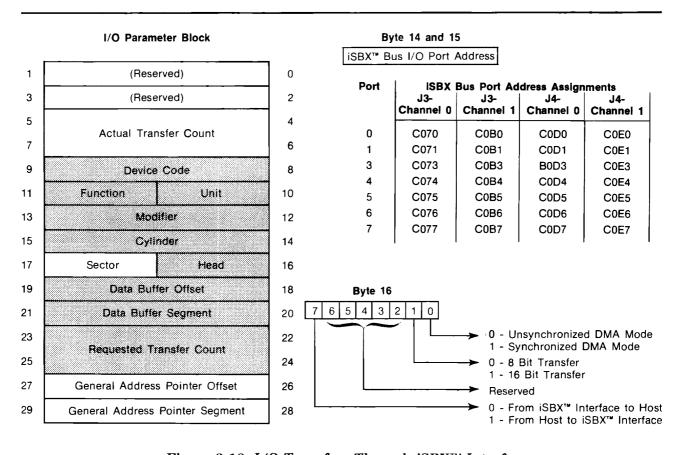

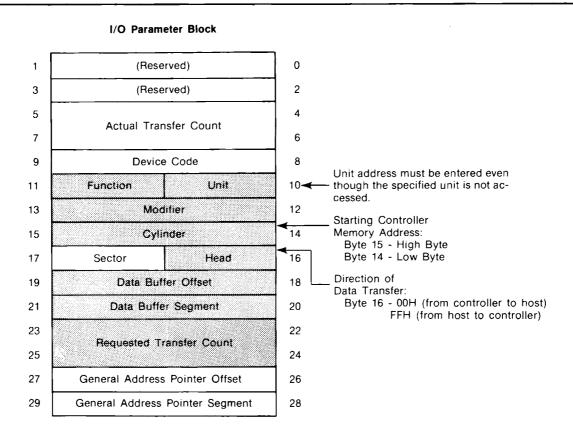

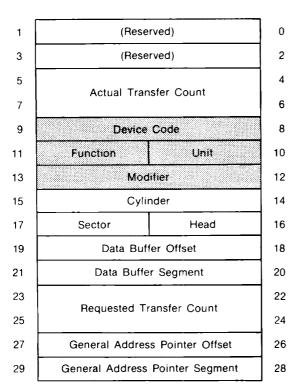

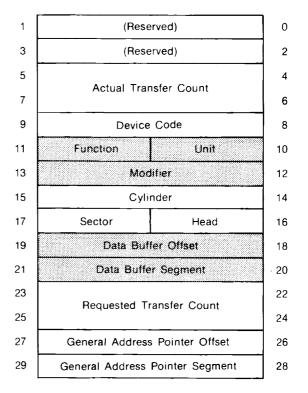

| 3-7.   | I/O Parameter Block Description       | 3-7    | 5-2.  | iSBC 215 Winchester Disk         |             |

| 3-8.   | I/O Communications Blocks Linking     |        |       | Controller Parts Location Diag   | ram 5-7     |

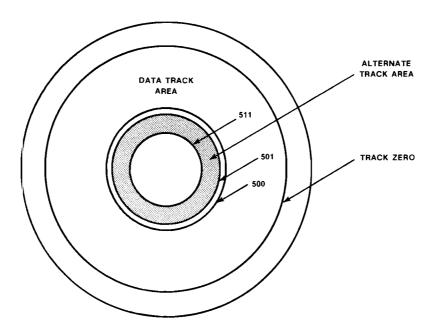

| 3-9.   | Track Formatting                      | 3-11   | 5-2.  | iSBC 215 Winchester Disk         |             |

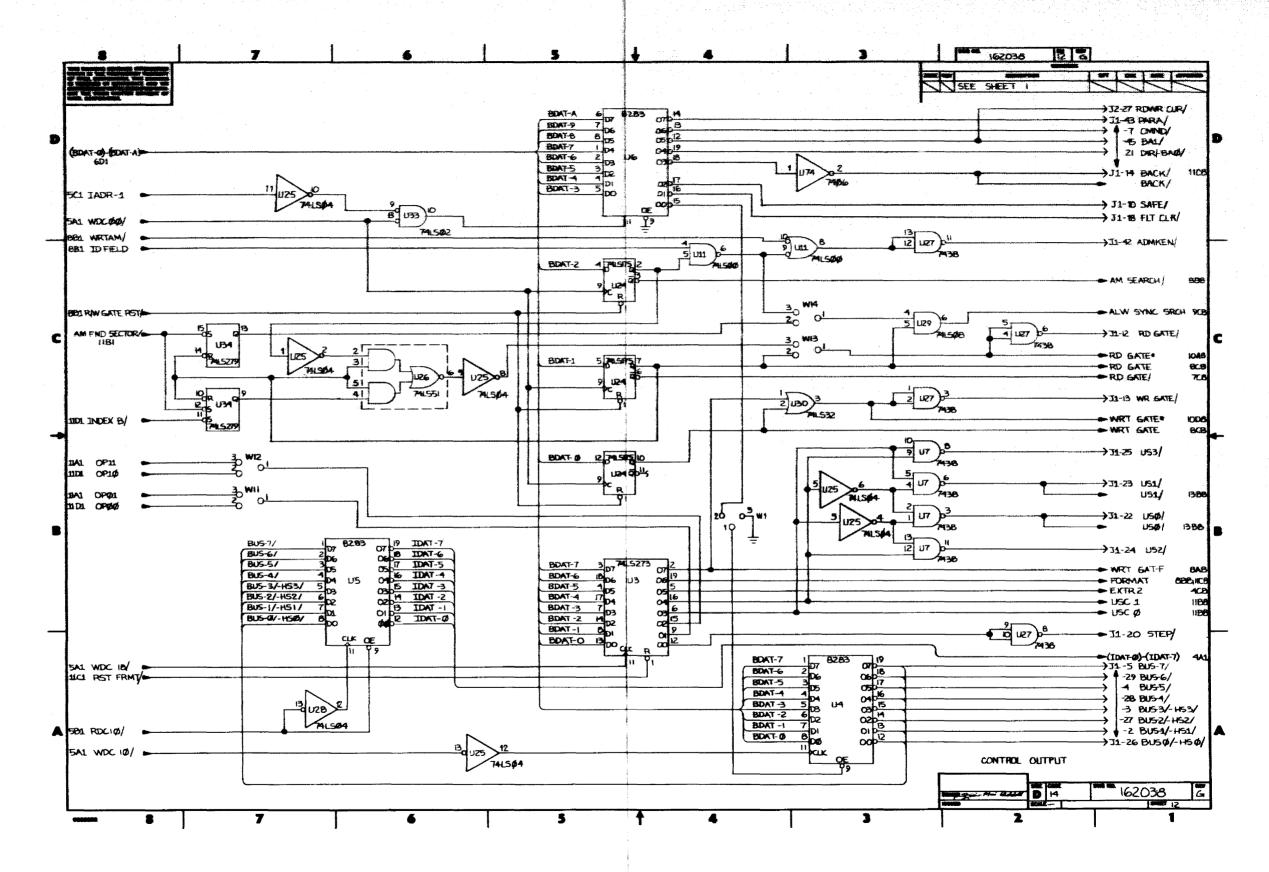

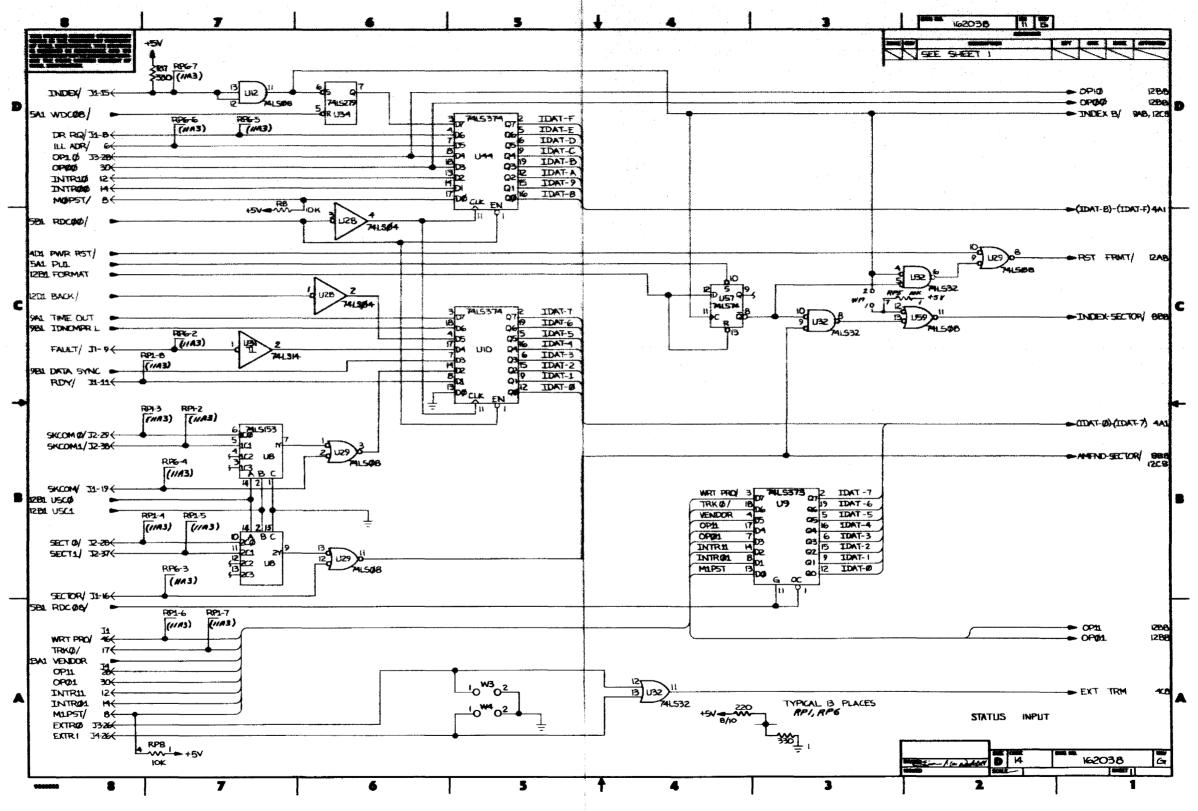

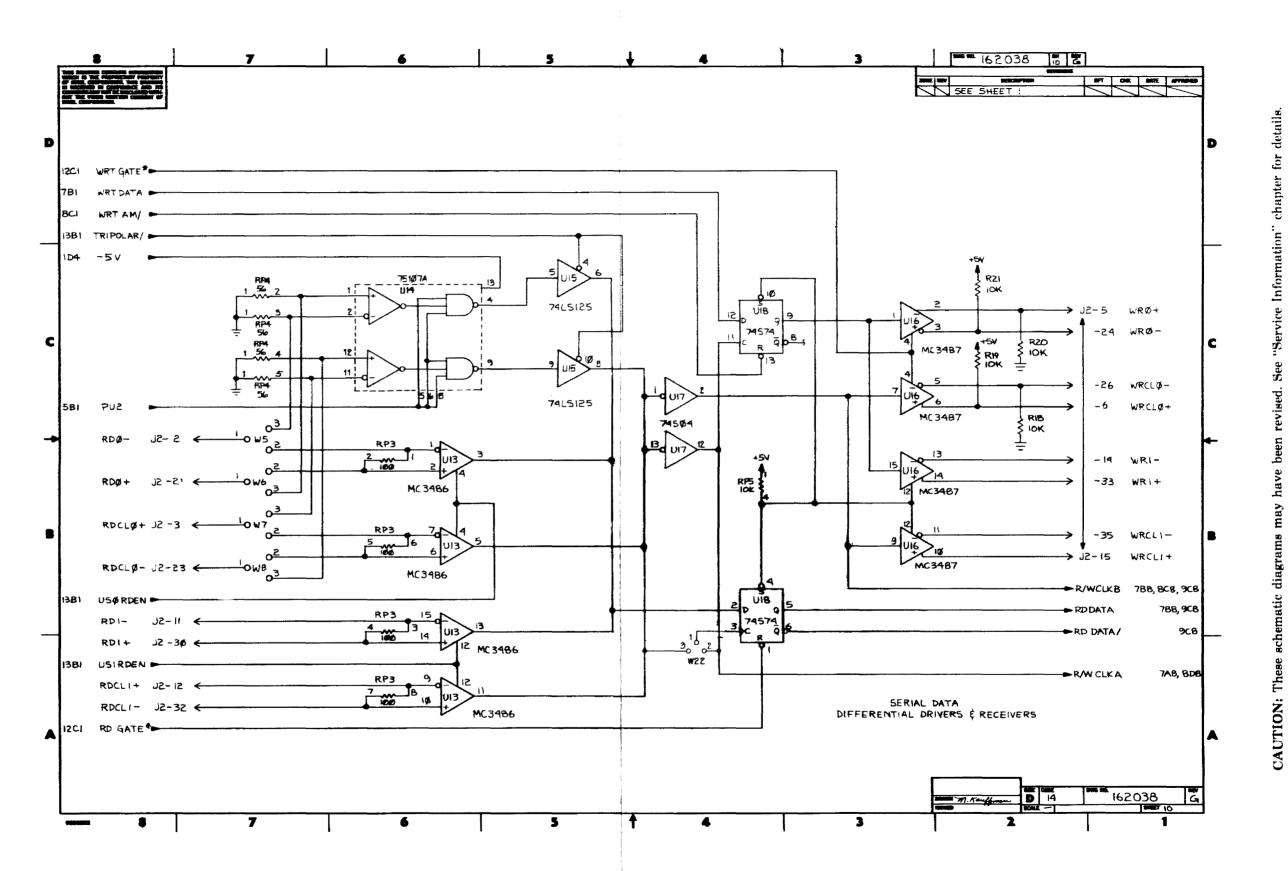

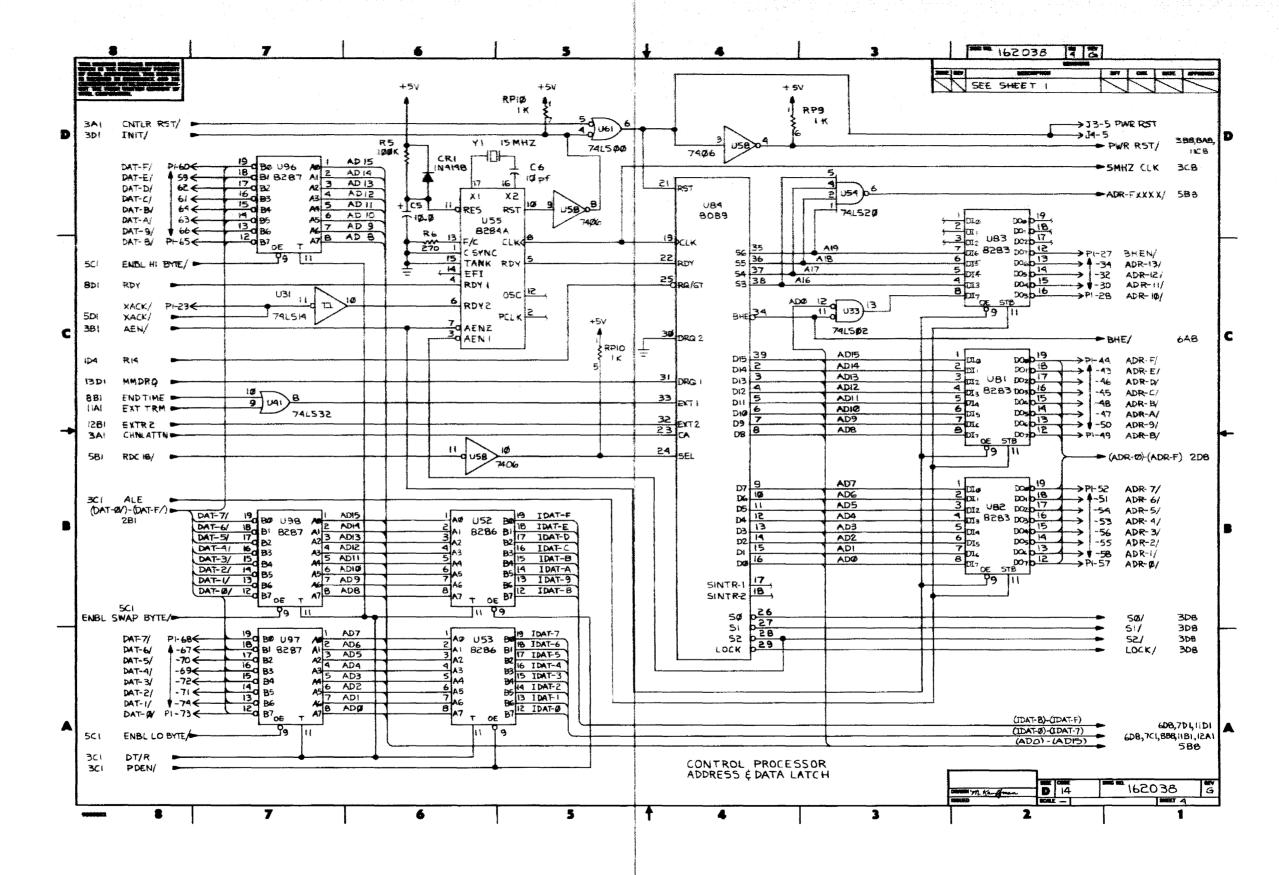

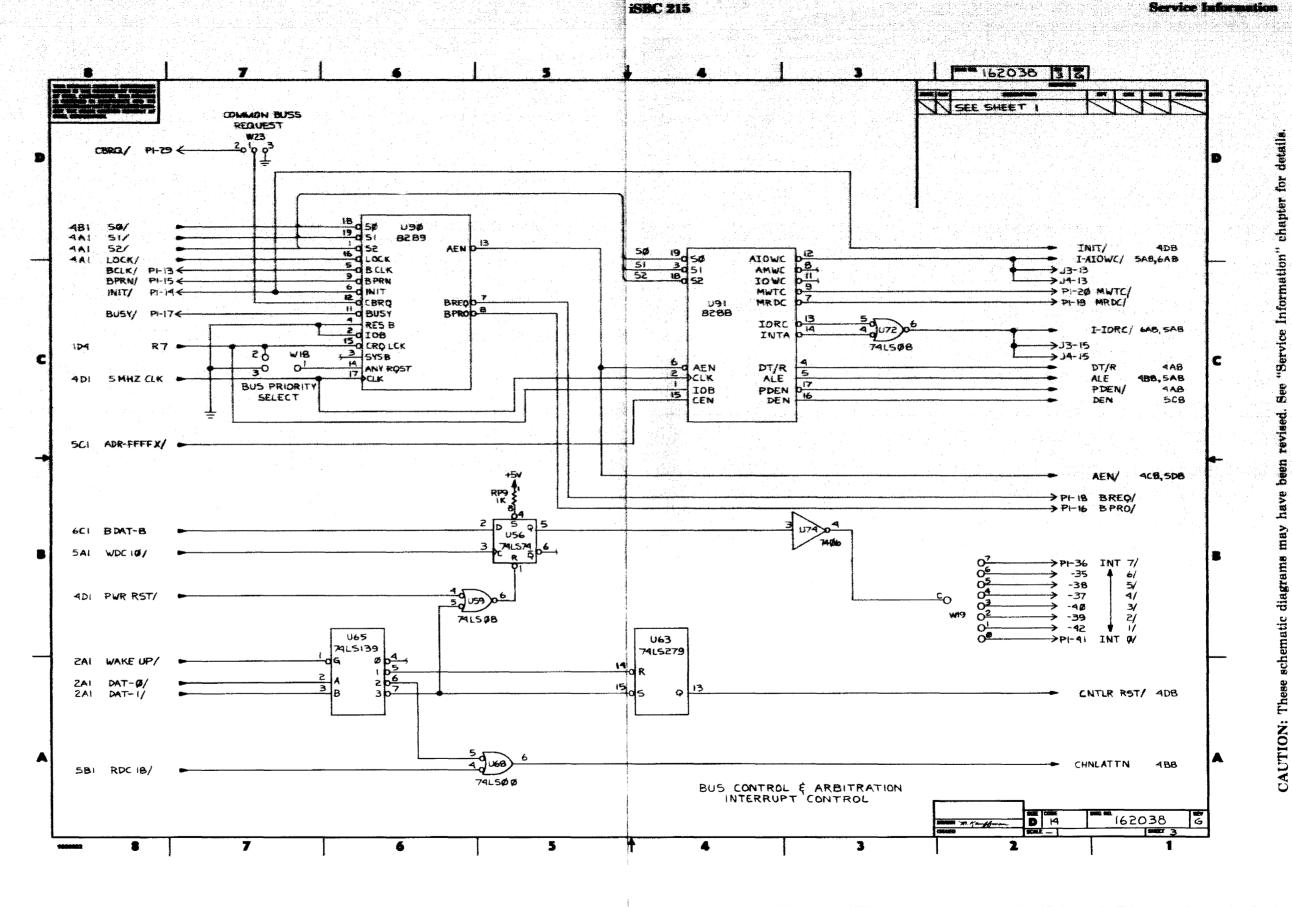

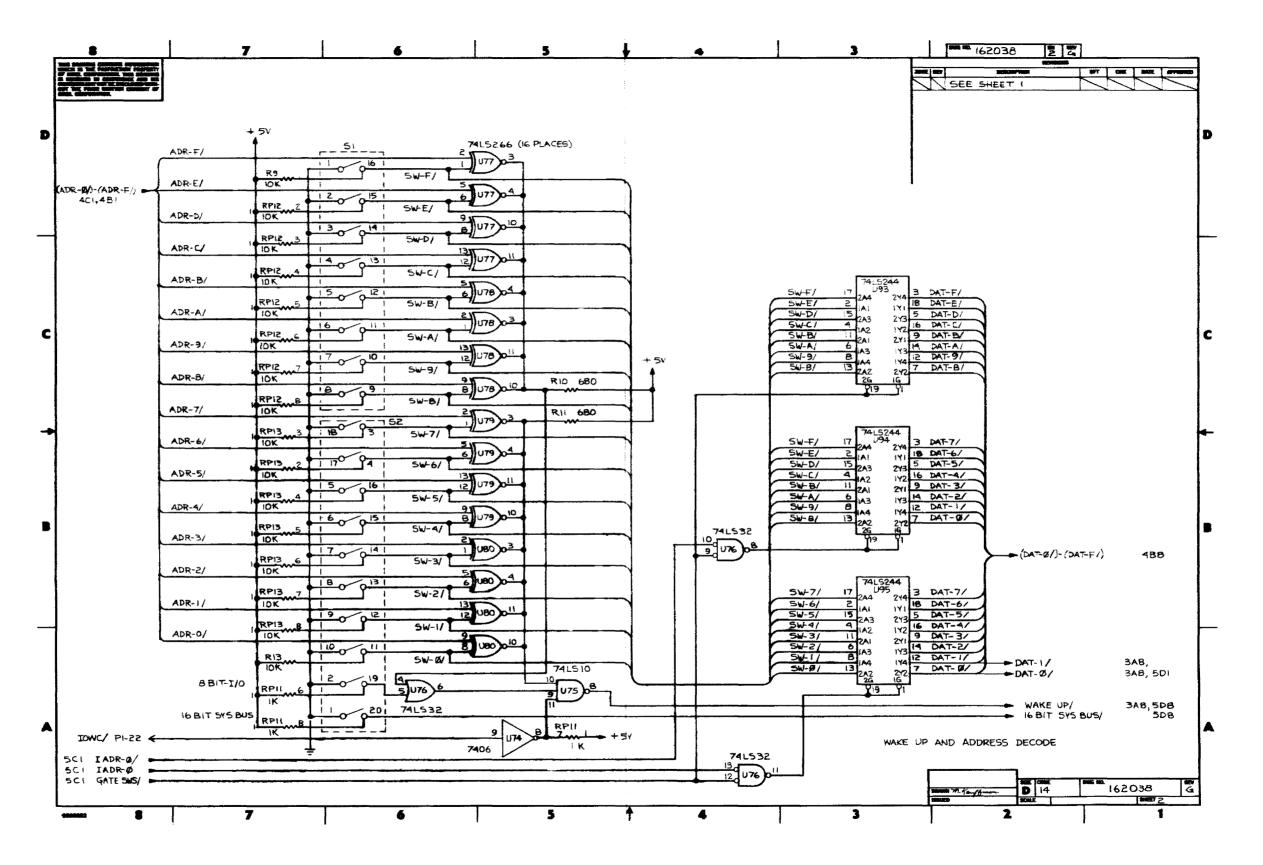

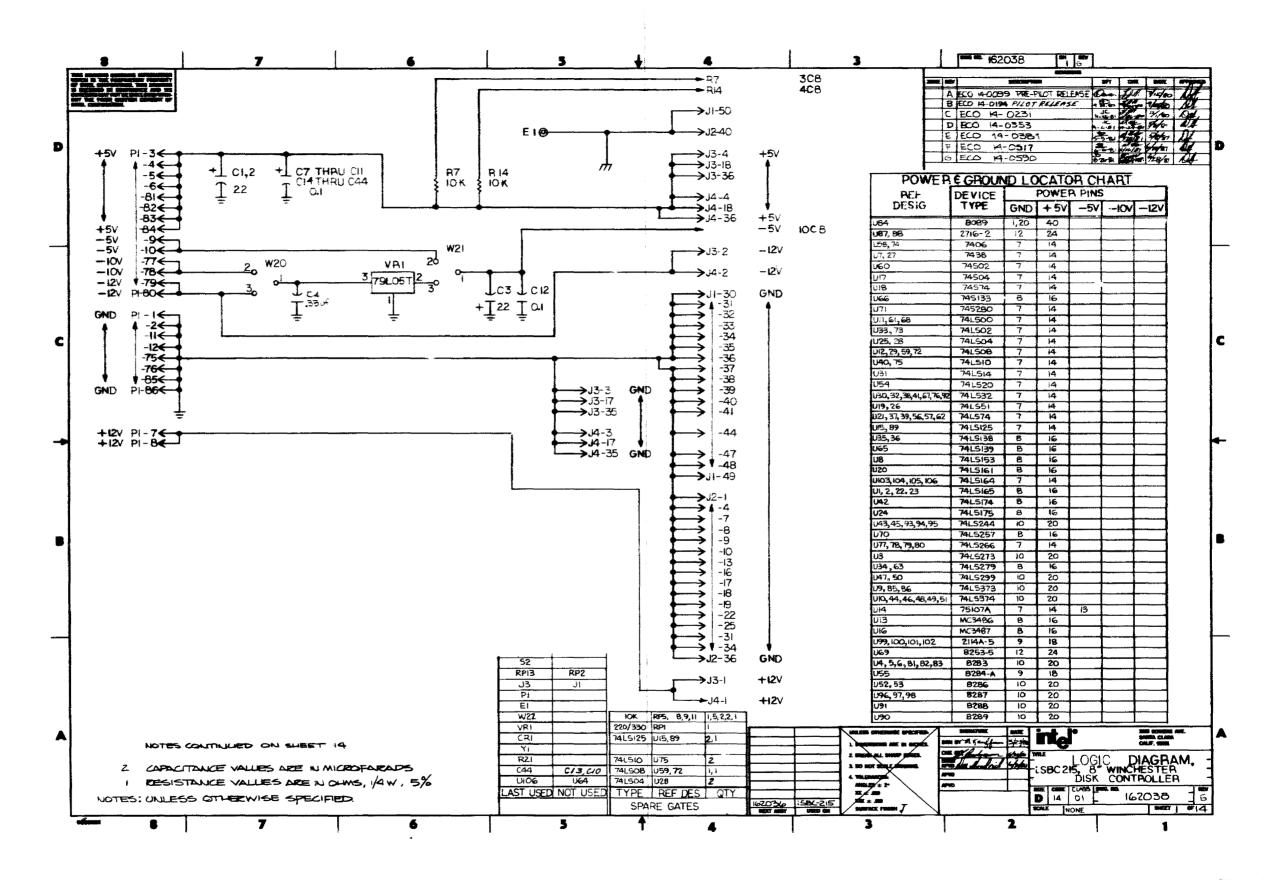

| 3-10.  | Alternate Track Formatting            | . 3-12 |       | Controller Schematic Diagram     | 5-9         |

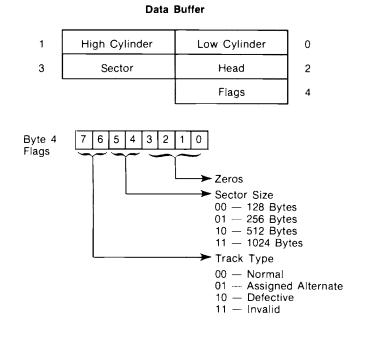

| 3-11.  | Read Sector ID                        | . 3-13 |       |                                  |             |

# CHAPTER 1 GENERAL INFORMATION

## 1-1. INTRODUCTION

The Intel iSBC 215™ Winchester Disk Controller allows up to four Winchester technology disk drives (see Table 1-2 for disk specifications) to be interfaced with any Intel Multibus<sup>TM</sup> interface compatible computer system. It supports drives that use either open loop head positioning (Shugart SA600, SA1000 and SA4000, Quantum Q2000 or Fujitsu 2300, RMS 500, CDC Finch or Memorex 101) or closed loop head positioning (Pertec D8000 or Priam 3350 and 3450). It's design is based on the Intel 8089 I/O Processor, which allows Direct Memory Access (DMA) transfers, error detection and correction, and data management. The controller can operate in a multiprocessor environment and is fully compatible with all Intel 8-bit and 16-bit computers. The number of tracks per surface, sectors per track, bytes per sector and alternate tracks per surface are software selectable for each drive unit. (In addition, the Memorex, 14" Shugart and Priam drives require that the sector size be set internally as shown in Chapter 2.) The single board assembly also features automatic error recovery and retry, transparent data error correction and multiple sector transfers. Seek operations on multiple drives can be overlapped with a read/write operation on another drive. The iSBC 215 controller is fully compatible with Intel 8086 CPU 20-bit addressing.

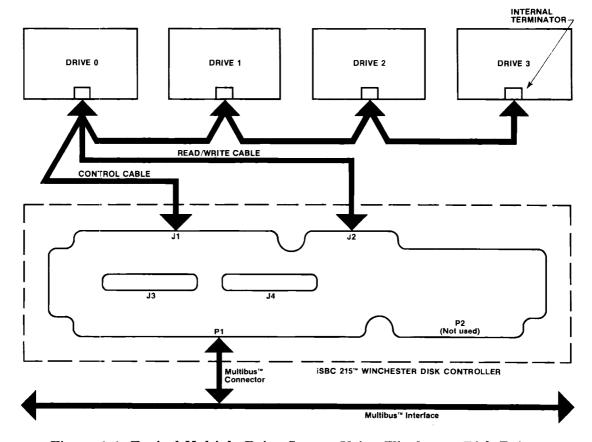

A typical multiple drive system using four Winchester disk drives and the iSBC 215 controller is shown in Figure 1-1. The controller also provides two Intel iSBX™ Bus connectors, J3 and J4, which allow other storage devices such as floppy disk drives or magnetic tape cartridge drives to be interfaced with Multibus interface compatible systems. The Intel iSBX 218™ Flexible Disk Controller, for example, attaches to one iSBX™ Connector, J4, allowing the controller to be interfaced with up to four double-density floppy disk drives. Figure 1-2 shows a typical multiple drive system using four 5½″ or 8″ floppy disk drives, the iSBC

Figure 1-1. Typical Multiple Drive System Using Winchester Disk Drives

General Information iSBC 215

215 controller and the iSBX 218 Flexible Disk Controller. It should be noted that the controller can interface concurrently with Winchester disk drives through connectors J1 and J2, and with other storage devices through the iSBX $^{\text{TM}}$  Connectors, J3 and J4.

# 1-2. DESCRIPTION

The iSBC 215 Winchester Disk Controller is a single board assembly. It may reside in any Intel backplane or in a custom-designed configuration that is physically and electrically compatible with the Intel Multibus interface.

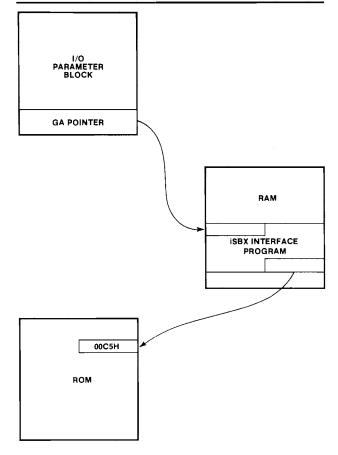

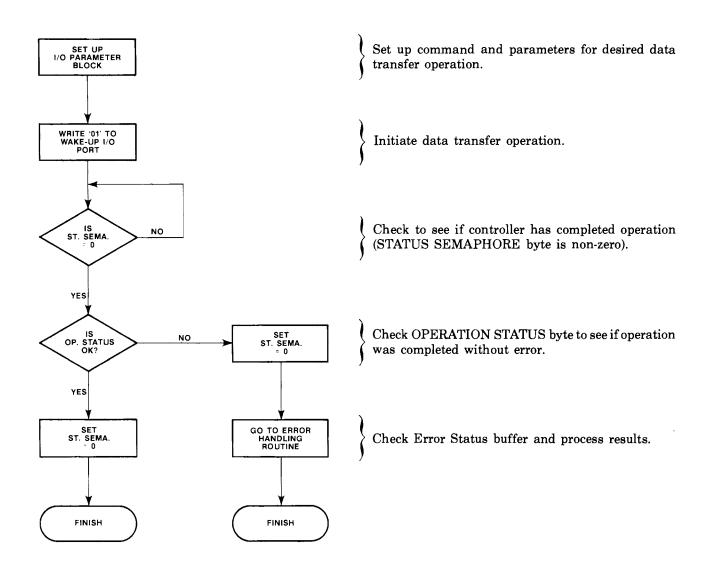

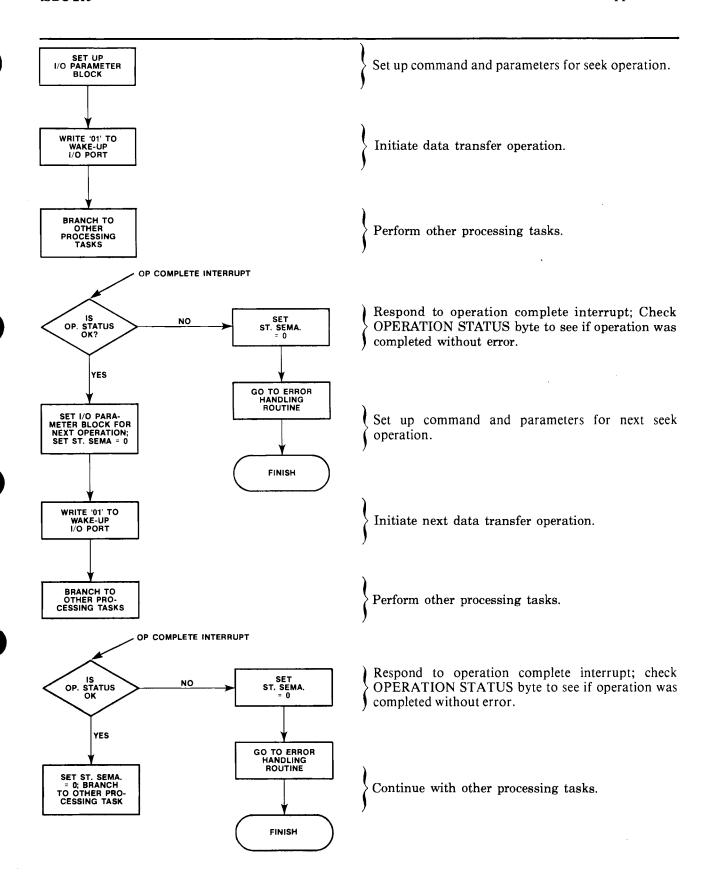

The host Central Processing Unit (CPU) communicates with the Disk controller via four blocks of information in host memory. Once the controller is initialized, a CPU I/O write to the controller Wake-Up Address initiates disk activities. The controller accesses the four blocks in the host memory to determine the specific operation to be performed, fetches the required parameters and completes the specified operation without further CPU intervention.

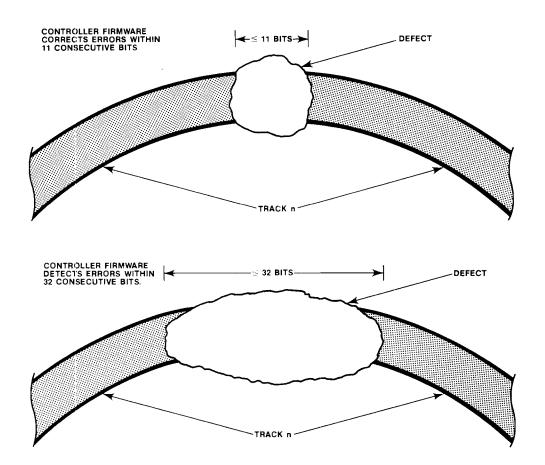

The controller board generates all drive, control and data signals and receives the drive status and data signals required to perform the entire disk drive interfacing task. During a disk read operation, the controller accepts serial data from the disk, interprets synchronizing bit patterns, verifies validity of the data, performs a serial-to-parallel data conversion, and passes parallel data or error condition indications to host memory. During a disk write operation, the controller performs parallel-to-serial data conversion and transmits serial write data and the write clock to the drive. As part of the disk format and write function, the controller appends an Error Checking Code (ECC) at the end of each ID and data field. Using this ECC, the controller hardware can detect errors of up to 32 bits in length; controller firmware can correct errors of up to 11 bits in length (see Figure 1-3).

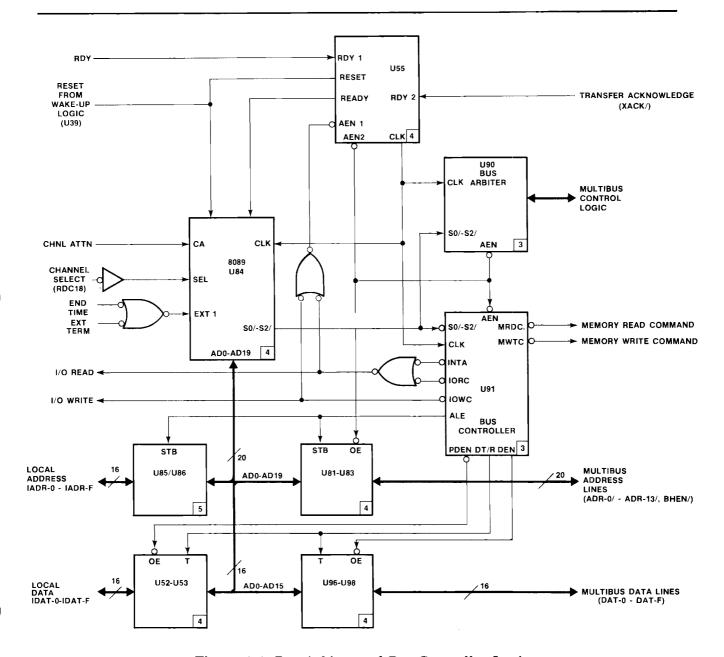

The Intel 8089 I/O Processor provides optimum performance with minimum CPU overhead. An Intel 8288 Bus Controller and 8289 Bus Arbiter control access to the Multibus interface. Intel 2732 EPROMs provide on-board storage of the controller I/O control program and a resident diagnostic exerciser, and 2114 Static RAMs provide local memory for data buffering and for temporary storage of read/write parameters.

Figure 1-2 Typical Multiple Drive System Using Flexible Disk Drives and iSBX 218™ Flexible Disk Controller

iSBC 215 General Information

Figure 1-3. Automatic Error Checking and Correction

# 1-3. SPECIFICATIONS

Table 1-1 lists the physical and performance specifications of the iSBC 215 Winchester Disk Controller;

Table 1-2 lists typical characteristics of the Winchester disk drives that are compatible with the iSBC 215 controller.

Table 1-1. Board Specifications

| COMPATIBILITY |                                                                                                                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU:          | Any Intel mainframe or any Multibus™ interface compatible CPU. The controller can operate with either 16- or 20-bit addresses and with either 8- or 16-bit data bus widths. |

| Disk Drive:   | Winchester disk drives (see Table 1-2); both open-loop and closed-loop head positioning types.                                                                              |

|               | Two versions of controller firmware (located in ROMs U87 and U88) are available, one for use with open-loop type drives and one for closed-loop drives.                     |

|               | Flexible disk drives through on-board iSBX™ Connector (see iSBX 218™ Flexible Disk Controller specifications)                                                               |

Table 1-1. Board Specifications (Continued)

#### DATA ORGANIZATION AND CAPACITY

Bytes per Sector and Sectors per Track:

| Bytes/ | SECTORS 1                        |                |                          |        |             |              |  |  |

|--------|----------------------------------|----------------|--------------------------|--------|-------------|--------------|--|--|

| Sector | 51/4" Rotating<br>Memory Systems | 14"<br>Shugart | Fujitsu 2300/<br>Memorex | Pertec | 8"<br>Priam | 14"<br>Priam |  |  |

| 128    | 54                               | 96             | 64                       | 69     | 70          | 104          |  |  |

| 256    | 31                               | 57             | 38                       | 42     | 42          | 62           |  |  |

| 512    | 17                               | 31             | 21                       | 24     | 23          | 34           |  |  |

| 1024   | 9                                | 16             | 11                       | 12     | 12          | 18           |  |  |

Formatted Disk Capacity:

| Bytes  | FORMATTED CAPACITY/DRIVE <sup>2</sup> |                      |                        |                |  |  |  |

|--------|---------------------------------------|----------------------|------------------------|----------------|--|--|--|

| Sector | 5¼" Rotating<br>Memory Systems        | Control Data<br>Corp | 8" Shugart/<br>Quantum | 14"<br>Shugart |  |  |  |

| 128    | 8.40 MBytes                           | 29.25 MBytes         | 7.08 MBytes            | 19.86 MBytes   |  |  |  |

| 256    | 9.65 MBytes                           | 28.03 MBytes         | 8.12 MBytes            | 23.58 MBytes   |  |  |  |

| 512    | 10.58 MBytes                          | 24.98 MBytes         | 8.91 MBytes            | 25.65 MBytes   |  |  |  |

| 1024   | 11.21 MBytes                          | 19.50 MBytes         | 9.43 MBytes            | 26.48 MBytes   |  |  |  |

| Bytes  | FORMATTED CAPACITY/DRIVE <sup>2</sup> (Cont.) |              |              |              |  |  |

|--------|-----------------------------------------------|--------------|--------------|--------------|--|--|

| Sector | Fujitsu/<br>Memorex                           | Pertec       | 8"<br>Priam  | 14"<br>Priam |  |  |

| 128    | 7.99 MBytes                                   | 12.35 MBytes | 23.29 MBytes | 22.40 MBytes |  |  |

| 256    | 9.49 MBytes                                   | 15.03 MBytes | 27.94 MBytes | 26.71 MBytes |  |  |

| 512    | 10.49 MBytes                                  | 17.17 MBytes | 30.62 MBytes | 29.29 MBytes |  |  |

| 1024   | 10.98 MBytes                                  | 17.18 MBytes | 31.95 MBytes | 31.02 MBytes |  |  |

Drives per Controller:

Winchester Disk Drives — Up to four 8" Shugart, Quantum, Pertec or Priam drives through connectors J1 and J2 (see Table 1-2); up to two Memorex drives or 14" Shugart drives.

Flexible Disk Drives — Up to four 51/4" or 8" drives through the iSBX 218 Flexible Disk Controller connected to the iSBC 215™ board's iSBX™

connector, J4.

**Error Detecting and Correction:**

The controller hardware can detect errors of up to 32 bits in length; controller firmware can correct errors of up to 11 bits in length (see figure 1-3).

#### **CONTROLLER CHARACTERISTICS**

Mounting:

Occupies a card slot in iSBC 604/614 Modular Cardcage/Backplane or equivalent Multibus™ backplane connector.

Physical Characteristics:

Width: Length: Height: Weight:

17.2 cm (6.8 inches) 30.5 cm (12.0 inches) 1.3 cm (0.5 inches) 0.54 kg (19 ounces)

Power Requirements:

$\pm$ 5 Volts  $\pm$ 5% @ 3.25 amperes maximum; -5 Volts  $\pm 5\%$  @ 0.15 amperes maximum.

# NOTE

Jumper and on-board voltage regulator allow -5 Volts or -12 Volts from Multibus™ connector to be used as voltage source for -5 Volt.

Environmental:

Temperature:

0°C to +55°C, operating (+32°F to +131°F).

-55°C to +85°C, non-operating (-67°F to +185°F).

Humidity:

Up to 90%, non-condensing.

<sup>1</sup>Maximum allowable for corresponding selection of Bytes per Sector.

Applies to the following drive models: 51/4" RMS 512, Control Data Corp 9410-32, 8" Shugart SA1004, Quantum Q2010, 14" Shugart SA4008, Memorex 101, Fujitsu 2301, Pertec D8000, 8" Priam 3450 and 14" Pram 3350.

Table 1-2. Winchester Disk Drive Characteristics

|                        | Rotating<br>Memory<br>Systems 5121 | Control<br>Data Corp<br>9410-32 <sup>2</sup> | Shugart<br>SA1004¹/ Quan-<br>tum Q2010 | Fujitsu<br>2301¹<br>Memorex 101 | Pertec<br>D8020 <sup>2</sup> | Priam<br>3450² |

|------------------------|------------------------------------|----------------------------------------------|----------------------------------------|---------------------------------|------------------------------|----------------|

| Capacity (Unformatted) | 12.7 MBytes                        | 31.89 MBytes                                 | 10.6 MBytes                            | 11.7 MBytes                     | 20.13 MBytes                 | 34.94 MBytes   |

| Read/Write Surfaces    | 8                                  | 4                                            | 4/2 <sup>3</sup>                       | 4                               | 3                            | 5              |

| Tracks/Surface         | 153                                | 595                                          | 256                                    | 244                             | 466                          | 520            |

| Bytes/Track            | 10.4 KBytes                        | 13.4 KBytes                                  | 10.4 KBytes                            | 12 KBytes                       | 14.4 KBytes                  | 13.4 KBytes    |

| Transfer Rate          | 625 KBytes/sec                     | 806 KBytes/sec                               | 524 KBytes/sec                         | 593 KBytes/sec                  | 864 KBytes/sec               | 806 KBytes/sec |

| Average Access Time    | 70 msec                            | 50 msec                                      | 70 msec                                | 70 msec                         | 50 msec                      | 50 msec        |

| Rotational Latency     | 8.33 msec                          | 8.33 msec                                    | 9.6 msec                               | 10.1 msec                       | 8.34 msec                    | 8.3 msec       |

| Track to Track         | 3 ms                               | 10 ms                                        | 19 msec                                | 20 msec                         | 12 msec                      | 10 msec        |

Open loop step positioner.

<sup>2</sup>Closed loop servo voice coil technology.

Quantum Q2010 has 2

# CHAPTER 2 PREPARATION FOR USE

## 2-1. INTRODUCTION

This chapter provides information for use in preparing and installing the iSBC 215 Winchester Disk Controller. Included are instructions for unpacking and inspection, installation, setting switches, installing jumpers, and interfacing the controller board with the Multibus connector and disk drives.

#### 2-2. UNPACKING AND INSPECTION

On receipt of the iSBC 215 controller from the carrier, immediately inspect the shipping carton for evidence of damage. If the shipping carton is damaged or water-stained, request that the carrier's agent be present when the carton is opened; if the carrier's agent is not present at the time of opening, keep the carton and packing materials for subsequent agent inspection.

For repairs or replacement of an Intel product damaged during shipment, contact Intel Technical Support Center (refer to Chapter 5) to obtain a Return Authorization Number and further instructions. A copy of the Purchase Order should be submitted to the carrier with the claim.

Carefully unpack the shipping carton and verify that the following items are included:

- iSBC 215 Winchester Disk Controller Printed Wired Assembly

- iSBC 215 Winchester Disk Controller Schematic Diagram

# 2-3. BOARD INSTALLATION CONSIDERATIONS

The iSBC 215 controller can be installed in any Intel cardcage/backplane or any user-designed backplane that is compatible with the Multibus interface and meets the controller's power and Multibus connector dimensional requirements. The controller occupies one backplane slot.

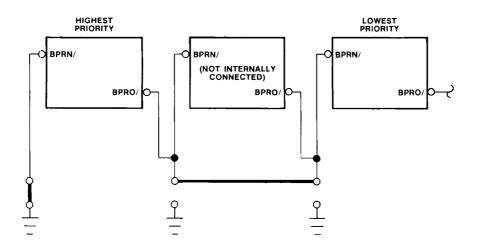

When installing the controller in a serial priority environment (e.g., within any of the Intel system chassis), wiring modifications are required to support serial priority; a daisy-chain technique, see Figure 2-1, establishes priority, The priority input (BPRN/) of the highest priority master is tied to ground. The priority output (BPRO/) of the highest priority master is then connected to the priority

Figure 2-1. Serial Priority Resolution

input (BPRN/) of the next lowest priority master, and so on. ("/" following the signal name indicates an active low). This technique can accommodate a limited number of masters due to gate delays through the daisy-chain.

## 2-4. POWER REQUIREMENT

The board requires a +5 Volt  $\pm 5\%$  power supply at a maximum current of 3.25 amperes, supplied through the Multibus connector. When interfacing with 8" Shugart/Quantum drives, an additional -5 Volt ±5% source at 150 milliamperes maximum is required. This -5-Volt supply can be obtained directly from the Multibus connector or from an on-board regulator that uses either the -10 or -12-Volt source from the Multibus connector (refer to Paragraph 2-14). When interfacing with an iSBX Bus through J3 or J4, additional voltage sources of +12 Volts, -12 Volts or both may be required, also supplied through the Multibus connector. (See individual iSBX Board specifications for tolerances and current requirements of these supplies.) Before installing the controller in a system chassis, make certain that the associated power supplies can supply the additional current that the controller board requires.

#### 2-5. COOLING REQUIREMENT

When the controller is installed in a high temperature environment, make certain the ambient operating temperature does not exceed  $\pm 55^{\circ}$ C.

# 2-6. MULTIBUS™ CONNECTOR

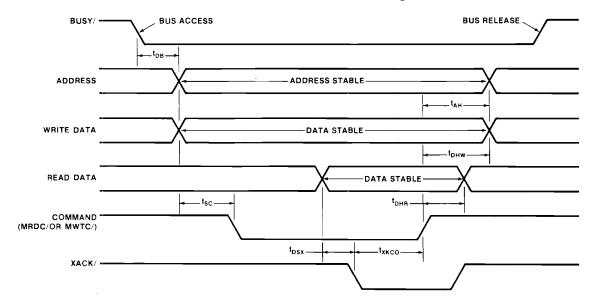

The controller communicates with the CPU and other boards via the Multibus interface. Table 2-1 lists the Multibus connector pin assignments; Table 2-2 describes the controller Multibus interface signals. Figure 2-2 provides a diagram of the controller/Multibus interface timing signals and a table of the timing requirements. Table 2-3 gives current requirements and other characteristics related to the controller/Multibus interface.

The controller is connected to the Multibus interface through connector P1, an 86-pin, double-sided, printed circuit edge connector with 3.96 mm (0.156 in) contact centers. Connector P2 is not used.

# 2-7. SWITCH/JUMPER CONFIGURATIONS

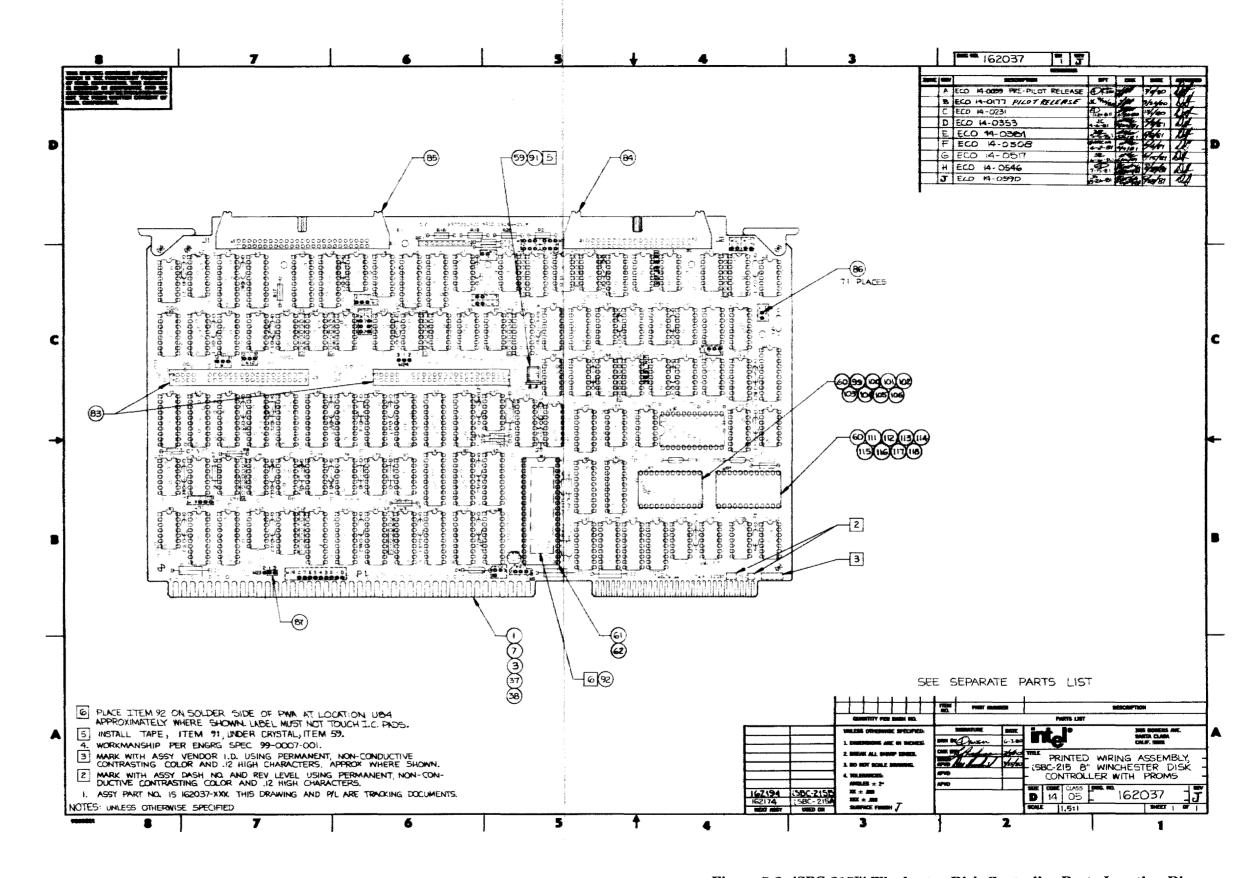

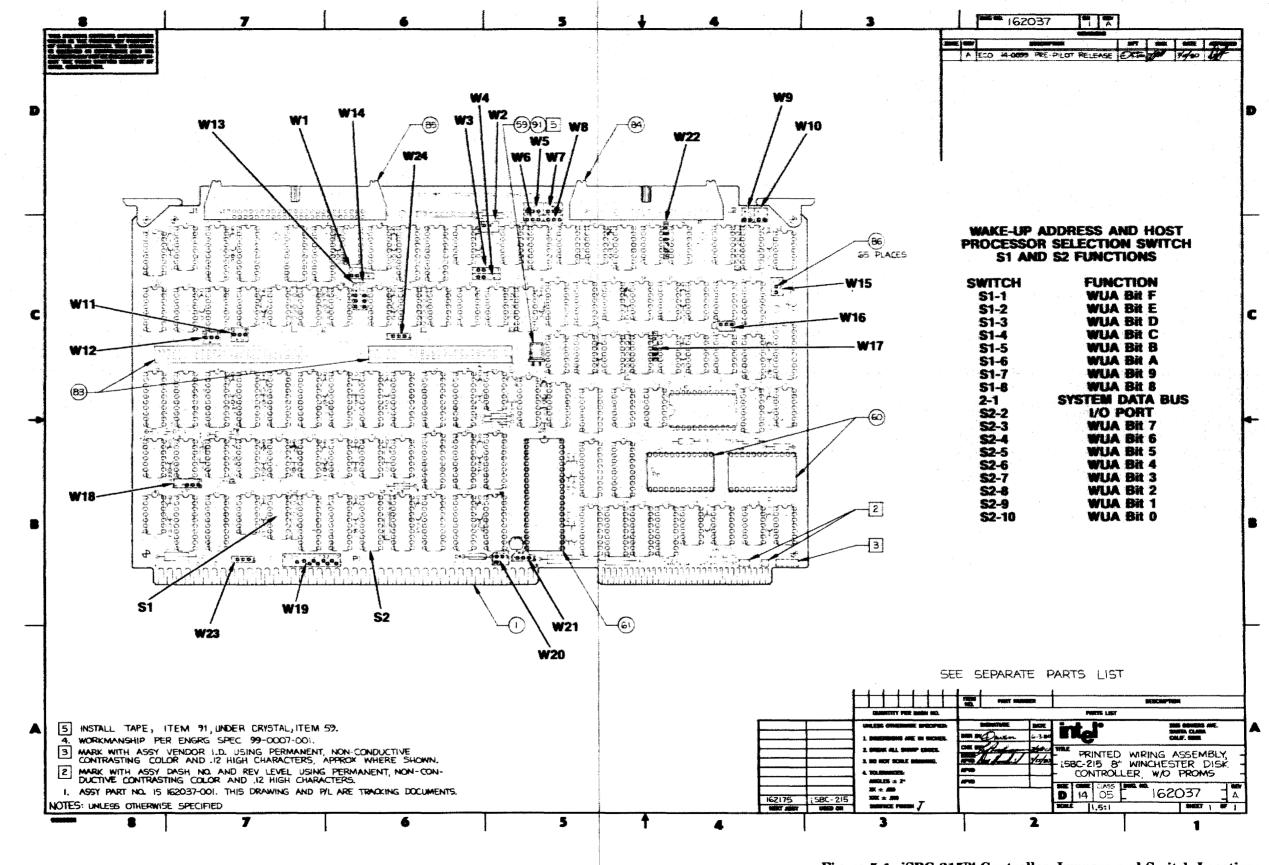

A number of switches and jumpers (see Table 2-4) are provided on the controller board that allow the user to conveniently set the controller for the system environment in which it is to operate (8-bit or 16-bit system data bus, 8-bit or 16-bit I/O addressing, etc.) and for the type of drive to which it is to be interfaced (Shugart/Quantum, Memorex, etc., or iSBX board). Figure 5-1 shows the location of these switches and jumpers on the board. They should be set, as described in the following paragraphs, prior to installing the board in a cardcage or backplane.

Table 2-1. Multibus™ Connector P1 Pin Assignment

|          |     | P1 (Component Side) |                    |     | P1 (Circuit Side) |                               |

|----------|-----|---------------------|--------------------|-----|-------------------|-------------------------------|

|          | Pin | Mnemonic*           | Description        | Pin | Mnemonic*         | Description                   |

|          | 1   | GND                 | Signal GND         | 2   | GND               | Signal GND                    |

|          | 3   | +5V                 | +5Vdc              | 4   | +5V               | +5Vdc                         |

| Power    | 5   | +5V                 | +5Vdc              | 6   | +5v               | +5Vdc                         |

| Supplies | 7   | +12V                | +12Vdc             | 8   | +12V              | +12Vdc                        |

|          | 9   | -5V                 | −5Vdc              | 10  | −5V               | −5Vdc                         |

|          | 11  | GND                 | Signal GND         | 12  | GND               | Signal GND                    |

|          | 13  | BCLK/               | Bus Clock          | 14  | INIT/             | Initialize                    |

|          | 15  | BPRN/               | Bus Pri. In        | 16  | BPRO/             | Bus Pri. Out                  |

| Bus      | 17  | BUSY/               | Bus Busy           | 18  | BREQ/             | Bus Request                   |

| Controls | 19  | MRDC/               | Mem Read Cmd       | 20  | MWTC/             | Mem Write Cmd                 |

|          | 21  | IORC/               | I/O Read Cmd       | 22  | IOWC/             | I/O Write Cmd                 |

|          | 23  | XACK/               | XFER Acknowledge   | 24  | INH1/             | Inhibit 1 disable RAM         |

| D        | 25  |                     | Reserved           | 26  | INH2/             | Inhibit 2 disable PROM or ROM |

| Bus      | 27  | BHEN/               | Byte High Enable   | 28  | ADR10/            | THIRDIT 2 GISGDIC THOM OF HOM |

| Controls | 29  | CBRQ/               | Common Bus Request | 30  | ADR11/            | Address                       |

| and      | 31  | CCLK/               | Constant Clk       | 32  | ADR12/            | Bus                           |

| Address  | 33  | INTA/               | Intr Achknowledge  | 34  | ADR13             | 200                           |

Table 2-1. Multibus™ Connector P1 Pin Assignment (Continued)

|              |          |                       | P1 (Component Side)        |          |                | P1 (Circuit Side)     |  |  |

|--------------|----------|-----------------------|----------------------------|----------|----------------|-----------------------|--|--|

|              | Pin      | Mnemonic*             | Description                | Pin      | Mnemonic*      | Description           |  |  |

| Interrupts   | 35<br>37 | INT6/<br>INT4/        | Parallel<br>Interrupt      | 36<br>38 | INT7/<br>INT5/ | Parallel<br>Interrupt |  |  |

| merupis      | 39<br>41 | IN'T2/<br>IN'T0/      | Requests                   | 40<br>42 | INT3/<br>INT1/ | Requests              |  |  |

| ,            | 43       | ADRE/                 |                            | 44       | ADRF/          |                       |  |  |

|              | 45<br>47 | ADRC/<br>ADRA/        |                            | 46<br>48 | ADRD/<br>ADRB/ |                       |  |  |

| Address      | 49       | ADR8/                 | Address                    | 50       | ADR9/          | Address               |  |  |

| /100/000     | 51       | ADR6/                 | Bus                        | 52       | ADR7/          | Bus                   |  |  |

|              | 53<br>55 | ADR4/<br>ADR2/        |                            | 54<br>56 | ADR5/<br>ADR3/ |                       |  |  |

|              | 57       | ADR0/                 |                            | 58       | ADR1/          |                       |  |  |

|              | 59       | DATE/                 |                            | 60       | DATF/          |                       |  |  |

|              | 61<br>63 | DATC/                 |                            | 62<br>64 | DATD/<br>DATB/ |                       |  |  |

| D - 4 -      | 65       | DAT8/                 | Data                       | 66       | DAT9/          | Data                  |  |  |

| Data         | 67       | DAT6/                 | Bus                        | 68       | DAT7/          | Bus                   |  |  |

|              | 69       | DAT4/                 |                            | 70       | DAT5/          |                       |  |  |

|              | 71<br>73 | DAT2/<br>DAT0/        |                            | 72<br>74 | DAT3/<br>DAT1/ |                       |  |  |

|              | 75       | GND                   | Signal GND                 | 76       | GND            | Signal GND            |  |  |

|              | 77       |                       | Reserved                   | 78       |                | Reserved              |  |  |

| Power        | 79       | -12V                  | −12Vdc                     | 80       | -12V           | -12Vdc                |  |  |

| Supplies     | 81       | +5V<br>+5V            | +5Vdc                      | 82       | +5V            | +5Vdc                 |  |  |

|              | 83<br>85 | GND                   | +5Vdc<br>Signal GND        | 84<br>86 | +5V<br>GND     | +5Vdc<br>Signal GND   |  |  |

| * "/" follow | ving th  | e signal n <b>a</b> m | e indicates an active low. |          | L              | <u> </u>              |  |  |

Table 2-2. iSBC 215™ Controller/Multibus™ Interface P1 Signal Descriptions

| Signal                        | Functional Description                                                                                                                                                                                                                                                                                 |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR0/, ADRF/<br>ADR10/-ADR13/ | Address. These 20 lines transmit the address of the memory location or I/O port to be accessed. For memory access, ADR0/ (when active) enables the even byte bank (DAT0/-DAT7/) on the Multibus¹w connector; i.e., ADR0/ is active for all even addresses. ADR13/ is the most significant address bit. |

| BCLK/                         | Bus Clock. Used to synchronize the bus contention logic on all bus masters.                                                                                                                                                                                                                            |

| BHEN/                         | Byte High Enable. When active low, enables the odd byte bank (DAT8/~DATF/) onto the Multibus™ connector.                                                                                                                                                                                               |

| BPRN/                         | Bus Priority In. When low indicates to a particular bus master that no higher priority bus master is requesting use of the bus. BPRN/ is synchronized with BCLK/.                                                                                                                                      |

| BPRO/                         | Bus Priority Out. In serial (daisy chain) priority resolution schemes, BPRO/ must be connected to the EPRN/ input of the bus master with the next lower bus priority.                                                                                                                                  |

| BREQ/                         | Bus Request. In parallel priority resolution schemes, BREQ/ indicates that a particular bus master requires control of the bus for one or more data transfers. BREQ/ is synchronized with BCLK/.                                                                                                       |

| BUSY/                         | Bus Busy. Indicates that the bus is in use and prevents all other bus masters from gaining control of the bus. BUSY/ is synchronized with BCLK/.                                                                                                                                                       |

| CBRQ/                         | Common Bus Request. Indicates that a bus master wishes control of the bus but does not presently have control. As soon as control of the bus is obtained, the requesting bus controller raises the CBRQ/ signal.                                                                                       |

| DAT0/-DATF/                   | Data. These 16 bidirectional data lines transmit and receive data to and from the addressed memory location or I/O port. DATF/ is the most-significant bit. For data byte operations, DATO/-DAT7 is the even byte and DAT8-DATF/ is the odd byte.                                                      |

Table 2-2. iSBC 215™ Controller/Multibus™ Interface P1 Signal Descriptions (Continued)

| Signal      | Functional Description                                                                                                                                                                                                 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT/       | Initialize. Reset the entire system to a known internal state.                                                                                                                                                         |

| INTO/-INT7/ | Interrupt Request. These eight lines transmit interrupt requests to the appropriate interrupt handler. INTO/ has the highest priority.                                                                                 |

| IÓWC/       | I/O Write Command. Indicates that the address of an I/O port is on the Multibus™ connector address lines and that the contents on the Multibus™ connector data lines are to be accepted by the addressed port.         |

| MRDC/       | Memory Read Command. Indicates that the address of a memory location is on the Multibus™ connector address lines and that the contents of that location are to be read (placed) on the Multibus™ connector data lines. |

| MWTC/       | Memory Write Command. Indicates that the address of a memory location is on the Multibus™ connector address lines and that the contents on the Multibus™ connector data lines are to be written into that location.    |

| XACK/       | Transfer Acknowledge. Indicates that the address memory location has completed the specified read or write operation. That is, data has been placed onto or accepted from the Multibus™ connector data lines.          |

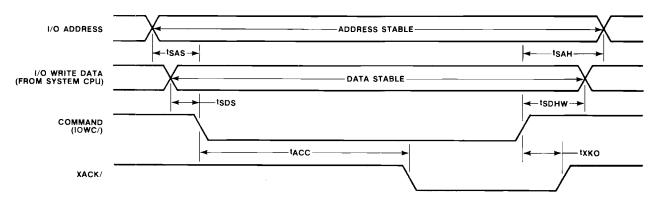

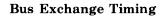

# **Master Command Access Timing**

# **Slave Command Timing**

Figure 2-2. Master Command Access Timing

| Parameter        | Time in Na | noseconds | Description                        |  |  |  |

|------------------|------------|-----------|------------------------------------|--|--|--|

| Parameter        | Minimum    | Maximum   | Description                        |  |  |  |

| tsas             | 50         |           | Address Setup Time to I/O Command  |  |  |  |

| tsds             | 0          |           | Data Setup Time to I/O Command     |  |  |  |

| <sup>t</sup> SAH | 15         |           | Address Hold Time from I/O Command |  |  |  |

| tsDHW            | 30         |           | Data Hold Time from I/O Command    |  |  |  |

| tACC             | 1          | 8000      | I/O Access Time                    |  |  |  |

| txko             | 100        |           | XACK/Hold Time from I/O Command    |  |  |  |

| tBCY             | 125        |           | Bus Clock Cycle Time               |  |  |  |

| tBL              | 65         |           | Bus Clock Low                      |  |  |  |

| tBH              | 35         |           | Bus Clock High                     |  |  |  |

| tDRQ             |            | 35        | Bus Request Delay                  |  |  |  |

| tDBY             |            | 60        | Bus Busy Turn On Delay             |  |  |  |

| tDBYF            |            | 35        | Bus Busy Turn Off Delay            |  |  |  |

| †DBPN            | 15         |           | Priority Input Setup Time          |  |  |  |

| tDBPO            |            | 25        | BPRO/Serial Delay from BPRN/       |  |  |  |

| tWAIT            |            | ∞         | Requesting Master Bus Access Time  |  |  |  |

| tDB              | 50         |           | Busy to Address/Data Delay         |  |  |  |

| tsc              | 50         |           | Address/Data Setup to Command      |  |  |  |

| txKCO            |            | 750       | XACK/ to Command Turn Off          |  |  |  |

| tah              | 50         |           | Address Hold Time                  |  |  |  |

| tDHW             | 50         |           | Data Hold Time                     |  |  |  |

| tDHR             | 0          |           | Read Data Hold Time                |  |  |  |

| tDSX             | 0          |           | Data Setup Time Before XACK/       |  |  |  |

Figure 2-2. Master Command Access Timing (Continued)

Table 2-3. iSBC 215<sup>™</sup> Controller/Multibus<sup>™</sup> Interface Signal Characteristics

|                                          |                |      | Driver 1, 3       |                |                   | Receive                  | r 2, 3            |                                |                   |

|------------------------------------------|----------------|------|-------------------|----------------|-------------------|--------------------------|-------------------|--------------------------------|-------------------|

| Bus                                      | Location       | Type | I <sub>OL</sub>   | Гон            | c <sub>o</sub>    | Location                 | I <sub>IL</sub>   | I <sub>IH</sub>                | Cı                |

| Signals                                  |                |      | Min <sub>ma</sub> | Min $_{\mu a}$ | Min <sub>pf</sub> |                          | Max <sub>ma</sub> | $\mathbf{Max}_{\mu\mathbf{a}}$ | Max <sub>pf</sub> |

| DAT0/-<br>DATF/<br>(16 lines)            | Masters        | TRI  | 32                | <b>-5000</b>   | 300               | Masters<br>and<br>Slaves | -0.5              | 125                            | 18                |

| ADR0/-<br>ADR13/,<br>BHEN/<br>(21 lines) | Masters        | TRI  | 32                | -5000          | 300               | Slaves                   | -0.8              | 90                             | 18                |

| MRDC/,<br>MWTC/                          | Masters        | TRI  | 32                | -5000          | 300               | Slaves                   | -0.7              | 50                             | 18                |

| IOWC/                                    |                |      |                   |                |                   | Slaves                   | -0.4              | 20                             | 5                 |

| XACK/                                    | Slaves         | TRI  | 48                | -2000          | 300               | Masters                  | -1.2              | 60                             | 18                |

| BCLK/                                    |                |      |                   |                |                   | Master                   | -0.5              | 60                             | 18                |

| BREQ/                                    | Each<br>Master | TTL  | 10                | -400           | 60                |                          |                   |                                |                   |

| BPRO/                                    | Each<br>Master | TTL  | 10                | -400           | 60                |                          |                   |                                |                   |

| BPRN/                                    |                |      |                   |                |                   | Master                   | 0.5               | 60                             | 18                |

| BUSY/,<br>CBRQ                           | All<br>Masters | O.C. | 20                | -              | 250               | All<br>Masters           | -0.5              | 60                             | 18                |

| INIT/                                    |                |      |                   |                |                   | All                      | -0.5              | 60                             | 18                |

| INTO/-<br>INT7/<br>(8 lines)             | Slaves         | O.C. | 40                | -              | 300               |                          |                   |                                |                   |

#### Notes:

1. Driver Requirements:

IOH = High Output Current Drive IOL = Low Output Current Drive Co = Capacitance Drive Capability

TRI = 3-State Drive

O.C.= Open Collector Driver TTL = Totem-pole Driver

2. Receiver Requirements:

$I_{IH}$  = High Input Current Load  $I_{IL}$  = Low Input Current Load

C<sub>1</sub> = Cap Active Load

3. Low and High Voltage Requirements:

Receiver:

$0 \le V_{IL} \le 0.8V$

$2.0V \le V_{IH} \le 5.5V$

Driver:

$0 \le V_{OL} \le 0.5V$

$2.4V \le V_{OH} \le 5.5V$

# 2-8. WAKE-UP ADDRESS SELECTION

The controller communicates with the host CPU through four I/O communications blocks located in the host memory. When the controller is to receive instructions, it goes to the beginning address of the first I/O communication block. This address is called the wake-up address (WUA). The WUA may be at any address in host memory. Sixteen WUA

switches (S1-1 through S1-8 and S2-3 through S2-10, see Figure 5-1) are provided on the controller board that allow the user to set the controller for the selected wake-up address. The function of each switch is shown in the table in Figure 5-1. Any switch set to ON represents a logical 1.

The controller multiplies the settings of the WUA switches by 2<sup>4</sup> (shifts the number four places to the

left) to create a 20-bit WUA. Note that due to this shift, the four least-significant bits of the selected WUA must be zeros. When accessing host memory, the controller transmits the entire 20-bit WUA through the Multibus interface. If the host memory uses 16-bit addressing, the four most significant bits of the 20-bit WUA must be zero. This is accomplished by setting the four most significant bits of the WUA switches (S1-1 through S1-4) to zero.

Table 2-4. Configuration Jumpers and Switches

| Function                                                 | Pin or Switch                                         |

|----------------------------------------------------------|-------------------------------------------------------|

| Wake-Up Address                                          | S1-1 through S1-8<br>S2-3 through S2-10               |

| 8-Bit or 16-Bit System<br>Data Bus Capability            | S2-1                                                  |

| 8-Bit or 16-Bit Host<br>Processor I/O Port<br>Addressing | S2-2                                                  |

| Interrupt Priority Level                                 | W19-C to W19-0<br>through W19-7                       |

| Any Request                                              | W18                                                   |

| Common Bus Request                                       | W23                                                   |

| Voltage Selection                                        | W20- and W21                                          |

| Winchester Drive<br>Manufacturer Selection               | W1, W2, W5, W6<br>through W10<br>W13 through W17, W22 |

| iSBX Bus Control                                         | W3, W4, W11 and W12, W24                              |

# 2-9. WAKE-UP I/O PORT ADDRESS SELECTION

The host processor communicates with the controller through an I/O port. The WUA switches also set the address of this I/O port. For a host processor with 8-bit I/O port addressing, bits 0 through 7 of the unshifted WUA determine the wake-up I/O port address; for a host processor with 16-bit I/O port addressing, bits 0 through F determine the address.

I/O Address Selection switch S2-2 on the controller board (see Figure 5-1) determines the type of I/O port addressing the host processor uses: ON for 16-bit addressing; OFF for 8-bit addressing.

## 2-10. SYSTEM DATA BUS SELECTION

System data bus selection switch S2-1 on the controller board (see Figure 5-1) sets the controller for the type of system data bus with which the controller is to interface: ON for 16-bit bus, OFF for an 8-bit bus. This switch allows the controller to use its 16-bit data transfer mode to access the system bus (if the system memory supports 16-bit accesses), even though the host processor only supports 8-bit accesses.

## 2-11. INTERRUPT PRIORITY LEVEL

The controller's internal interrupt request signal can be assigned to any of eight interrupt priority levels (INT0/ to INT7/) on the Multibus connector. To select the interrupt request priority level, place a jumper link as shown in Table 2-5 and Figure 5-1.

Table 2-5. Interrupt Priority Level Selection

| Duinuitu                   | Wire Wrap |        |  |  |  |  |

|----------------------------|-----------|--------|--|--|--|--|

| Priority<br>Level Selected | From Pin  | To Pin |  |  |  |  |

| 0                          | W19-C     | W19-0  |  |  |  |  |

| 1                          | W19-C     | W19-1  |  |  |  |  |

| 2                          | W19-C     | W19-2  |  |  |  |  |

| 3                          | W19-C     | W19-3  |  |  |  |  |

| r                          | W19-C     | W19-4  |  |  |  |  |

| 5                          | W19-C     | W19-5  |  |  |  |  |

| 6                          | W19-C     | W19-6  |  |  |  |  |

| 7                          | W19-C     | W19-7  |  |  |  |  |

# 2-12. ANY REQUEST SELECTION

The *any request* function allows the controller to be set to relinquish control of the Multibus interface following a request from:

- A higher priority device only (jumper between pins W18-1 and W18-2 on the controller board).

- 2. Any device, lower or higher priority, (jumper between pins W18-1 and W18-3).

Figure 5-1 shows the location of the selection pins.

## 2-13. COMMON BUS REQUEST

The common bus request function allows the controller to take advantage of higher bus transfer rates by arbitrating for the use of the bus only when other bus controllers have access requests pending. The controller will:

- Arbitrate for the bus on every access, (jumper between pins W23-1 and W23-2 on the controller). This mode is used when other bus controllers do not implement common bus request.

- 2. Arbitrate for the bus to acquire the bus for the first access and rearbitrate only when another bus controller requests use of the bus.

## 2-14. WINCHESTER DRIVE INTERFACE

The iSBC 215 Winchester Disk Controller has been designed to communicate with any of four unique

|               | MANUFACTURER  |   |      |     |                                   |               |      |           |              |   |            |         |            |                      |

|---------------|---------------|---|------|-----|-----------------------------------|---------------|------|-----------|--------------|---|------------|---------|------------|----------------------|

| Jumper<br>No. | 51/4"<br>From |   | Quan | tum | Memo<br>14" Sh<br>Fujitsu<br>From | ugart<br>2300 | Perl | lec<br>To | Pria<br>From |   | CD<br>From | C<br>To |            | Function             |

| W1            | 1             | 3 | 1    | 3   | 1                                 | 3             | 1    | 2         | 1            | 2 | 1          | 3       | Open/Cios  | sed Head Positioning |

| W2            | -             |   |      | _   | 1                                 | 2             | _    | _         | 1            | 2 | 1          | 2       | Vendor Se  | elect                |

| W5            | 1             | 2 | 1    | 3   | 1                                 | 2             | 1    | 2         | 1            | 2 | 1          | 3       | RD —       |                      |

| W6            | 1             | 2 | 1    | 3   | 1                                 | 2             | 1    | 2         | 1            | 2 | 1          | 3       | RD+        | Level                |

| W7            | 1             | 2 | 1    | 3   | 1                                 | 2             | 1    | 2         | 1            | 2 | 1          | 3       | RDCL+      | Select               |

| W8            | 1             | 2 | 1    | 3   | 1                                 | 2             | 1    | 2         | 1            | 2 | 1          | 3       | RDCL-      | )                    |

| W9            | _             | _ | 1    | 2   | l —                               | _             | _    | _         |              | _ | 1          | 2       | Shugart T  | ri-State Select      |

| W10           | 1             | 2 | 1    | 2   | _                                 | _             | 1    | 2         | 1            | 2 | 1          | 2       | Radial Sel | ect                  |

| W13           | 1             | 2 | 1    | 2   | 1                                 | 3             | 1    | 2         | 1            | 3 | 1          | 3       | Hard/Soft  | Sectoring            |

2

3

1

Table 2-6. 8" Winchester Drive Manufacturer Selection

# NOTE

W14

W15

W16

W17

W22

means not installed

2

2

1

1

The iSBX bus control jumpers, W3, W4, W11 and W12, are factory wired for the configuration required when the iSBX Bus is not being used. See Paragraph 2-17 and Table 2-9 for a description of the use of these jumpers.

2

2

2

2

3

2

1

1

Winchester technology disk drive interfaces: 8" Shugart/Quantum, Memorex/14" Shugart, Pertec and Priam. The Shugart, Quantum and Memorex drives use a stepper motor for head positioning (called open-loop head positioning); the Pertec and Priam drives use a linear positioner coupled with a servo surface on one disk for position feedback (closed-loop head positioning).

2

2

2

1

The manufacturer's models with which the controller interfaces are: 8" Shugart (Models SA1002 and SA1004), Quantum (Models Q2010, Q2020, Q2030 and Q2040), Memorex (Models 101 and 102), 14" Shugart (Models SA4004 and SA4008), Pertec (Model D8000), Rotating Memory Systems (Models 506 and 512) and Control Data Corporation (Models 9410 24 and 32), Priam (Models 570, 1070, 2050, 3350 and 3450).

The controller can control up to four 8" Shugart, Quantum, Pertec or Priam drives, or up to two Memorex or 14" Shugart drives. It cannot control drives of different manufacturers concurrently.

The jumpers listed in Table 2-6 allow the controller to be set for the selected drive type. In addition, two versions of the controller firmware (located in ROMs U87 and U88) are available, one for use with open-loop type drives and one for closed-loop drives. Boards configured for use with open-loop drives come from the factory with open-loop firmware installed and with jumpers preset for 8" Shugart/Quantum drives; boards configured for closed-loop

drives come with closed-loop firmware and with jumpers preset for Pertec drives. Converting the controller from the 8" Shugart/Quantum interface to a Memorex/14" Shugart interface or from Pertec to Priam merely requires changing the connections of some of the jumpers as shown in Table 2-6 and Figure 5-1. Converting the controller from an openloop interface to a closed-loop interface, and vice versa, requires the ROMs to be changed in addition to changing jumpers.

Shugart AM Control

Shugart GAP Control

Pertec RD Clock Select

Hard/Soft Sectoring

**INDEX Select**

3

2

3

2

2

Interface cables must also be constructed and installed according to the type of drive being used as described in Paragraph 2-15.

# 2-15. -5-VOLT SELECTION (8" SHUGART/ QUANTUM CDC DRIVES ONLY)

Figure 5-1 shows the location of the Voltage Selection pins for the -5 Volt power supply. Install jumpers as described in Table 2-7 to select -5 volts either from the Multibus connector or from the on-board regulator and to select the voltage source for the regulator.

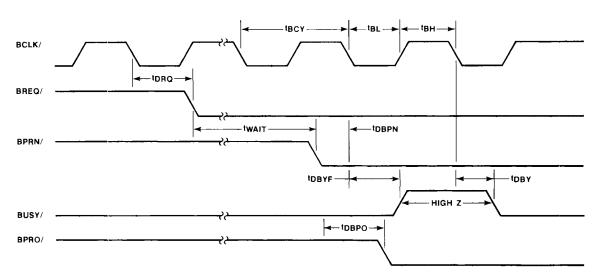

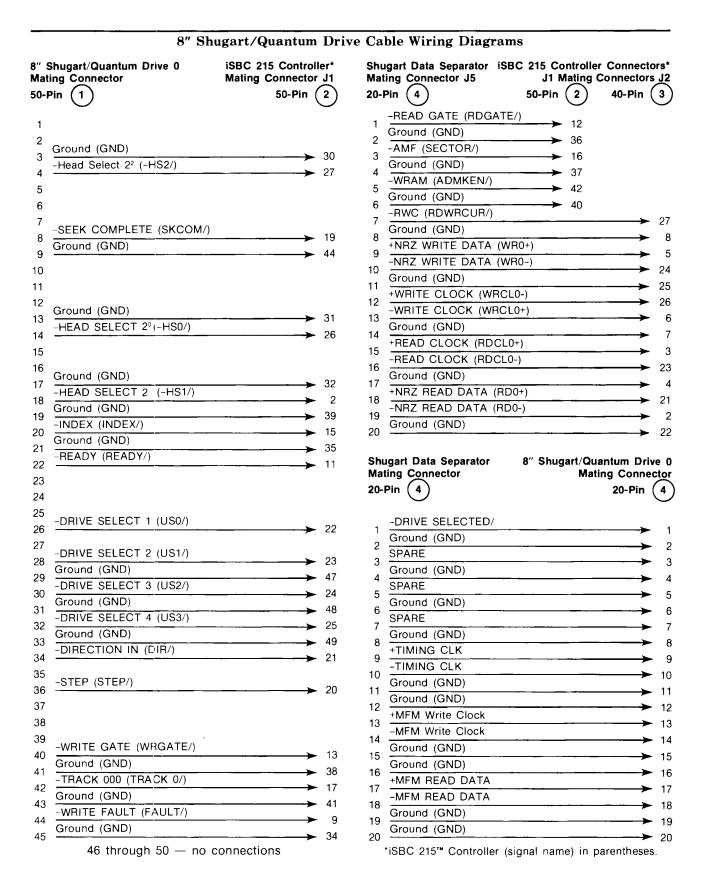

## 2-16. CABLING REQUIREMENTS

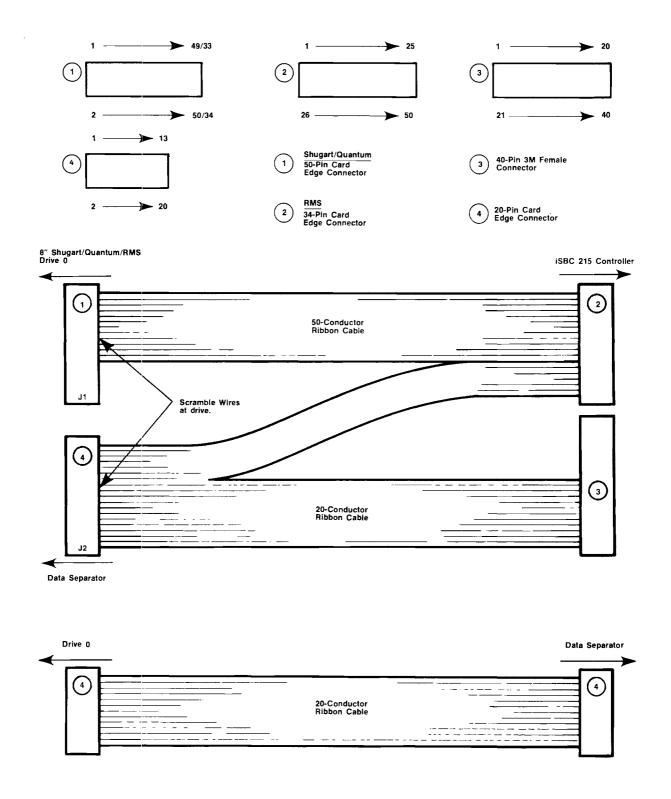

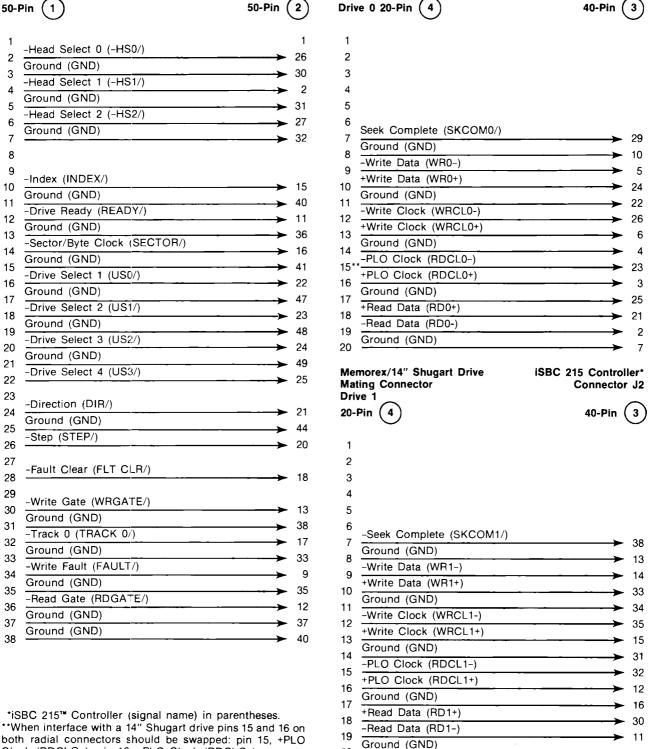

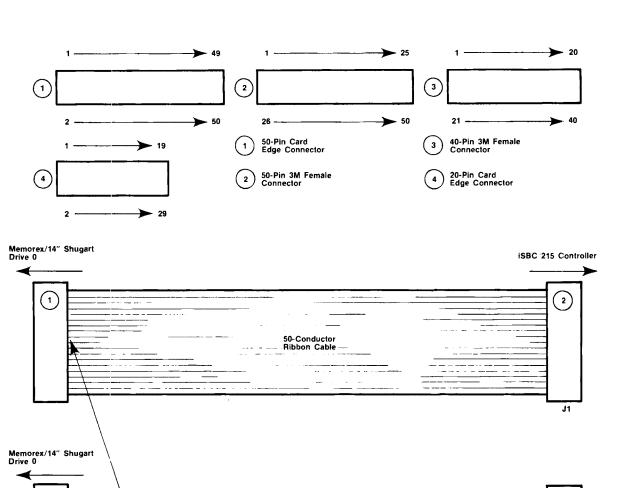

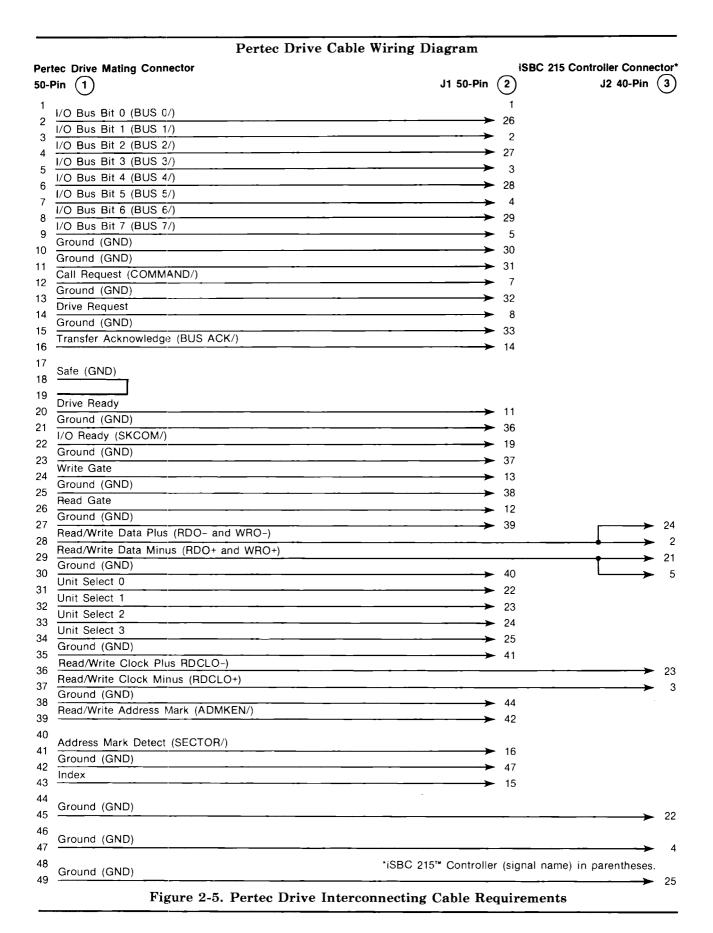

Interface cables between the controller and the disk drives must be fabricated according to the type of drive being used and the number of drives. Figures 2-3 through 2-7 show the connector pin assignments for the controller and for each type of drive. A 50-pin mass-terminated socket connector 3M 3425/6050 or

equivalent, is recommended for mating with J1 of the controller board. A 40-pin 3M 3417-6040 or equivalent connector is recommended for mating with J2. The mass-terminated sockets are easily attached to flat ribbon cable using the jig that the connector manufacturer supplies. The Control Cable that connects to J1 requires a 50-conductor ribbon cable; the Read/Write cable that connects to J2 requires one or two 20-conductor ribbon cables, depending on the drive configuration (refer to Paragraph 2-16). Cable length for the control cable cannot exceed a total length of 10 feet; total length for any Read/Write cable must not exceed 10 feet. See the respective service manual for the type of connectors required for the cable end that connects to the drives.

Each of the cables shown in Figures 2-3 through 2-7 require a number of wire cross-overs "scrambling" between the controller connectors and the drives. It is suggested that the scrambling be done at the drive interface connector.

# NOTE

The cabling and drive interconnecting information given in Paragraphs 2-15 and 2-16 and in Figures 2-3 through 2-6, reflect the specifications at the time this manual was printed. Before proceeding with construction of interconnecting cables, check the drive's hardware reference manual for current pin assignments and interface requirements.

## 2-17. DRIVE INSTALLATION

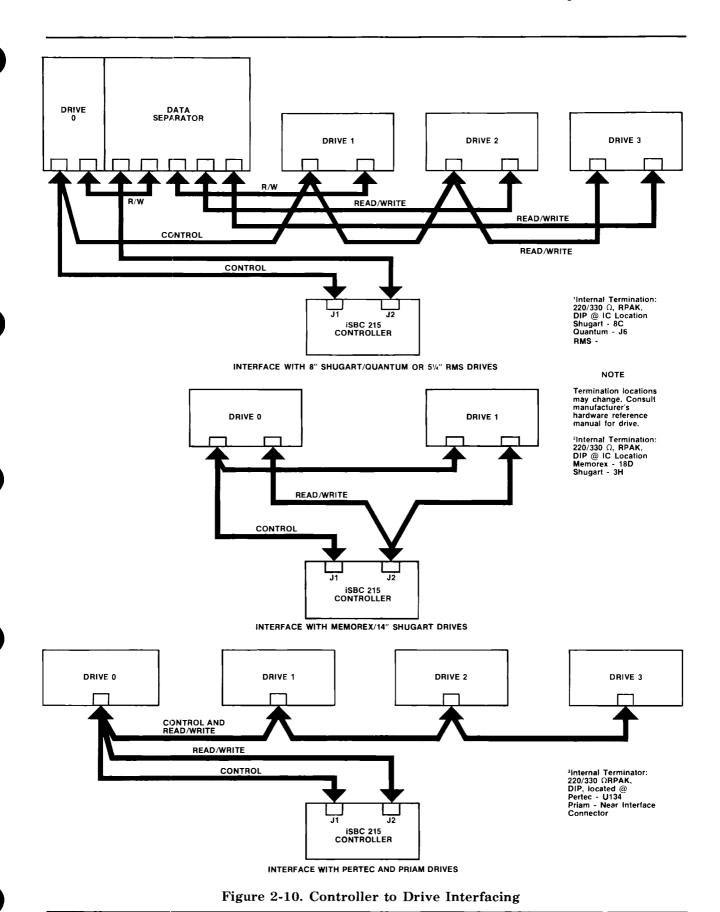

The requirements for connecting the controller to the disk drive or drives varies between drive types. The following discussion and Figure 2-10 describes the specific interconnection requirements for each drive type.

Shugart SA1000 or Quantum Q2000. When connecting the controller to a single 8" Shugart/Quantum drive, a Shugart SA1200 Data Separator and three interconnecting cables are required (see Figure 2-10. One control cable and one NRZ read/write cable are required to interface the controller with the drive and data separator, respectively. A

separate MFM read/write cable is then required to transmit read/write information between the data separator and the drive.

When controlling multiple drives, Drive 0 (which is called the master and is equipped with the data separator) allows control and read/write data to be routed to and from up to three additional slave drives. The control cable for multiple drive configurations is daisy-chained from the master to the slave drives. Physically, the cable consists of a ribbon cable with an in-line connector for each drive. One MFM read/write cable is required from each slave drive to the master drive.

Memorex 101 and 102 or Shugart SA4000. The controller can drive one or two Memorex/14" Shugart drives. When connecting the controller to a single drive, both a control and a read/write cable are required. When controlling two drives, a single cable, such as the control cable described for the Shugart/Quantum drives, is required that daisy-chains the control information to both drives as shown in Figure 2-10. A split (bifurcated) cable is required to route NRZ read/write data to and from the two drives.

Pertec D8000 and Priam 570, 1070, 2050 and 3450. The connector on the Pertec and Priam drives transmit both control and read/write data. When connecting the controller to a single drive, a bifurcated (split) cable that combines the control lines and the read/write lines from the controller is requires as shown in Figure 2-10. When controlling multiple drives, a cable such as the control cable described for the Shugart drives is required that daisy-chains the control and read/write information between the four drives.

RMS 500. When connecting the controller to a single RMS drive, an RMS Data Separator and three interconnecting cables are required. See Figure 2-8 similar to Shugart SA1000 and Quantum Q2000 above.

Table 2-7. -5-Volt Selection

| Jumper | From | То | Function                                                                  |

|--------|------|----|---------------------------------------------------------------------------|

| W21    | 1    | 2  | Select -5 volts from Multibus™ connector                                  |

|        | 1    | 3  | Select -5 volts from regulator (requires jumper to be set on W20)         |

| W20    | 1    | 2  | Select -10 volts from Multibus™ connector as source for -5 Volt regulator |

|        | 1    | 3  | Select -12 volts from Multibus™ connector as source for -5 Volt regulator |

Figure 2-3. 8" Shugart/Quantum Drive Interconnecting Cable Requirements

Figure 2-3. 8" Shugart/Quantum Drive Interconnecting Cable Requirements (Continued)

36

#### Fujitsu 2300/Memorex/14" Shugart Drive Cable Wiring Diagram iSBC 215 Controller\* Memorex/14" Shugart Drive iSBC 215 Controller\* Memorex/14" Shugart Drive Connector J1 Mating Connector Connector J2 Mating Connector 50-Pin Drive 0 20-Pin ( 2

both radial connectors should be swapped: pin 15, +PLO Clock (RDCLO+); pin 16, -PLO Clock (RDCLO-).

Figure 2-4. Fujitsu 2300/Memorex/14" Shugart Drive Interconnecting Cable Requirements

Memorex/14" Shugart Drive 1

Scramble Wires at drive.

Memorex/14" Shugart Mating Connectors

Figure 2-4. Fujitsu 2300/Memorex/14" Shugart Drive Interconnecting Cable Requirements (Continued)

(3)

40-Conductor Ribbon Cable

Figure 2-5. Pertec Drive Interconnecting Cable Requirements (Continued)

Figure 2-6. Priam Drive Interconnecting Cable Requirements (Continued)

Figure 2-7. 51/4" RMS Drive Interconnecting Cable Requirements

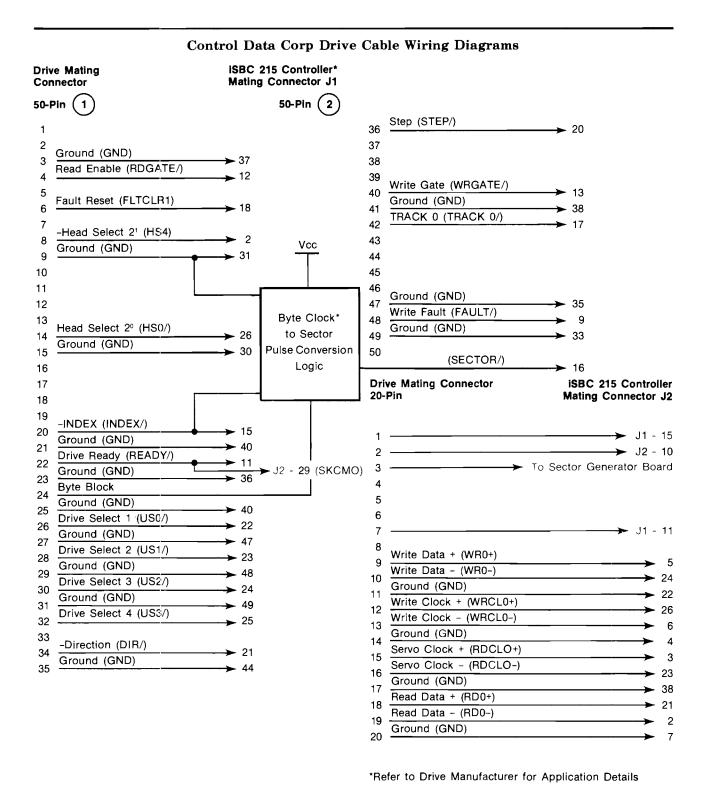

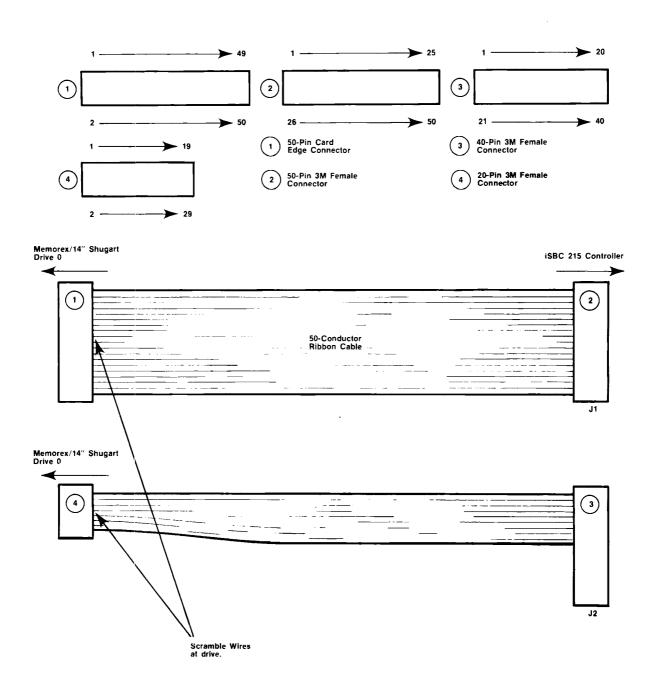

Figure 2-8. Control Data Corporation Drive Interconnecting Cable Requirements

Figure 2-9. Control Data Corporation Drive Interconnecting Cable Requirements

2-21

Table 2-8. J3 and J4 Pin Assignments

| Pin     | Mnemonic            | Description             | Pin     | Mnemonic         | Description                       |

|---------|---------------------|-------------------------|---------|------------------|-----------------------------------|

| 43      | MD8                 | MDATA Bit 8             | 44      | MD9              | MDATA Bit 9                       |

| 41      | MDA                 | MDATA Bit A             | 42      | MDB              | MDATA Bit B                       |

| 39      | MDC                 | MDATA Bit C             | 40      | MDD              | MDATA Bit D                       |

| 37      | MDE                 | MDATA Bit 3             | 38      | MDF              | MDATA Bit F                       |

| 35      | GND                 | Signal Ground           | 36      | +5V              | +5 Volts                          |

| 33      | MD0                 | MDATA Bit 0             | 34      | MDRQT            | M DMA Request                     |

| 31      | MD1                 | MDATA Bit 1             | 32      | MDACK/           | M DMA Acknowledge*                |

| 29      | MD2                 | MDATA Bit 2             | 30      | ОРТ0             | Option 0                          |

| 27      | MD3                 | MDATA Bit 3             | 28      | OPT1             | Option 1                          |

| 25      | MD4                 | MDATA Bit 4             | 26      | RDMA             | Terminate DMA                     |

| 23      | MD5                 | MDATA Bit 5             | 24      |                  | Reserved                          |

| 21      | MD6                 | MDATA Bit 6             | 22      | MCS0/            | M Chip Select 0                   |

| 19      | MD7                 | MDATA Bit 7             | 20      | MCS1/            | M Chip Select 1                   |

| 17      | CND                 | Signal Gnd              | 18      | +5V              | +5 Volts                          |

| 15      | IORD/               | I/O Read Cmd            | 16      | MWAIT/           | M Wait                            |

| 13      | IOWRT/              | I/O Write Cmd           | 14      | MINTR0           | M Interrupt 0                     |

| 11      | MA0                 | M Address 0             | 12      | MINTR1           | M Interrupt 1                     |

| 9       | MA1                 | M Address 1             | 10      |                  | Reserved                          |

| 7       | MA2                 | M Address 2             | 8       | MPST/            | iSBX Multimodule<br>Board Present |

| 5       | RESET               | Reset                   | 6       | MCLK             | M Clock                           |

| 3       | GND                 | Signal Gnd              | 4       | +5V              | +5 Volts                          |

| 1       | +12V                | +12 Volts               | 2       | -12V             | -12 Volts                         |

| All und | defined pins are re | eserved for future use. | *The is | SBC 215 does not | drive this signal.                |

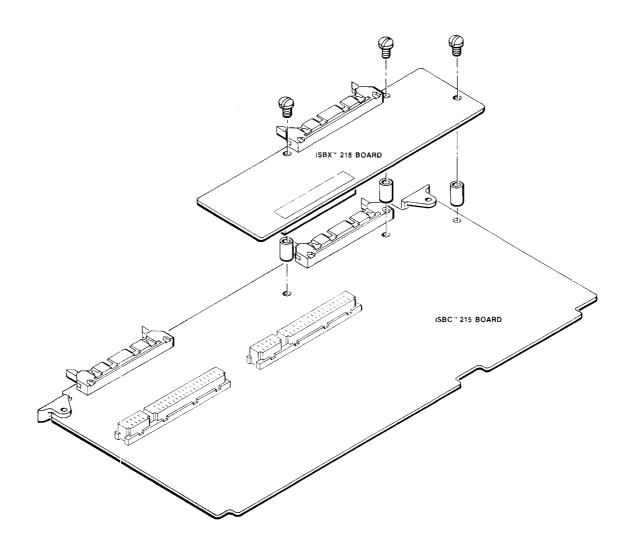

# 2-18. iSBX MULTIMODULE™ INTERFACE

Controller board connectors J3 and J4 have each been designed to interface with Intel iSBX I/O controllers or other I/O modules designed to meet the Intel iSBX Bus Specifications. The Intel iSBX 218 Flexible Disk Controller connects to the J4 connector and provides an interface between the iSBC 215 controller board and up to four 5¼" or 8" double density flexible (floppy) disk drives. The iSBX 218 controller interfaces directly with the iSBC 215 software as described in Chapter 3. Instructions for installing the iSBX 218 controller on iSBC 215 board are given in Paragraph 2-18.